Diferencia entre revisiones de «ICS (Configuración Reloj Interno) - MC9S08QE128»

(→Uso de los Registros del ICS) |

|||

| (No se muestran 18 ediciones intermedias de 5 usuarios) | |||

| Línea 1: | Línea 1: | ||

| − | + | <div style="top:+0.3em; text-align: center;font-size:100%; border:1px solid #C7D0F8; background:#F2F5FD;width:80%"> | |

| + | '''Este artículo está incompleto. Necesita trabajo adicional. Revisar la discusión.'''</div> | ||

| + | |||

| + | |||

| + | |||

A continuación se presenta una descripcion del Módulo de Clock Interno del [[MC9S08QE128]] | A continuación se presenta una descripcion del Módulo de Clock Interno del [[MC9S08QE128]] | ||

| − | [[Categoría: MC9S08QE128]] | + | [[Categoría: MC9S08QE128]]. |

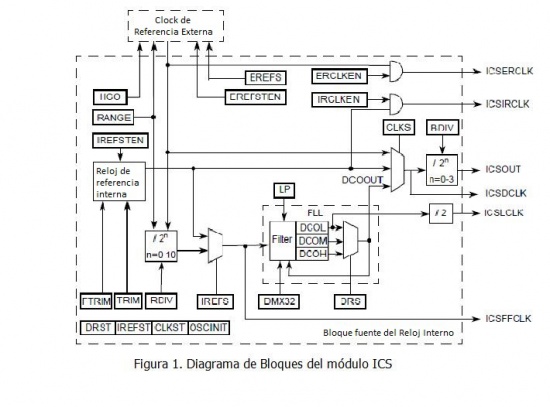

| − | [[Image: | + | [[Image:Diagrama de bloques ICS.jpg|550px|thumb|right|Diagrama de Bloques del Módulo ICS.]] |

==ICS (Configuración Reloj Interno) - MC9S08QE128== | ==ICS (Configuración Reloj Interno) - MC9S08QE128== | ||

'''¿Qué es el ICS?''' | '''¿Qué es el ICS?''' | ||

| − | El | + | El Módulo de reloj interno conocido como ''ICS'' por sus siglas en inglés (Internal Clock Source) es una fuente de reloj que usa el Microcontrolador ''MC9S08QE128'' de la familia HS08 el cual provee al sistema MCU (Microcontroller Unit) de una frecuencia de operación interna. |

| + | |||

'''¿Para que se utiliza?''' | '''¿Para que se utiliza?''' | ||

| − | La gran ventaja de este modulo es que permite regular la frecuencia del clock con el que trabaja el MCU. Esto es posible gracias a un circuito que contiene el modulo ICS llamado ''Frecuency-Locked Loop'' (FLL por su siglas en ingles) el cual permite generar frecuencias estables a partir de la reconversión | + | La gran ventaja de este modulo es que permite regular la frecuencia del clock con el que trabaja el MCU. Esto es posible gracias a un circuito que contiene el modulo ICS llamado ''Frecuency-Locked Loop'' (FLL por su siglas en ingles) el cual permite generar frecuencias estables a partir de la reconversión frecuencial de una fuente de clock referencial, bien sea interna o externa al Microcontrolador. |

| + | |||

| Línea 15: | Línea 21: | ||

El modulo ICS presenta las siguientes características: | El modulo ICS presenta las siguientes características: | ||

| − | #Un circuito de lazo de frecuencia de enganche o FLL (Frecuency-Locked loop) el cual es programable | + | #Un circuito de lazo de frecuencia de enganche o FLL (Frecuency-Locked loop) el cual es programable vía software para generar frecuencias. |

#El FLL puede ser controlado por una referencia de clock interna o externa. | #El FLL puede ser controlado por una referencia de clock interna o externa. | ||

| − | #En caso de usar | + | #En caso de usar Clock Externo el modulo proporciona un divisor de frecuencia que controla el rango del oscilador. |

#Al usar el clock interno como referencia se dispone de 9 bits programables para controlar el rango de frecuencia controlando el período del clock (TRIM). | #Al usar el clock interno como referencia se dispone de 9 bits programables para controlar el rango de frecuencia controlando el período del clock (TRIM). | ||

#Clock interno o externo puede ser seleccionado como fuente para el MCU. | #Clock interno o externo puede ser seleccionado como fuente para el MCU. | ||

| Línea 31: | Línea 37: | ||

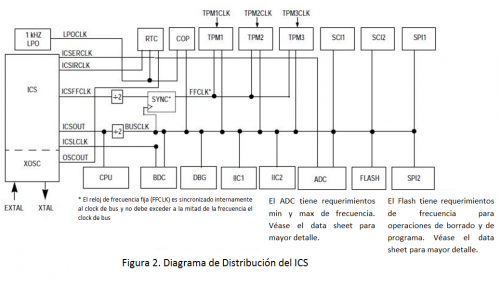

El conocimiento y manejo del módulo ICS es de vital importancia puesto que representa una fuente de clock controlable vital para el funcionamiento del MCU y de muchos módulos del microprocesador. en la figura 2 se aprecia que el ICS proporciona el clock del bus común a los módulos y ademas posee salidas especificas cuya frecuencia son totalmente programables. | El conocimiento y manejo del módulo ICS es de vital importancia puesto que representa una fuente de clock controlable vital para el funcionamiento del MCU y de muchos módulos del microprocesador. en la figura 2 se aprecia que el ICS proporciona el clock del bus común a los módulos y ademas posee salidas especificas cuya frecuencia son totalmente programables. | ||

| − | [[Image: | + | [[Image:Diagrama de Distribución del ICS.png|500px|thumb|right|Diagrama de Distribución del ICS.]] |

Entre los módulos que requieren de ICS se encuentran | Entre los módulos que requieren de ICS se encuentran | ||

| − | #Contador de Tiempo Real [[RTC (Real-timer counter) - MC9S08QE128|RTC]] | + | #Contador de Tiempo Real. [[RTC (Real-timer counter) - MC9S08QE128|RTC]] |

| − | #Conversor Analógico Digital [[ADC (Conversor Analógico-Digital) - MC9S08QE128|ADC]] | + | #Conversor Analógico Digital.[[ADC (Conversor Analógico-Digital) - MC9S08QE128|ADC]] |

| − | #Interfaz de Comunicación Serial [[SCI (Interfaz de Comunicación Serial) - MC9S08QE128|SCI]] | + | #Interfaz de Comunicación Serial. [[SCI (Interfaz de Comunicación Serial) - MC9S08QE128|SCI]] |

| − | #Interfaz de Comunicación Serial Periférica [[ SPI: Interfaz de Serial Periferico para el microcontrolador QE - MC9S08QE128|SPI]] | + | #Interfaz de Comunicación Serial Periférica. [[ SPI: Interfaz de Serial Periferico para el microcontrolador QE - MC9S08QE128|SPI]] |

| − | #Circuito Inter-Integrado [[ I²C (Inter-Integrated Circuit) - MC9S08QE128|IIC]] | + | #Circuito Inter-Integrado. [[ I²C (Inter-Integrated Circuit) - MC9S08QE128|IIC]] |

| − | #Temporizador de operacion del computador COP | + | #Temporizador de operacion del computador COP. |

#Debug Backgraound DBM. Ver [[ Modos de operación del MC9S08QE128 | Modos de Operación]] para mayor información. | #Debug Backgraound DBM. Ver [[ Modos de operación del MC9S08QE128 | Modos de Operación]] para mayor información. | ||

| − | #Background Debug Controller BDC | + | #Background Debug Controller BDC. |

| − | #Modulador de Ancho de Pulso [http://wikitronica.labc.usb.ve/index.php/PWM_(Modulaci%C3%B3n_de_Ancho_de_Pulso) PWM] | + | #Modulador de Ancho de Pulso. |

| + | [http://wikitronica.labc.usb.ve/index.php/PWM_(Modulaci%C3%B3n_de_Ancho_de_Pulso) PWM] | ||

==Registros del Módulo ICS== | ==Registros del Módulo ICS== | ||

| Línea 65: | Línea 72: | ||

1.'''CLKS'''(Clock Source Select): está compuesto por dos bits (7:6) cuya combinación codifica la selección del clock que controla el bus de frecuencia, es decir el clock de salida para el MCU . La frecuencia de este bus depende del valor en BDIV bits (será explicado mas adelante) | 1.'''CLKS'''(Clock Source Select): está compuesto por dos bits (7:6) cuya combinación codifica la selección del clock que controla el bus de frecuencia, es decir el clock de salida para el MCU . La frecuencia de este bus depende del valor en BDIV bits (será explicado mas adelante) | ||

| − | 00 Selecciona como clock la salida del circuito FLL | + | 00 Selecciona como clock la salida del circuito FLL. |

| − | 01 Selecciona el clock interno como referencia | + | 01 Selecciona el clock interno como referencia. |

| − | 10 Selecciona el clock externo como referencia | + | 10 Selecciona el clock externo como referencia. |

11 Reservado, no se utiliza. | 11 Reservado, no se utiliza. | ||

<br> | <br> | ||

| Línea 107: | Línea 114: | ||

|align="center"|6 | |align="center"|6 | ||

|align="center"|64 | |align="center"|64 | ||

| − | |align="center"|Reservado | + | |align="center"|Reservado. |

|- | |- | ||

|align="center"|7 | |align="center"|7 | ||

|align="center"|128 | |align="center"|128 | ||

| − | |align="center"|Reservado | + | |align="center"|Reservado. |

|} | |} | ||

| Línea 123: | Línea 130: | ||

!'''1''' | !'''1''' | ||

|- | |- | ||

| − | |align="center"|Clock Externo seleccionado como referencia para el FLL | + | |align="center"|Clock Externo seleccionado como referencia para el FLL. |

| − | |align="center"|Clock Interno seleccionado como referencia para el FLL | + | |align="center"|Clock Interno seleccionado como referencia para el FLL. |

|}<br> | |}<br> | ||

| − | 4.'''IRCLKEN'''(Internal Reference Clock Enable) :está compuesto por 1 bits y se encarga de habilitar el clock interno para ser usado como ICSIRCLK (ver diagrama de bloques Figura | + | 4.'''IRCLKEN'''(Internal Reference Clock Enable) :está compuesto por 1 bits y se encarga de habilitar el clock interno para ser usado como ICSIRCLK (ver diagrama de bloques Figura 1). Es decir, el clock interno es tomado como salida del módulo ICS sin hacerle ninguna modificación |

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | ||

|- valign="bottom" style="background:#FFFFFF" ; | |- valign="bottom" style="background:#FFFFFF" ; | ||

| Línea 136: | Línea 143: | ||

!'''1''' | !'''1''' | ||

|- | |- | ||

| − | |align="center"|ICSIRCLK desactivado | + | |align="center"|ICSIRCLK desactivado. |

| − | |align="center"|ICSIRCLK activado | + | |align="center"|ICSIRCLK activado. |

|} | |} | ||

<br> | <br> | ||

| Línea 148: | Línea 155: | ||

|- | |- | ||

|align="center"|El clock interno es deshabilitado en el modo de stop. | |align="center"|El clock interno es deshabilitado en el modo de stop. | ||

| − | |align="center"|El clock de referencia interno permanece habilitado una vez entrado al modo de stop si el bits de IRCLKEN está en | + | |align="center"|El clock de referencia interno permanece habilitado una vez entrado al modo de stop si el bits de IRCLKEN está en uno lógico antes de entrar en dicho módulo. |

|} | |} | ||

| Línea 158: | Línea 165: | ||

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | ||

|- valign="bottom" style="background:#F9F9F9" | |- valign="bottom" style="background:#F9F9F9" | ||

| − | !BDIV (bits 7:6) | + | !BDIV (bits 7:6). |

| − | !RANGE (5) | + | !RANGE (5). |

| − | !HGO (4) | + | !HGO (4). |

| − | !LP (3) | + | !LP (3). |

| − | !EREFS(2) | + | !EREFS(2). |

| − | !ERCLKEN(1) | + | !ERCLKEN(1). |

| − | !EREFSTEN (0) | + | !EREFSTEN (0). |

|} | |} | ||

<br> | <br> | ||

| Línea 178: | Línea 185: | ||

!'''11''' | !'''11''' | ||

|- | |- | ||

| − | |align="center"| | + | |align="center"|Divide la frecuencia del clock escogido como salida por 1. |

| − | |align="center"| | + | |align="center"|Divide la frecuencia del clock por 2 (modo escogido después de un reset.) |

| − | |align="center"| | + | |align="center"|Divide la frecuencia del clock por 4. |

| − | |align="center"| | + | |align="center"|Divide la frecuencia del clock por 8. |

|} | |} | ||

<br> | <br> | ||

| Línea 226: | Línea 233: | ||

|- | |- | ||

|align="center"|Clock Externo requerido como fuente. | |align="center"|Clock Externo requerido como fuente. | ||

| − | |align="center"|Oscilador requerido como fuente | + | |align="center"|Oscilador requerido como fuente. |

| + | |||

| + | |||

|} | |} | ||

<br> | <br> | ||

| Línea 236: | Línea 245: | ||

!'''1''' | !'''1''' | ||

|- | |- | ||

| − | |align="center"|ICSERCLK desactivado | + | |align="center"|ICSERCLK desactivado. |

| − | |align="center"|ICSERCLK activado | + | |align="center"|ICSERCLK activado. |

|} | |} | ||

<br> | <br> | ||

| Línea 247: | Línea 256: | ||

!'''1''' | !'''1''' | ||

|- | |- | ||

| − | |align="center"|El clock | + | |align="center"|El clock externo es deshabilitado en el modo de stop. |

|align="center"|El clock de referencia externo permanece habilitado una vez entrado al modo de stop si el bits de ERCLKEN está en uno lógico antes de entrar en dicho modo de operación. | |align="center"|El clock de referencia externo permanece habilitado una vez entrado al modo de stop si el bits de ERCLKEN está en uno lógico antes de entrar en dicho modo de operación. | ||

|} | |} | ||

| Línea 268: | Línea 277: | ||

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | ||

|- valign="bottom" style="background:#F9F9F9" | |- valign="bottom" style="background:#F9F9F9" | ||

| − | !DRST(lectrua) / DRS(escritura) (bits 7:6) | + | !DRST(lectrua) / DRS(escritura) (bits 7:6). |

| − | !DMX (5) | + | !DMX (5). |

| − | !IREFST(4) | + | !IREFST(4). |

| − | !CLKST (3:2) | + | !CLKST (3:2). |

| − | !OSCINIT(1) | + | !OSCINIT(1). |

| − | !FTRIM(0) | + | !FTRIM(0). |

|} | |} | ||

<br> | <br> | ||

| Línea 286: | Línea 295: | ||

!'''11''' | !'''11''' | ||

|- | |- | ||

| − | |align="center"|Baja frecuencia (Low Range) | + | |align="center"|Baja frecuencia (Low Range). |

| − | |align="center"|Frecuencias Medias (Mide Range) | + | |align="center"|Frecuencias Medias (Mide Range). |

| − | |align="center"|Alta frecuencia (High Range) | + | |align="center"|Alta frecuencia (High Range). |

| − | |align="center"|Reservado | + | |align="center"|Reservado. |

|}<br> | |}<br> | ||

| − | '''¡ATENCION!''' La escritura de | + | '''¡ATENCION!''' La escritura de 11 en DRS es ignorada y DRST permanece en la configuración actual. Este espacio es reservado. |

'''¡ATENCION!''' Escribir en DRS mientras el bit de baja potencia (LP) en ICSC2 esta activo no produce ningún resultado, ¡es ignorado por el CPU! | '''¡ATENCION!''' Escribir en DRS mientras el bit de baja potencia (LP) en ICSC2 esta activo no produce ningún resultado, ¡es ignorado por el CPU! | ||

<br><br> | <br><br> | ||

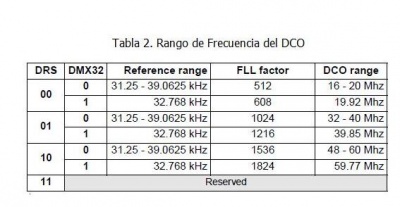

| − | 2.'''DMX32''' (DCO Maximun Frecuency with 32.768Khz reference): este bit de control decide si el rango de frecuencia del DCO es aproximado a su máxima frecuencia con un clock de referencia de 32.768Khz (clock interno).En otras palabras el factor del FLL es máximo y la frecuencia es mayor y muy aproximado a la frecuencia máxima de la configuración. (Ver tabla 2) | + | 2.'''DMX32''' (DCO Maximun Frecuency with 32.768Khz reference): este bit de control decide si el rango de frecuencia del DCO es aproximado a su máxima frecuencia con un clock de referencia de 32.768Khz (clock interno).En otras palabras el factor del FLL es máximo y la frecuencia es mayor y muy aproximado a la frecuencia máxima de la configuración. (Ver tabla 2). |

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | ||

| Línea 303: | Línea 312: | ||

|- | |- | ||

|align="center"|El DCO trabaja en un rango del 25% de la frecuencia de referencia. | |align="center"|El DCO trabaja en un rango del 25% de la frecuencia de referencia. | ||

| − | |align="center"| | + | |align="center"|El DCO es conducido a su máxima frecuencia cuando el clock de referencia es de 32.768Khz. |

|} | |} | ||

En la Siguiente Tabla se muestra la combinación de los bits de DRS y DXM32 y las frecuencias que ellas generan: | En la Siguiente Tabla se muestra la combinación de los bits de DRS y DXM32 y las frecuencias que ellas generan: | ||

| − | [[Image: | + | [[Image:Rango de frecuencia del DCO.jpg|400px|thumb|center|Rango de Frecuencia del DCO.]] |

<br> | <br> | ||

'''¡CUIDADO!''' La frecuencia del clock del Bus que conecta otros módulos no debería exceder el máximo valor de frecuencia permitido por el dispositivo. | '''¡CUIDADO!''' La frecuencia del clock del Bus que conecta otros módulos no debería exceder el máximo valor de frecuencia permitido por el dispositivo. | ||

| Línea 318: | Línea 327: | ||

!'''1''' | !'''1''' | ||

|- | |- | ||

| − | |align="center"|La fuente usada como referencia para el circuito FLL es un Clock Externo | + | |align="center"| La fuente usada como referencia para el circuito FLL es un Clock Externo. |

| − | |align="center"| La fuente usada como referencia es un Clock Interno | + | |align="center"| La fuente usada como referencia es un Clock Interno. |

|} | |} | ||

<br> | <br> | ||

| Línea 331: | Línea 340: | ||

!'''11''' | !'''11''' | ||

|- | |- | ||

| − | |align="center"|La salida del FLL está seleccionada como fuente de clock | + | |align="center"|La salida del FLL está seleccionada como fuente de clock. |

| − | |align="center"| | + | |align="center"| El FLL no está siendo usado (Bypassed), el Clock interno de referencia es usado como fuente de clock. |

| − | |align="center"| | + | |align="center"| El FLL no está siendo usado (Bypassed), el Clock externo de referencia es usado como fuente de clock. |

| − | |align="center"|Reservado | + | |align="center"|Reservado. |

|}<br> | |}<br> | ||

5.'''OSCINIT''' (OSC Initialization): Si el clock externo es seleccionado por el campo ERCLKEN en el registro ICSC2 o se trabaja en el modo FEE,FBE o FBLEP (ver más adelante), y además el bit EREFS está en uno lógico, entonces el OSCINIT se pone en uno lógico después que la inicialización del clock externo es completado. | 5.'''OSCINIT''' (OSC Initialization): Si el clock externo es seleccionado por el campo ERCLKEN en el registro ICSC2 o se trabaja en el modo FEE,FBE o FBLEP (ver más adelante), y además el bit EREFS está en uno lógico, entonces el OSCINIT se pone en uno lógico después que la inicialización del clock externo es completado. | ||

| Línea 349: | Línea 358: | ||

*Usemos el registro '''ICSC1'''para: | *Usemos el registro '''ICSC1'''para: | ||

| − | #Escoger la fuente que generará el clock deseado (FLL, Clock Interno(IC) o Clock Externo(EC)) | + | #Escoger la fuente que generará el clock deseado (FLL, Clock Interno(IC) o Clock Externo(EC)). |

| − | #En caso de usar el FLL escoger la referencia que usará este circuito (Clock Interno o Externo) | + | #En caso de usar el FLL escoger la referencia que usará este circuito (Clock Interno o Externo). |

| − | #Habilitar o no la salida ICSIRCLK que es fuente del módulo RTC | + | #Habilitar o no la salida ICSIRCLK que es fuente del módulo RTC. |

#Habilitar o no el clock interno en caso de actuar en el modo de Stop. | #Habilitar o no el clock interno en caso de actuar en el modo de Stop. | ||

#Seleccionar el factor divisor de frecuencia en caso de usar el clock externo. | #Seleccionar el factor divisor de frecuencia en caso de usar el clock externo. | ||

*Usemos el registro '''ICSC2''' para: | *Usemos el registro '''ICSC2''' para: | ||

| − | #Escoger el factor de division de frecuencia que se le aplicará a la salida de nuestra fuente de clock (FLL,IC,EC) | + | #Escoger el factor de division de frecuencia que se le aplicará a la salida de nuestra fuente de clock (FLL,IC,EC). |

| − | #Seleccionar si trabajaremos en Alta o Baja frecuencia | + | #Seleccionar si trabajaremos en Alta o Baja frecuencia. |

| − | #Configurar el oscilador para trabajar con alta ganancia o baja potencia | + | #Configurar el oscilador para trabajar con alta ganancia o baja potencia. |

| − | #Habilitar o no el FLL en caso de trabajar en los modos del tipo Bypass FLL | + | #Habilitar o no el FLL en caso de trabajar en los modos del tipo Bypass FLL. |

| − | #Habilitar o no el ICSERCLK que es salida del clock externo que sirve de fuente al módulo ADC | + | #Habilitar o no el ICSERCLK que es salida del clock externo que sirve de fuente al módulo ADC. |

#Habilitar o no el clock externo en caso de actuar en el modo de Stop. | #Habilitar o no el clock externo en caso de actuar en el modo de Stop. | ||

| Línea 366: | Línea 375: | ||

*Usemos el Registro '''ICSSC''' para verificar estatus de funcionamiento, tales como: | *Usemos el Registro '''ICSSC''' para verificar estatus de funcionamiento, tales como: | ||

| − | #Chequear en que rango de frecuencia se trabaja (Baja, Media o Alta) | + | #Chequear en que rango de frecuencia se trabaja (Baja, Media o Alta). |

| − | #Chequear que tipo de referencia se está usando (Clock interno o Externo) | + | #Chequear que tipo de referencia se está usando (Clock interno o Externo). |

| − | #Chequear en que modo de trabajo se encuentra el clock (FLL, SóloClock Interno, Sólo Clock Externo) | + | #Chequear en que modo de trabajo se encuentra el clock (FLL, SóloClock Interno, Sólo Clock Externo). |

#Chequear si el clock externo fue inicializado correctamente en caso de usarlo. | #Chequear si el clock externo fue inicializado correctamente en caso de usarlo. | ||

También se puede usar para configurar lo siguiente: | También se puede usar para configurar lo siguiente: | ||

| − | #Los cambios mas pequeños en la variación del período del Clock interno mediante el FTRIM | + | #Los cambios mas pequeños en la variación del período del Clock interno mediante el FTRIM. |

| − | #El tipo de rango de frecuencia que tendrá el DCO del circuito FLL (Baja, Media o Alta) | + | #El tipo de rango de frecuencia que tendrá el DCO del circuito FLL (Baja, Media o Alta). |

*'''IMPORTANTE:'''Existen dos Registros que permiten controlar la habilitación del busclock hacia todos los módulos que lo requieren. Ellos son los registro de compuertas de control de sistema de reloj '''SCGC1''' y '''SCGC2''' por sus siglas en inglés (System Clock Gating Control). | *'''IMPORTANTE:'''Existen dos Registros que permiten controlar la habilitación del busclock hacia todos los módulos que lo requieren. Ellos son los registro de compuertas de control de sistema de reloj '''SCGC1''' y '''SCGC2''' por sus siglas en inglés (System Clock Gating Control). | ||

*Usemos el registro '''SCGC1''' para habilitar el busclock de los siguientes módulos: | *Usemos el registro '''SCGC1''' para habilitar el busclock de los siguientes módulos: | ||

| − | #Temporizador para modulación de ancho de pulso (TPM1, TPM2 y TPM3) | + | #Temporizador para modulación de ancho de pulso (TPM1, TPM2 y TPM3). |

| − | #Conversor Analógico Digtal (ADC) | + | #Conversor Analógico Digtal (ADC). |

| − | #Cirucuito Inter-Integrado (IIC1 e IIC2) | + | #Cirucuito Inter-Integrado (IIC1 e IIC2). |

| − | #Interfaz de comunicación serial (SCI1 y SCI2) | + | #Interfaz de comunicación serial (SCI1 y SCI2). |

Diagrama del Registro SCGC1 (8 bits): | Diagrama del Registro SCGC1 (8 bits): | ||

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | ||

|- valign="bottom" style="background:#F9F9F9" | |- valign="bottom" style="background:#F9F9F9" | ||

| − | !TPM3 (bit 7) | + | !TPM3 (bit 7). |

| − | !TPM2 (6) | + | !TPM2 (6). |

| − | !TPM1 (5) | + | !TPM1 (5). |

| − | !ADC (4) | + | !ADC (4). |

| − | !IIC2(3) | + | !IIC2(3). |

| − | !IIC1(2) | + | !IIC1(2). |

| − | !SCI2 (1) | + | !SCI2 (1). |

| − | !SCI1 (0) | + | !SCI1 (0). |

|} | |} | ||

| Línea 399: | Línea 408: | ||

*Usemos el registro '''SCGC2''' para habilitar el busclock de los siguientes módulos: | *Usemos el registro '''SCGC2''' para habilitar el busclock de los siguientes módulos: | ||

#Depurador de Programa [http://wikitronica.labc.usb.ve/index.php/Debug_Module_(DBG)(128k)-_MC9S08QE128#Modos_de_Operaci.C3.B3n: DBG] | #Depurador de Programa [http://wikitronica.labc.usb.ve/index.php/Debug_Module_(DBG)(128k)-_MC9S08QE128#Modos_de_Operaci.C3.B3n: DBG] | ||

| − | #Registros de memoria Flash (FLS) | + | #Registros de memoria Flash (FLS). |

| − | #Interrupciones Externas [http://wikitronica.labc.usb.ve/index.php/Interrupciones#IRQ: IRQ] | + | #Interrupciones Externas. [http://wikitronica.labc.usb.ve/index.php/Interrupciones#IRQ: IRQ] |

| − | #Interrupciones por Teclado [http://wikitronica.labc.usb.ve/index.php/KBI_(Keyboard_interrupts)_-_MC9S08QE128: KBI] | + | #Interrupciones por Teclado. |

| − | #Comparador Analógico [http://wikitronica.labc.usb.ve/index.php/Comparador_Analógico_-_MC9S08QE128: ACMP] | + | |

| − | #Contador de tiempo real [http://wikitronica.labc.usb.ve/index.php/RTC_(Real-timer_counter)_-_MC9S08QE128#Configuraci.C3.B3n_en_el_MC9S08QE128: RTC] | + | [http://wikitronica.labc.usb.ve/index.php/KBI_(Keyboard_interrupts)_-_MC9S08QE128#M.C3.B3dulo_de_interrupciones_por_teclado_MC9S08QE128: KBI] |

| − | #Interfaz de comunicación serial periférica [http://wikitronica.labc.usb.ve/index.php/SPI:_Interfaz_de_Serial_Periferico_para_el_microcontrolador_QE_-_MC9S08QE128#Formatos_del_Reloj_de_la_SPI: SPI1 y SPI2] | + | #Comparador Analógico. |

| + | |||

| + | [http://wikitronica.labc.usb.ve/index.php/Comparador_Analógico_-_MC9S08QE128#Registro_de_Control_y_Estado_.28ACMPxSC.29: ACMP] | ||

| + | #Contador de tiempo real. | ||

| + | |||

| + | [http://wikitronica.labc.usb.ve/index.php/RTC_(Real-timer_counter)_-_MC9S08QE128#Configuraci.C3.B3n_en_el_MC9S08QE128: RTC] | ||

| + | #Interfaz de comunicación serial periférica. | ||

| + | |||

| + | [http://wikitronica.labc.usb.ve/index.php/SPI:_Interfaz_de_Serial_Periferico_para_el_microcontrolador_QE_-_MC9S08QE128#Formatos_del_Reloj_de_la_SPI: SPI1 y SPI2] | ||

Diagrama del Registro SCGC2 (8 bits): | Diagrama del Registro SCGC2 (8 bits): | ||

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="6" | ||

|- valign="bottom" style="background:#F9F9F9" | |- valign="bottom" style="background:#F9F9F9" | ||

| − | !DBG (bit 7) | + | !DBG (bit 7). |

| − | !FLS (6) | + | !FLS (6). |

| − | !IRQ (5) | + | !IRQ (5). |

| − | !KBI (4) | + | !KBI (4). |

| − | !ACMP(3) | + | !ACMP(3). |

| − | !RTC(2) | + | !RTC(2). |

| − | !SPI2 (1) | + | !SPI2 (1). |

| − | !SPI1 (0) | + | !SPI1 (0). |

|} | |} | ||

| Línea 441: | Línea 458: | ||

'''¿Cuando sucede esto?''' | '''¿Cuando sucede esto?''' | ||

| − | *Los bits de '''CLKS''' (ICSC1)deben estar en 00 | + | *Los bits de '''CLKS''' (ICSC1)deben estar en 00. |

| − | *El bit '''IREFS''' debe ser 0 lógico | + | *El bit '''IREFS''' debe ser 0 lógico. |

| − | *Los bits de RDIV deben indicar el factor de división del FLL tal que la frecuencia queden en el rango 31.25-39.0625 Khz | + | *Los bits de RDIV deben indicar el factor de división del FLL tal que la frecuencia queden en el rango 31.25-39.0625 Khz. |

===FLL Bypassed Internal (FBI)=== | ===FLL Bypassed Internal (FBI)=== | ||

| Línea 450: | Línea 467: | ||

'''¿Cuando sucede esto?''' | '''¿Cuando sucede esto?''' | ||

| − | *Los bits de '''CLKS''' (ICSC1)deben estar en 01 | + | *Los bits de '''CLKS''' (ICSC1)deben estar en 01 . |

| − | *El bit '''IREFS''' debe ser 1 lógico | + | *El bit '''IREFS''' debe ser 1 lógico. |

| − | *El modo BDM (Backgroun Debug Mode) debe estar activo o el bit '''LP'''en '''ICSC2''' debe ser 0 | + | *El modo BDM (Backgroun Debug Mode) debe estar activo o el bit '''LP'''en '''ICSC2''' debe ser 0. |

===FLL Bypassed Internal Low Power (FBILP)=== | ===FLL Bypassed Internal Low Power (FBILP)=== | ||

| Línea 468: | Línea 485: | ||

'''¿Cuando sucede esto?''' | '''¿Cuando sucede esto?''' | ||

| − | *Los bits de '''CLKS''' (ICSC1)deben estar en 10 | + | *Los bits de '''CLKS''' (ICSC1)deben estar en 10. |

| − | *El bit '''IREFS''' debe ser 0 lógico | + | *El bit '''IREFS''' debe ser 0 lógico. |

| − | *El modo BDM (Backgroun Debug Mode) debe estar activo o el bit '''LP'''en '''ICSC2''' debe ser 0 | + | *El modo BDM (Backgroun Debug Mode) debe estar activo o el bit '''LP'''en '''ICSC2''' debe ser 0. |

| − | *Los bits de RDIV deben indicar el factor de división del FLL tal que la frecuencia queden en el rango 31.25-39.0625 Khz | + | *Los bits de RDIV deben indicar el factor de división del FLL tal que la frecuencia queden en el rango 31.25-39.0625 Khz. |

=== FLL Bypassed External Low Power (FBELP)=== | === FLL Bypassed External Low Power (FBELP)=== | ||

| Línea 478: | Línea 495: | ||

'''¿Cuando sucede esto?''' | '''¿Cuando sucede esto?''' | ||

| − | *Los bits de '''CLKS''' (ICSC1)deben estar en 10 | + | *Los bits de '''CLKS''' (ICSC1)deben estar en 10. |

| − | *El bit '''IREFS''' debe ser 0 lógico | + | *El bit '''IREFS''' debe ser 0 lógico. |

| − | *El modo BDM (Backgroun Debug Mode) debe estar inactivo o el bit '''LP'''en '''ICSC2''' debe ser 1 | + | *El modo BDM (Backgroun Debug Mode) debe estar inactivo o el bit '''LP'''en '''ICSC2''' debe ser 1. |

===STOP=== | ===STOP=== | ||

| Línea 497: | Línea 514: | ||

===Cambios entre Modos de Operación === | ===Cambios entre Modos de Operación === | ||

| − | *El bit IREF puede ser cambiado en cualquier momento pero el cambio no será mostrado inmediatamente por el bit IREFST del registro ICSSC | + | *El bit IREF puede ser cambiado en cualquier momento pero el cambio no será mostrado inmediatamente por el bit IREFST del registro ICSSC. |

* Cuando se pasa del modo FEI al modo FEE, la salida del modulo se enganchará a la nueva frecuencia y clock de referencia cuando el cambio sea completado correctamente. | * Cuando se pasa del modo FEI al modo FEE, la salida del modulo se enganchará a la nueva frecuencia y clock de referencia cuando el cambio sea completado correctamente. | ||

| − | *El bit CLKS puede ser cambiado en cualquier momento pero el cambio no será mostrado inmediatamente por el bit CLKST del registro ICSSC | + | *El bit CLKS puede ser cambiado en cualquier momento pero el cambio no será mostrado inmediatamente por el bit CLKST del registro ICSSC. |

*El bit DRS puede ser cambiado en cualquier momento excepto cuando el bit LP está en 1. Si DRS es cambiado mientras se trabaja en modo FEI o FEE el clock del bus permanece en el rango de frecuencia anterior hasta que se inicialice el nuevo DCO. Después que cambie el DCO el FLL permanecerá desenganchado de la frecuencia seleccionada por algunos ciclos. Cuando el cambio es completado totalmente, los bits del DRST se actualizan. | *El bit DRS puede ser cambiado en cualquier momento excepto cuando el bit LP está en 1. Si DRS es cambiado mientras se trabaja en modo FEI o FEE el clock del bus permanece en el rango de frecuencia anterior hasta que se inicialice el nuevo DCO. Después que cambie el DCO el FLL permanecerá desenganchado de la frecuencia seleccionada por algunos ciclos. Cuando el cambio es completado totalmente, los bits del DRST se actualizan. | ||

| Línea 507: | Línea 524: | ||

===Uso del bit de Baja Potencia (LP) en el registro ICSC2=== | ===Uso del bit de Baja Potencia (LP) en el registro ICSC2=== | ||

| + | |||

| + | |||

*Este bit es usado para permitir al circuito FLL estar deshabilitado y conservar potencia cuando no está siendo usado. | *Este bit es usado para permitir al circuito FLL estar deshabilitado y conservar potencia cuando no está siendo usado. | ||

*Los bits DRS no pueden ser cambiados mientras LP esté en 1. | *Los bits DRS no pueden ser cambiados mientras LP esté en 1. | ||

| − | *En los casos en los que se desee mantener el FLL activo aunque no se use por momentos ( | + | *En los casos en los que se desee mantener el FLL activo aunque no se use por momentos (Modo Bypass) se deberá colocar el bt LP en 0. |

=== Máxima Frecuencia del DCO con un oscilador de 32.768Khz=== | === Máxima Frecuencia del DCO con un oscilador de 32.768Khz=== | ||

| − | + | ||

| + | FLL puede ser programado de tal forma que la frecuencia en el bus sea máxima a partir de un Oscilado común de 32.768 Khz. | ||

=== Clock Interno de Referencia=== | === Clock Interno de Referencia=== | ||

| + | |||

* Cuando el bit IRCLKEN está en 1 el modulo arrojará una una fuente de clock adicional llamada ICSIRCLK. la frecuencia de esta señal puede ser modificada cambiando el período clock interno con los valores cargados en el registro ICSTRM (Trimming). cargar un valor pequeño en ICSTRM disminuye el periodo y por lo tanto aumenta frecuencia. Incrementar el valor del ICSTRM aumenta período ergo disminuye frecuencia. | * Cuando el bit IRCLKEN está en 1 el modulo arrojará una una fuente de clock adicional llamada ICSIRCLK. la frecuencia de esta señal puede ser modificada cambiando el período clock interno con los valores cargados en el registro ICSTRM (Trimming). cargar un valor pequeño en ICSTRM disminuye el periodo y por lo tanto aumenta frecuencia. Incrementar el valor del ICSTRM aumenta período ergo disminuye frecuencia. | ||

| Línea 521: | Línea 542: | ||

* Si el usuario desea mayor precisión en la frecuencia del clock interno deberá variar el bit FTRIM en el registro ICSC2. | * Si el usuario desea mayor precisión en la frecuencia del clock interno deberá variar el bit FTRIM en el registro ICSC2. | ||

* Hay que tener cuidado cuando se programa el RDIV en el rango de baja frecuencia puesto que puede resultar que en la salida del módulo aparezcan frecuencias que excedan el máximo nivel que soporta el Chip. | * Hay que tener cuidado cuando se programa el RDIV en el rango de baja frecuencia puesto que puede resultar que en la salida del módulo aparezcan frecuencias que excedan el máximo nivel que soporta el Chip. | ||

| + | |||

===Clock Externo de Referencia=== | ===Clock Externo de Referencia=== | ||

| − | *El | + | |

| + | |||

| + | *El Módulo ICS soporta un clock externo de referencia con frecuencias entre 31.25Khz-40Mhz en todos los modos d operación. | ||

*Cuando el bit ERCLKEN está en 1 el modulo arrojará una una fuente de clock adicional llamada ICSERCLK. | *Cuando el bit ERCLKEN está en 1 el modulo arrojará una una fuente de clock adicional llamada ICSERCLK. | ||

*Cuando el bit IREFS es 1 el clock externo no es usado por el FLL. En este caso el clock externo arrojará una salida unicamente del tipo ICSERCLK. | *Cuando el bit IREFS es 1 el clock externo no es usado por el FLL. En este caso el clock externo arrojará una salida unicamente del tipo ICSERCLK. | ||

| Línea 529: | Línea 553: | ||

===Clock de Frecuencia Aproximada=== | ===Clock de Frecuencia Aproximada=== | ||

| + | |||

El módulo ICS presenta un clock adicional de referencia llamado ICSFFCLK (Ver figura 1). La frecuencia de este clock no deberia ser mayor a 1/4 de la salida ICSOUT para ser válido. | El módulo ICS presenta un clock adicional de referencia llamado ICSFFCLK (Ver figura 1). La frecuencia de este clock no deberia ser mayor a 1/4 de la salida ICSOUT para ser válido. | ||

| + | |||

===Clock Local=== | ===Clock Local=== | ||

El módulo ICS posee un clock como salida del DCO de baja frecuencia (Low Range) llamado ICSLCLK el cual es usado como clock para el BDC. este clock no está habilitado para los modo de FBILP y FBELP. | El módulo ICS posee un clock como salida del DCO de baja frecuencia (Low Range) llamado ICSLCLK el cual es usado como clock para el BDC. este clock no está habilitado para los modo de FBILP y FBELP. | ||

| − | ==Programando el Módulo en Lenguaje C== | + | ==Programación del Módulo ICS== |

| + | ===Programando el Módulo en Lenguaje C=== | ||

<syntaxhighlight lang="c"> | <syntaxhighlight lang="c"> | ||

#include "derivative.h" | #include "derivative.h" | ||

| − | //Ejemplo 1: | + | //Ejemplo 7.1.1: Configurando un clock con referencia de clock interna para el RTC |

ICSC1= 0x46 // la salida ICSICLK esta activo con referencia interna del Clock | ICSC1= 0x46 // la salida ICSICLK esta activo con referencia interna del Clock | ||

| − | // En caso de que el MCU caiga en | + | // En caso de que el MCU caiga en Modo Stop se deshabilita el clock interno de referencia. |

| − | // | + | //El Módulo FLL usa como fuente el clock interno aunque no es usado por el MCU. |

| − | ICSC2=0x88 // | + | ICSC2=0x88 // La frecuencia será el clock interno dividido por 4. |

| − | //Se configura el clock externo para trabajar en baja frecuencia y baja potencia aunque en realidad no es usado por ICS | + | //Se configura el clock externo para trabajar en baja frecuencia y baja potencia aunque en realidad no es usado por ICS. |

| − | // | + | //La Fuente de Clock ICSERCLK usado por el ADC esta inactivo. |

| − | // | + | //El clock externo en caso de usarse queda deshabilitado si el MCU entre en Modo Stop. |

| − | ICSTRM=0x00 // | + | ICSTRM=0x00 // No se modificará el período de clock interno para variar su frecuencia. |

| + | |||

| + | |||

| + | // Ejemplo 7.1.2: Configurando el ICS para trabajar con un clock del FLL en el modo FEI. | ||

| + | ICSC1=0x04 // La salida del FLL es seleccionada usando como referencia del clock interno del Módulo. | ||

| + | // En caso de que el MCU caiga en modo stop se deshabilita el clock interno de referencia. | ||

| + | ICSC2=0x11 // La frecuencia del clock interno sera dividido por 2 | ||

| + | ICSTRM=0x04 // Se aumenta el período del clock interno para disminuir un poco mas la frecuencia. | ||

| + | ICSSC= 0x10 // El DCO esta configurado para trabajar en baja frecuencia. | ||

| + | |||

| + | // Ejemplo 7.1.3: Configurando el ICS para trabajar con un clock del FLL en el modo FEE. | ||

| + | ICSC1=0x00 // La salida del FLL es seleccionada usando como referencia el clock externo del Módulo. | ||

| + | // En caso de que el MCU caiga en Modo Stop se deshabilita el clock interno de referencia. | ||

| + | ICSC2=0x93 // La frecuencia para el bus clock sera dividido por 4, el oscilador trabajará con alta ganancia y en baja. | ||

| + | // Frecuencia. El FLL no es deshabilitado en caso de trabajar en modo bypass FBE. | ||

| + | // El ICSERCLK esta activado para usar al ADC. el clock externo permanece activo en caso de caer en Modo Stop. | ||

| + | ICSSC= 0x10 // El DCO esta configurado para trabajar en baja frecuencia. | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | |||

| + | |||

| + | ===Programando el Módulo en Assembler=== | ||

| + | <syntaxhighlight lang="c"> | ||

| + | |||

| + | //Ejemplo 7.2.1: Programando el ''ICS'' en baja frecuencia (2Mhz)usando el circuito FLL.Modo FEI | ||

| + | |||

| + | INCLUDE 'derivative.inc' | ||

| + | |||

| + | ORG $2080 | ||

| + | |||

| + | LDA #$04 // Circuito FLL activado con clock interno (32Khz) como referencia. salida ICSIRCLK desactivada. | ||

| + | STA ICSC1 | ||

| + | LDA #$C0 // La salida del clock del FLL será dividida por 8. salida ICSERCLK desactivada. | ||

| + | STA ICSC2 | ||

| + | LDA #$00 /*DCO configurado para trabajar en baja frecuencia con el clock entre 31.25-39.0625Khz (32Khz en nuestro caso)*/ | ||

| + | STA ICSSC /*la salida del modulo será: ICSOUT= DCOOUT/8= (32Khz x 512)/8=16,38Mhz/8= '''2.04MHZ''' */ | ||

| + | LDA #$00 // No se modifica el período del clock interno. | ||

| + | STA ICSTRM | ||

| + | |||

| + | //Ejemplo 7.2.2: Programando el ''ICS'' en Alta frecuencia (49Mhz)usando el circuito FLL. Modo FEI | ||

| − | + | MOV #0x04,ICSC1 // Circuito FLL activado con clock interno (32Khz) como referencia. salida ICSIRCLK desactivada. | |

| − | + | CLR ICSC2 // La salida del clock del FLL será dividida por 1. salida ICSERCLK desactivada. | |

| − | + | MOV #0x80,ICSSC /*DCO configurado para trabajar en alta frecuencia con el clock entre 31.25-39.0625Khz (32Khz en nuestro caso) | |

| − | + | la salida del modulo será: ICSOUT= DCOOUT/1= (32Khz x 1536)/1=49.15Mhz/1= '''49.15MHZ'''*/ | |

| − | + | CLR ICSTRM // No se modifica el período del clock interno. | |

| − | + | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

Revisión actual del 13:29 5 may 2013

A continuación se presenta una descripcion del Módulo de Clock Interno del MC9S08QE128.

Contenido

- 1 ICS (Configuración Reloj Interno) - MC9S08QE128

- 2 Características del Módulo

- 3 Alcance del Módulo ICS

- 4 Registros del Módulo ICS

- 5 Modos de Operación del Módulo

- 6 Algunas Consideraciones del módulo

- 6.1 Cambios entre Modos de Operación

- 6.2 Factor divisor del Bus de Frecuencia

- 6.3 Uso del bit de Baja Potencia (LP) en el registro ICSC2

- 6.4 Máxima Frecuencia del DCO con un oscilador de 32.768Khz

- 6.5 Clock Interno de Referencia

- 6.6 Clock Externo de Referencia

- 6.7 Clock de Frecuencia Aproximada

- 6.8 Clock Local

- 7 Programación del Módulo ICS

- 8 Referencias

ICS (Configuración Reloj Interno) - MC9S08QE128

¿Qué es el ICS? El Módulo de reloj interno conocido como ICS por sus siglas en inglés (Internal Clock Source) es una fuente de reloj que usa el Microcontrolador MC9S08QE128 de la familia HS08 el cual provee al sistema MCU (Microcontroller Unit) de una frecuencia de operación interna.

¿Para que se utiliza?

La gran ventaja de este modulo es que permite regular la frecuencia del clock con el que trabaja el MCU. Esto es posible gracias a un circuito que contiene el modulo ICS llamado Frecuency-Locked Loop (FLL por su siglas en ingles) el cual permite generar frecuencias estables a partir de la reconversión frecuencial de una fuente de clock referencial, bien sea interna o externa al Microcontrolador.

Características del Módulo

El modulo ICS presenta las siguientes características:

- Un circuito de lazo de frecuencia de enganche o FLL (Frecuency-Locked loop) el cual es programable vía software para generar frecuencias.

- El FLL puede ser controlado por una referencia de clock interna o externa.

- En caso de usar Clock Externo el modulo proporciona un divisor de frecuencia que controla el rango del oscilador.

- Al usar el clock interno como referencia se dispone de 9 bits programables para controlar el rango de frecuencia controlando el período del clock (TRIM).

- Clock interno o externo puede ser seleccionado como fuente para el MCU.

- El modulo provee bits de control para un oscilador de baja potencia usado como clock externo de referencia. Estos bits son: HGO, RANGE, EREFS, ERCLKEN, EREFSTEN ( serán explicados mas adelante).

- Después de un reset el modo de operación es automáticamente configurado para trabajar como FLL Enganged Internal (ver sección de modos de operación).

- El modulo tiene tres tipos de DCO (digitally controlled oscillators), es decir, control digital de oscilador, los cuales ofrecen diferentes rangos de frecuencia agrupadas en tres rangos (Baja,Media y Alta frecuencia).

- Es posible maximizar la frecuencia de salida para una referencia de clock externa.

- El clock para Background Debugged Controller (BDC) es suministrado como una constante dividida por 2 de la salida del oscilador controlado digitalmente en el circuito FLL del módulo (DCO ouput)en el modo bajo rango de frecuencia DCOL(ver figura 1).

- Cualquier clock utilizado como fuente del módulo puede ser dividido mediante un selector de 2 bits que permite divisores de frecuencia de potencias de 1, 2,4 y 8.

Alcance del Módulo ICS

¿Qué hago con el ICS? El conocimiento y manejo del módulo ICS es de vital importancia puesto que representa una fuente de clock controlable vital para el funcionamiento del MCU y de muchos módulos del microprocesador. en la figura 2 se aprecia que el ICS proporciona el clock del bus común a los módulos y ademas posee salidas especificas cuya frecuencia son totalmente programables.

Entre los módulos que requieren de ICS se encuentran

- Contador de Tiempo Real. RTC

- Conversor Analógico Digital.ADC

- Interfaz de Comunicación Serial. SCI

- Interfaz de Comunicación Serial Periférica. SPI

- Circuito Inter-Integrado. IIC

- Temporizador de operacion del computador COP.

- Debug Backgraound DBM. Ver Modos de Operación para mayor información.

- Background Debug Controller BDC.

- Modulador de Ancho de Pulso.

Registros del Módulo ICS

Los registros que permiten configurar y monitorear todas las funciones del módulo ICS son:

(ICSC1) ICS CONTROL REGISTER 1

el registro 1 de control del módulo ICS está compuesto de 8 bits y es un registro de escritura y lectura como se muestra a continuación:

| CLKS | RDIV | IREFS | IRCLKEN | IREFSTEN |

|---|

Donde cada campo representa:

1.CLKS(Clock Source Select): está compuesto por dos bits (7:6) cuya combinación codifica la selección del clock que controla el bus de frecuencia, es decir el clock de salida para el MCU . La frecuencia de este bus depende del valor en BDIV bits (será explicado mas adelante)

00 Selecciona como clock la salida del circuito FLL. 01 Selecciona el clock interno como referencia. 10 Selecciona el clock externo como referencia. 11 Reservado, no se utiliza.

2.RDIV (Reference Divider): está formado por 3 bits ( 5:3) cuya codificación binaria, y en conjunto con los bits de RANGE(ver más adelante), seleccionan el divisor de frecuencia cuando el clock externo es usado como referencia. La frecuencia resultante debería estar en el rango de 31.25Khz-39.0625Khz.

A continuación se muestra la combinación que debe tener RDIV y RANGE para seleccionar el factor divisor de frecuencia:

"Tabla 1. Factor divisor de Frecuencia"

| RDIV | RANGE=0 | RANGE=1 |

|---|---|---|

| 0 | 1 | 32 |

| 1 | 2 | 64 |

| 2 | 4 | 128 |

| 3 | 8 | 256 |

| 4 | 16 | 512 |

| 5 | 32 | 1024 |

| 6 | 64 | Reservado. |

| 7 | 128 | Reservado. |

3.IREFS (Internal Reference Select): está compuesto por un bits y selecciona el clock de referencia para el circuito FLL

| 0 | 1 |

|---|---|

| Clock Externo seleccionado como referencia para el FLL. | Clock Interno seleccionado como referencia para el FLL. |

4.IRCLKEN(Internal Reference Clock Enable) :está compuesto por 1 bits y se encarga de habilitar el clock interno para ser usado como ICSIRCLK (ver diagrama de bloques Figura 1). Es decir, el clock interno es tomado como salida del módulo ICS sin hacerle ninguna modificación

| 0 | 1 |

|---|---|

| ICSIRCLK desactivado. | ICSIRCLK activado. |

5.IREFSTEN(Internal Reference Stop Enable): este bit controla si el clock de referencia interna permanece habilitado, o no, una vez que el módulo entre en el modo de Stop

| 0 | 1 |

|---|---|

| El clock interno es deshabilitado en el modo de stop. | El clock de referencia interno permanece habilitado una vez entrado al modo de stop si el bits de IRCLKEN está en uno lógico antes de entrar en dicho módulo. |

Nota: los bits de este registro después de un reset están en 0 salvo el bit IREFS que esta en 1.

ICS Control Register 2 (ICSC2)

El registro 2 de control del módulo ICS contiene 8 bits programables de escritura-lectura. El bit mas significativo a la izquierda y el menos significativos a la derecha como sigue:

| BDIV (bits 7:6). | RANGE (5). | HGO (4). | LP (3). | EREFS(2). | ERCLKEN(1). | EREFSTEN (0). |

|---|

Descripción de los set de Bits:

1.BDIV(Bus Frecuency Divider): Selecciona la cantidad con la cual se dividirá la frecuencia del clock escogido por los bits de CLK para alimentar el bus de frecuencia del microcotrolador. La codificación de los bits es como sigue:

| 00 | 01 | 10 | 11 |

|---|---|---|---|

| Divide la frecuencia del clock escogido como salida por 1. | Divide la frecuencia del clock por 2 (modo escogido después de un reset.) | Divide la frecuencia del clock por 4. | Divide la frecuencia del clock por 8. |

2.RANGE (Frecuency Range Select): selecciona el rango de frecuencia para el oscilador externo. Se configura en conjunto con el bit RDIV (ver tabla 1).

| 0 | 1 |

|---|---|

| Selecciona el modo de Baja frecuencia para el oscilador externo. | Selecciona el modo de Alta frecuencia para el oscilador externo. |

3.HGO (High Gain Oscillator Select): selecciona el modo de operación del oscilador externo.

| 0 | 1 |

|---|---|

| Configura el oscilador externo para trabajar en modo de baja potencia. | Configura el oscilador externo para trabajar en modo de alta ganancia. |

4.LP (Low Power Select): este bit determina si el circuito FLL queda desactivado cuando se trabaja en el modo de operación tipo FLL bypass.

| 0 | 1 |

|---|---|

| FLL se mantiene activo en el modo de operación FLL bypass. | FLL es desactivado en el modo de operación FLL bypass a menos que el BMD esta activo. |

5.EREFS (External Reference Select): este bit selecciona el tipo de fuente para la referencia de clock externa.

| 0 | 1 |

|---|---|

| Clock Externo requerido como fuente. | Oscilador requerido como fuente.

|

6.ERCLKEN (External Reference enable): se encarga de habilitar el clock externo para ser usado como ICSERCLK (ver diagrama de bloques Figura 1). Es decir, el clock externo es tomado como salida del módulo ICS sin hacerle ninguna modificación.

| 0 | 1 |

|---|---|

| ICSERCLK desactivado. | ICSERCLK activado. |

7.ERFSTEN (External Reference Stop Enable): este bit controla si el clock de referencia externa permanece habilitado, o no, una vez que el módulo entre en el modo de Stop.

| 0 | 1 |

|---|---|

| El clock externo es deshabilitado en el modo de stop. | El clock de referencia externo permanece habilitado una vez entrado al modo de stop si el bits de ERCLKEN está en uno lógico antes de entrar en dicho modo de operación. |

Nota: los bits de este registro después de un reset están en 0 salvo el bit 6 del BDIV que esta en 1.

ICS Trim Register (ICSTRM)

Este registro de 8 bits de escritura-lectura se encarga de controlar la frecuencia del Clock de referencia interna modificando el período del clock, el tipo de cambio se hace de modo binario, es decir, los bits en 1 a 0 y viceversa. Un incremento en el valor binario de este registro , incrementa el período del clock. Un decremento en el valor binario disminuye el período. Exite otro bits usado para el ajuste mas pequeño del Trim el cual se encuentra en el modulo de Status y controlo Register (ICSSC).

| TRIM (bits 7:0) |

|---|

ICS Status and Control Register(ICSSC)

Este es un registro que posee 8 bits donde se encuentran bits de estatus (sólo lectura) y bits de control (escritura-lectura). La distribución de bits es tal que bit más significativo se encuentra a la izquierda y el menos significativo a la derecha como sigue:

| DRST(lectrua) / DRS(escritura) (bits 7:6). | DMX (5). | IREFST(4). | CLKST (3:2). | OSCINIT(1). | FTRIM(0). |

|---|

1.DRST (DCO Range Status): este campo es de solo lectura e indica que tipo de rango de frecuencia es arrojado por el ciercuito FLL, es decir, el DCOOUT (ver figura 1).Este campo no se actualiza inmediatamente después de una escritura en DRS(en breve será explicado) debido a la sincronización interna entre clocks, por lo que debemos esperar como mínimo un ciclo de reloj para solicitar la lectura del DRST.

DRS( DCO Range Select): el selector del rango de frecuencia del DCO es programable con dos bits de la siguiente manera:

| 00 | 01 | 10 | 11 |

|---|---|---|---|

| Baja frecuencia (Low Range). | Frecuencias Medias (Mide Range). | Alta frecuencia (High Range). | Reservado. |

¡ATENCION! La escritura de 11 en DRS es ignorada y DRST permanece en la configuración actual. Este espacio es reservado.

¡ATENCION! Escribir en DRS mientras el bit de baja potencia (LP) en ICSC2 esta activo no produce ningún resultado, ¡es ignorado por el CPU!

2.DMX32 (DCO Maximun Frecuency with 32.768Khz reference): este bit de control decide si el rango de frecuencia del DCO es aproximado a su máxima frecuencia con un clock de referencia de 32.768Khz (clock interno).En otras palabras el factor del FLL es máximo y la frecuencia es mayor y muy aproximado a la frecuencia máxima de la configuración. (Ver tabla 2).

| 0 | 1 |

|---|---|

| El DCO trabaja en un rango del 25% de la frecuencia de referencia. | El DCO es conducido a su máxima frecuencia cuando el clock de referencia es de 32.768Khz. |

En la Siguiente Tabla se muestra la combinación de los bits de DRS y DXM32 y las frecuencias que ellas generan:

¡CUIDADO! La frecuencia del clock del Bus que conecta otros módulos no debería exceder el máximo valor de frecuencia permitido por el dispositivo.

3.IREFST(Internal Reference Status): es un bit de sólo lectura que indica que tipo de fuente está siendo usada como referencia del clock del circuito FLL. Es útil usar este bit como bandera para que el CPU tome alguna decisión a gusto del programador.

| 0 | 1 |

|---|---|

| La fuente usada como referencia para el circuito FLL es un Clock Externo. | La fuente usada como referencia es un Clock Interno. |

4.CLKST (Clock Mode Status): este campo contiene 2 bits que indican en qué modo está trabajando el clock. Estos bits son como una bandera que muestran el estatus del campo CLKS en el registro ICSC1. Si se escribe en CLKS, el valor de CLKST no cambia inmediatamente debido a la sincronización de los clocks internos.

| 00 | 01 | 10 | 11 |

|---|---|---|---|

| La salida del FLL está seleccionada como fuente de clock. | El FLL no está siendo usado (Bypassed), el Clock interno de referencia es usado como fuente de clock. | El FLL no está siendo usado (Bypassed), el Clock externo de referencia es usado como fuente de clock. | Reservado. |

5.OSCINIT (OSC Initialization): Si el clock externo es seleccionado por el campo ERCLKEN en el registro ICSC2 o se trabaja en el modo FEE,FBE o FBLEP (ver más adelante), y además el bit EREFS está en uno lógico, entonces el OSCINIT se pone en uno lógico después que la inicialización del clock externo es completado.

En otras palabras, indica si el clock externo ya fue inicializado. Este bit es llevado a cero cuando se deshabilita el uso del clock externo.

6.FTRIM (ICS Fine TRIM): este bit es el más pequeño ajuste del registro TRIM (ver ICSTRIM) , si está en 1 lógico se incrementa el Período del clock interno en la más pequeña cantidad posible; si esta en 0 lógico se decrementa el período en la más pequeña cantidad posible.

Visto más fácil: es una extensión del registro ICSTRIM y representa el bit de mayor precisión con el que se puede hacer los cambios más pequeños en la frecuencia del clock interno.

Uso de los Registros del ICS

¿Como Inicio la programación de los Registros?

para programar el ICS debemos conocer el alcance que tiene cada registro:

- Usemos el registro ICSC1para:

- Escoger la fuente que generará el clock deseado (FLL, Clock Interno(IC) o Clock Externo(EC)).

- En caso de usar el FLL escoger la referencia que usará este circuito (Clock Interno o Externo).

- Habilitar o no la salida ICSIRCLK que es fuente del módulo RTC.

- Habilitar o no el clock interno en caso de actuar en el modo de Stop.

- Seleccionar el factor divisor de frecuencia en caso de usar el clock externo.

- Usemos el registro ICSC2 para:

- Escoger el factor de division de frecuencia que se le aplicará a la salida de nuestra fuente de clock (FLL,IC,EC).

- Seleccionar si trabajaremos en Alta o Baja frecuencia.

- Configurar el oscilador para trabajar con alta ganancia o baja potencia.

- Habilitar o no el FLL en caso de trabajar en los modos del tipo Bypass FLL.

- Habilitar o no el ICSERCLK que es salida del clock externo que sirve de fuente al módulo ADC.

- Habilitar o no el clock externo en caso de actuar en el modo de Stop.

- Usemos el registro ICSTRM para controlar la frecuencia del Clock interno de referencia variando su período.

- Usemos el Registro ICSSC para verificar estatus de funcionamiento, tales como:

- Chequear en que rango de frecuencia se trabaja (Baja, Media o Alta).

- Chequear que tipo de referencia se está usando (Clock interno o Externo).

- Chequear en que modo de trabajo se encuentra el clock (FLL, SóloClock Interno, Sólo Clock Externo).

- Chequear si el clock externo fue inicializado correctamente en caso de usarlo.

También se puede usar para configurar lo siguiente:

- Los cambios mas pequeños en la variación del período del Clock interno mediante el FTRIM.

- El tipo de rango de frecuencia que tendrá el DCO del circuito FLL (Baja, Media o Alta).

- IMPORTANTE:Existen dos Registros que permiten controlar la habilitación del busclock hacia todos los módulos que lo requieren. Ellos son los registro de compuertas de control de sistema de reloj SCGC1 y SCGC2 por sus siglas en inglés (System Clock Gating Control).

- Usemos el registro SCGC1 para habilitar el busclock de los siguientes módulos:

- Temporizador para modulación de ancho de pulso (TPM1, TPM2 y TPM3).

- Conversor Analógico Digtal (ADC).

- Cirucuito Inter-Integrado (IIC1 e IIC2).

- Interfaz de comunicación serial (SCI1 y SCI2).

Diagrama del Registro SCGC1 (8 bits):

| TPM3 (bit 7). | TPM2 (6). | TPM1 (5). | ADC (4). | IIC2(3). | IIC1(2). | SCI2 (1). | SCI1 (0). |

|---|

- Usemos el registro SCGC2 para habilitar el busclock de los siguientes módulos:

- Depurador de Programa DBG

- Registros de memoria Flash (FLS).

- Interrupciones Externas. IRQ

- Interrupciones por Teclado.

- Comparador Analógico.

- Contador de tiempo real.

- Interfaz de comunicación serial periférica.

Diagrama del Registro SCGC2 (8 bits):

| DBG (bit 7). | FLS (6). | IRQ (5). | KBI (4). | ACMP(3). | RTC(2). | SPI2 (1). | SPI1 (0). |

|---|

NOTA: Después de un reset el busclock está habilitado para todos los módulos escribiendo un uno lógico (1) en cada posición del registro. Si desea conservar potencia puede deshabilitar el busclock de los módulos que no estén en uso escribiendo cero lógico (0)en las posiciones del registro que desee desconectar.

¡Enhorabuena! ya solo falta conocer los modos de operación para comenzar a programar el módulo de ICS.

Modos de Operación del Módulo

Existen siete modos de operación del modulo ICS los cuales son:

FLL Enganged Internal (FEI)

En este caso el FLL esta 'Enganchado' con el clock interno.Es el modo de operación por defecto despues de un reset en el microprocesador en el cual la salida del módulo ICSOUT (ver figura 1) es la salida del circuito FLL que es controlada por la referencia de clock interna.En este caso el BDC es alimentado por el clock del FLL mediante la salida ICSLCLK. En este caso el factor divisor de frecuencia viene dado por los bits del BDIV en el registro ICSC2

¿Cuando sucede esto?

- Los bits de CLKS (ICSC1)deben estar en 00

- El bit IREFS debe ser 1 lógico

FLL Enganged External (FEE)

En este caso el FLL esta 'Enganchado' con el clock Externo. Por lo tanto, la salida del módulo ICSOUT' es derivada del circuito FLL el cual usa como referencia dicho clock. En este caso el factor divisor de frecuencia es seleccionado por los bits de RDIV. En este caso el BDC es alimentado por el clock del FLL mediante la salida ICSLCLK

¿Cuando sucede esto?

- Los bits de CLKS (ICSC1)deben estar en 00.

- El bit IREFS debe ser 0 lógico.

- Los bits de RDIV deben indicar el factor de división del FLL tal que la frecuencia queden en el rango 31.25-39.0625 Khz.

FLL Bypassed Internal (FBI)

En este caso la salida del módulo ICSOUT es derivada directamente del clock interno de referencia sin usar la salida del FLL. por eso se dice en lenguaje común que el circuito FLL es 'Bypaseado'. Sin embargo, el FLL estará programado en este modo para seguir activo y usando el clock interno como referencia aunque sea ignorado por el MCU. En este caso el BDC es alimentado por el clock del FLL mediante la salida ICSLCLK.

¿Cuando sucede esto?

- Los bits de CLKS (ICSC1)deben estar en 01 .

- El bit IREFS debe ser 1 lógico.

- El modo BDM (Backgroun Debug Mode) debe estar activo o el bit LPen ICSC2 debe ser 0.

FLL Bypassed Internal Low Power (FBILP)

Este modo de operación es igual al modo FBI salvo que en este caso el FLL queda desactivado por completo. El clock para el BDC no estará disponible y el clock interno se mantiene activo.

¿Cuando sucede esto?

- Los bits de CLKS (ICSC1)deben estar en 01

- El bit IREFS debe ser 1 lógico

- El modo BDM (Backgroun Debug Mode) debe estar inactivo o el bit LPen ICSC2 debe ser 1

FLL Bypassed External (FBE)

En este caso la salida del módulo ICSOUT es derivada directamente del clock externo de referencia sin usar la salida del FLL. Sin embargo, el FLL estará programado en este modo para seguir activo y usando el clock externo como referencia aunque sea ignorado por el MCU. En este caso el BDC es alimentado por el clock del FLL mediante la salida ICSLCLK.

¿Cuando sucede esto?

- Los bits de CLKS (ICSC1)deben estar en 10.

- El bit IREFS debe ser 0 lógico.

- El modo BDM (Backgroun Debug Mode) debe estar activo o el bit LPen ICSC2 debe ser 0.

- Los bits de RDIV deben indicar el factor de división del FLL tal que la frecuencia queden en el rango 31.25-39.0625 Khz.

FLL Bypassed External Low Power (FBELP)

Este modo de operación es igual al modo FBE salvo que en este caso el FLL queda desactivado por completo. El clock para el BDC no estará disponible y el clock externo se mantiene activo.

¿Cuando sucede esto?

- Los bits de CLKS (ICSC1)deben estar en 10.

- El bit IREFS debe ser 0 lógico.

- El modo BDM (Backgroun Debug Mode) debe estar inactivo o el bit LPen ICSC2 debe ser 1.

STOP

Este modo ocurre cuando el MCU entre en estado de standby . En este caso todas las salidas del módulo ICS quen estaticas excepto en los siguientes casos que decida el programador:

- la salida ICSIRCLK que usa el RTC queda activo a pesar de que el modulo entre en modo stop ¿Cuando sucede esto?

- IRCLKEN en el registro ICSC1 debe estar en 1.

- IREFSTEN en el registro ICSC1 debe estar en 1.

- la salida ICSERCLK que usa el ADC queda activo a pesar de que el modulo entre en modo stop ¿Cuando sucede esto?

- ERCLKEN en el registro ICSC2 debe estar en 1.

- EREFSTEN en el registro ICSC2 debe estar en 1.

Algunas Consideraciones del módulo

Cambios entre Modos de Operación

- El bit IREF puede ser cambiado en cualquier momento pero el cambio no será mostrado inmediatamente por el bit IREFST del registro ICSSC.

- Cuando se pasa del modo FEI al modo FEE, la salida del modulo se enganchará a la nueva frecuencia y clock de referencia cuando el cambio sea completado correctamente.

- El bit CLKS puede ser cambiado en cualquier momento pero el cambio no será mostrado inmediatamente por el bit CLKST del registro ICSSC.

- El bit DRS puede ser cambiado en cualquier momento excepto cuando el bit LP está en 1. Si DRS es cambiado mientras se trabaja en modo FEI o FEE el clock del bus permanece en el rango de frecuencia anterior hasta que se inicialice el nuevo DCO. Después que cambie el DCO el FLL permanecerá desenganchado de la frecuencia seleccionada por algunos ciclos. Cuando el cambio es completado totalmente, los bits del DRST se actualizan.

Factor divisor del Bus de Frecuencia

Los bits de BDIV en el registro ICSC2 pueden ser cambiados en cualquier momento y el cambio actual ocurre inmediatamente.

Uso del bit de Baja Potencia (LP) en el registro ICSC2

- Este bit es usado para permitir al circuito FLL estar deshabilitado y conservar potencia cuando no está siendo usado.

- Los bits DRS no pueden ser cambiados mientras LP esté en 1.

- En los casos en los que se desee mantener el FLL activo aunque no se use por momentos (Modo Bypass) se deberá colocar el bt LP en 0.

Máxima Frecuencia del DCO con un oscilador de 32.768Khz

FLL puede ser programado de tal forma que la frecuencia en el bus sea máxima a partir de un Oscilado común de 32.768 Khz.

Clock Interno de Referencia

- Cuando el bit IRCLKEN está en 1 el modulo arrojará una una fuente de clock adicional llamada ICSIRCLK. la frecuencia de esta señal puede ser modificada cambiando el período clock interno con los valores cargados en el registro ICSTRM (Trimming). cargar un valor pequeño en ICSTRM disminuye el periodo y por lo tanto aumenta frecuencia. Incrementar el valor del ICSTRM aumenta período ergo disminuye frecuencia.

- Al ser modificado el registro ICSTRM la salida del modulo será afectada siempre que el FLL trabaje en los modos FEI, FBI, FBILP.

- Si el bit IREFSTEN está en 1 y el IRCLKEN también lo está, el clock de referencia interna continua corriendo durante el modo de stop.

- Si el usuario desea mayor precisión en la frecuencia del clock interno deberá variar el bit FTRIM en el registro ICSC2.

- Hay que tener cuidado cuando se programa el RDIV en el rango de baja frecuencia puesto que puede resultar que en la salida del módulo aparezcan frecuencias que excedan el máximo nivel que soporta el Chip.

Clock Externo de Referencia

- El Módulo ICS soporta un clock externo de referencia con frecuencias entre 31.25Khz-40Mhz en todos los modos d operación.

- Cuando el bit ERCLKEN está en 1 el modulo arrojará una una fuente de clock adicional llamada ICSERCLK.

- Cuando el bit IREFS es 1 el clock externo no es usado por el FLL. En este caso el clock externo arrojará una salida unicamente del tipo ICSERCLK.

- Si el bit EREFSTEN está en 1 y el ERCLKEN también lo está, el clock de referencia externa continua corriendo durante el modo de stop.

Clock de Frecuencia Aproximada

El módulo ICS presenta un clock adicional de referencia llamado ICSFFCLK (Ver figura 1). La frecuencia de este clock no deberia ser mayor a 1/4 de la salida ICSOUT para ser válido.

Clock Local

El módulo ICS posee un clock como salida del DCO de baja frecuencia (Low Range) llamado ICSLCLK el cual es usado como clock para el BDC. este clock no está habilitado para los modo de FBILP y FBELP.

Programación del Módulo ICS

Programando el Módulo en Lenguaje C

#include "derivative.h"

//Ejemplo 7.1.1: Configurando un clock con referencia de clock interna para el RTC

ICSC1= 0x46 // la salida ICSICLK esta activo con referencia interna del Clock

// En caso de que el MCU caiga en Modo Stop se deshabilita el clock interno de referencia.

//El Módulo FLL usa como fuente el clock interno aunque no es usado por el MCU.

ICSC2=0x88 // La frecuencia será el clock interno dividido por 4.

//Se configura el clock externo para trabajar en baja frecuencia y baja potencia aunque en realidad no es usado por ICS.

//La Fuente de Clock ICSERCLK usado por el ADC esta inactivo.

//El clock externo en caso de usarse queda deshabilitado si el MCU entre en Modo Stop.

ICSTRM=0x00 // No se modificará el período de clock interno para variar su frecuencia.

// Ejemplo 7.1.2: Configurando el ICS para trabajar con un clock del FLL en el modo FEI.

ICSC1=0x04 // La salida del FLL es seleccionada usando como referencia del clock interno del Módulo.

// En caso de que el MCU caiga en modo stop se deshabilita el clock interno de referencia.

ICSC2=0x11 // La frecuencia del clock interno sera dividido por 2

ICSTRM=0x04 // Se aumenta el período del clock interno para disminuir un poco mas la frecuencia.

ICSSC= 0x10 // El DCO esta configurado para trabajar en baja frecuencia.

// Ejemplo 7.1.3: Configurando el ICS para trabajar con un clock del FLL en el modo FEE.

ICSC1=0x00 // La salida del FLL es seleccionada usando como referencia el clock externo del Módulo.

// En caso de que el MCU caiga en Modo Stop se deshabilita el clock interno de referencia.

ICSC2=0x93 // La frecuencia para el bus clock sera dividido por 4, el oscilador trabajará con alta ganancia y en baja.

// Frecuencia. El FLL no es deshabilitado en caso de trabajar en modo bypass FBE.

// El ICSERCLK esta activado para usar al ADC. el clock externo permanece activo en caso de caer en Modo Stop.

ICSSC= 0x10 // El DCO esta configurado para trabajar en baja frecuencia.

Programando el Módulo en Assembler

//Ejemplo 7.2.1: Programando el ''ICS'' en baja frecuencia (2Mhz)usando el circuito FLL.Modo FEI

INCLUDE 'derivative.inc'

ORG $2080

LDA #$04 // Circuito FLL activado con clock interno (32Khz) como referencia. salida ICSIRCLK desactivada.

STA ICSC1

LDA #$C0 // La salida del clock del FLL será dividida por 8. salida ICSERCLK desactivada.

STA ICSC2

LDA #$00 /*DCO configurado para trabajar en baja frecuencia con el clock entre 31.25-39.0625Khz (32Khz en nuestro caso)*/

STA ICSSC /*la salida del modulo será: ICSOUT= DCOOUT/8= (32Khz x 512)/8=16,38Mhz/8= '''2.04MHZ''' */

LDA #$00 // No se modifica el período del clock interno.

STA ICSTRM

//Ejemplo 7.2.2: Programando el ''ICS'' en Alta frecuencia (49Mhz)usando el circuito FLL. Modo FEI

MOV #0x04,ICSC1 // Circuito FLL activado con clock interno (32Khz) como referencia. salida ICSIRCLK desactivada.

CLR ICSC2 // La salida del clock del FLL será dividida por 1. salida ICSERCLK desactivada.

MOV #0x80,ICSSC /*DCO configurado para trabajar en alta frecuencia con el clock entre 31.25-39.0625Khz (32Khz en nuestro caso)

la salida del modulo será: ICSOUT= DCOOUT/1= (32Khz x 1536)/1=49.15Mhz/1= '''49.15MHZ'''*/

CLR ICSTRM // No se modifica el período del clock interno.

Referencias

Manual de usuario DEMOQE128 (Rev A)

Publicado por: Jesús Grimón

Contributors

AK, Artdamato, JRodríguez, Jesus Grimón, LitzaPinto, Minleung, Misato, Racuna, Ramor