SPI: Interfaz de Serial Periferico para el microcontrolador QE - MC9S08QE128

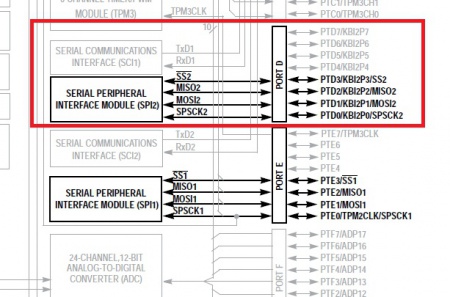

Nota: Para empezar a usar este recurso, si se esta utilizando la tarjeta DEMOQE128, se sugiere hacer la inicializaciones para el segundo modulo del SPI2, porque este solo tiene 40 pines y estos no contienen los PTE del primer modulo del SPI1. Como se observa en la figura

Contenido

- 1 Introducción

- 2 Elementos Fundamentales que componen el SPI

- 3 El Módulo SPI

- 4 Características del SPI

- 5 Estructuras de los Registros de la SPI

- 6 Descripción funcional de la SPI

- 7 Tiempos del Reloj del SPI

- 8 Interrupciones del SPI

- 9 Modo de Detección de Fallos

- 10 Protocolos de Configuración de la SPI

- 11 Referencias Consultadas

Introducción

El Bus SPI (del inglés Serial Peripheral Interface) es un estándar de comunicaciones, cuya función principal es la transferencia de datos entre circuitos integrados en equipos electrónicos. El MC9S08QE128 cuenta con dos módulos de SPI para realizar operaciones entre módulos periféricos( por (por ejemplo: sensores), lo cual le permite al usuario controlar casi cualquier dispositivo electrónico digital que acepte un flujo de bits regulado por un reloj.

Elementos Fundamentales que componen el SPI

RELOJ SERIAL DEL SPI (SPSCK): Cuando el SPI es habilitado como un esclavo, este pin es la entrada del clock. Cuando el SPI es habilitado como maestro, este pin es la salida del clock.

SALIDA DE DATO MAESTRO, ENTRADA DE DATO ESCLAVO (MOSI):

Si SPC0 = 0 -> Modo no bidireccional Cuando el SPI es habilitado como maestro (MSTR) y SPC0 = 0, este pin es la salida de dato serial. Cuando el SPI es habilitado como esclavo (SSOE) y SPC0 = 0, este pin es la entrada de dato serial.

Si SPC0 = 1 -> Modo bidireccional

Si SPC0 = 1 y el modo maestro (MSTR) está seleccionado, este pin se convierte en el pin de entrada/salida de dato bidireccional (MOMI).

Si SPC0 = 1 y el modo esclavo (SSOE) esta seleccionado, este pin no es usado por la SPI y vuelve a ser un pin de puerto de entrada/salida uso general.

El bit de habilitación de salida de modo bidireccional (BIDIROE), determina si el pin se comporta como una entrada (BIDIROE = 0) o como una salida (BIDIROE = 1).

ENTRADA DE DATO MAESTRO, SALIDA DE DATO ESCLAVO (MISO): Cuando el SPI es habilitado como maestro y el pin de control Zero de la misma(SPC0) es 0 (en modo no bidireccional), este pin es la entrada de dato serial. Cuando la SPI es habilitada como esclavo y SPC0 = 0, este pin es la salida de dato serial. Si SPC0 = 1 para seleccionar el modo bidireccional de cable simple, y el modo esclavo está seleccionado, este pin se convierte en el pin de entrada – salida de dato bidireccional (SISO), además, el bit de habilitación de salida de modo bidireccional determina si el pin se comporta como una entrada (BIDIROE = 0) o como una salida (BIDIROE = 1). Si SPC0 = 1 y el modo maestro esta seleccionado, este pin no es usado por la SPI y vuelve a ser un pin de puerto de entrada – salida de uso general.

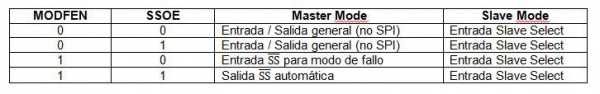

SLAVE SELECT ((SS)): Cuando el SPI esta habilitado como esclavo, este pin es la selección de entrada “low-true” del esclavo. Cuando el SPI esta habilitado como maestro y el habilitador del modo de fallo esta apagado (MODFEN = 0), este pin no es utilizado por la SPI y vuelve a ser un pin de puerto entrada - salida de uso general. Cuando la SPI esta habilitada como maestro y el MODFEN = 1, el bit habilitador de selección de salida del esclavo determina si ese pin se comporta como la entrada del modo de fallo (SSOE = 0) o como la salida de Slave Select (SSOE = 1).

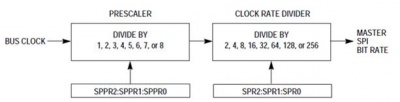

TASA DE BAUDIOS DEL SPI:

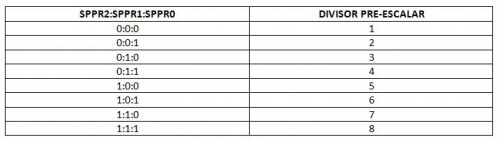

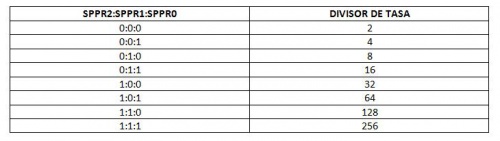

En la imagen inferior puede apreciarse que, la fuente del reloj para la Tasa de Baudios del SPI es el bus Clock. Los tres bits de calibración (SPPR2:SPPR1:SPPR0) seleccionan un divisor de calibración de 1, 2, 3, 4, 5, 6, 7 u 8. Los tres bits de selección de tasa (SPR2:SPR1:SPR0) dividen la salida de la etapa de calibración por 2, 4, 8, 16, 32, 64, 128 ó 256 para conseguir el Clock de tasa de bits interno de la SPI en modo maestro.

Descripción de Señal Externa: La SPI opcionalmente comparte cuatro pines de puerto. La función de estos pines depende de los ajustes de los bits de control de la SPI. Cuando la SPI es inhabilitada (SPE = 0) estos cuatro pines se convierten en puertos de entrada – salida de uso general y no son controlados por el SPI.

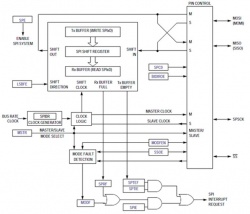

El Módulo SPI

El elemento central de la SPI es el registro de desplazamiento SPI. Los datos se escriben en el transmisor de doble búfer (escrito en SPIxD) y se transfieren al registro de desplazamiento SPI al inicio de una transferencia de datos. Después de desplazar en un byte el dato, este es transferido dentro del receptor de doble búfer donde puede ser leído (leído desde SPIxD).

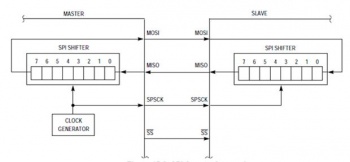

Cuando el SPI es configurado como maestro, el reloj de salida es dirigido por el pin SPSCK, el shifter output es dirigido por MOSI, y el shifter input desde el pin MISO. Cuando el SPI es configurado como esclavo, el pin SPSCK es dirigido por la entrada de reloj del SPI, el shifter output es dirigido por MISO y el shifter input desde el pin MOSI. En sistemas SPI externos, simplemente se conectan todos los pines SPSCK con los otros, todos los pines MISO juntos y todos los pines MOSI juntos. Los dispositivos periféricos a menudo utilizan nombres ligeramente diferentes para estos pines. En la figura se muestra el diagrama de bloques del módulo SPI.

Características del SPI

Entre las características del módulo SPI se incluye:

• Modo de operación maestro/esclavo.

• Opciones bidireccionales de un solo cable o cable doble.

• Rango de bits de transmisión programable.

• Doble búfer para transmisión y recepción.

• Opciones de fase y polaridad del reloj serial.

• Selección de salida esclavo.

• Cambio seleccionable entre bit más significativo primero y bit menos significativo primero.

Pueden conectarse varias unidades de microcontrol para crear sistemas de transferencia de datos. Por ejemplo, en el esquema se muestran los módulo SPI de dos unidades de microcontrol conectados en un arreglo maestro – esclavo. El dispositivo maestro inicializa todas las transferencias de dato SPI. Durante una transferencia, el maestro pasa el dato de salida, en el pin MOSI, al esclavo, mientras que, simultáneamente, recibe el dato de entrada (en el pin MISO) del esclavo. La transferencia cambia eficazmente los datos en los registros de desplazamiento SPI de los dos sistemas. La señal SPSCK es un reloj de salida desde el maestro y una entrada al esclavo. El dispositivo esclavo debe ser seleccionado por un bajo nivel en la entrada “slave select” (pin SS). En este sistema, el dispositivo maestro ha configurado su pin SS como una salida “slave select” opcional.

Los usos más comunes de sistemas SPI incluyen conexiones simples de los registros de desplazamiento para sumar puertos de entradas o salidas, o conectar pequeños dispositivos periféricos como conversores A/D o D/A serial. A pesar de que en la figura dos se muestra un sistema donde el dato es intercambiado entre dos unidades de microcontrol, muchos sistemas prácticos solo requieren conexiones simples donde el dato es transferido unidireccionalmente desde la unidad de microcontrol maestra al esclavo, o desde el esclavo a la unidad de microcontrol maestra.

Estructuras de los Registros de la SPI

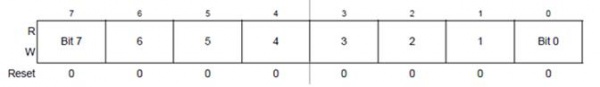

La SPI tiene cinco registros de 8 – bits para selección de opciones SPI, control de velocidad de transmisión, reporte de estado SPI y para transmitir/recibir datos. A continuación se presenta una descripción de los registros y bits de control sólo por sus nombres.

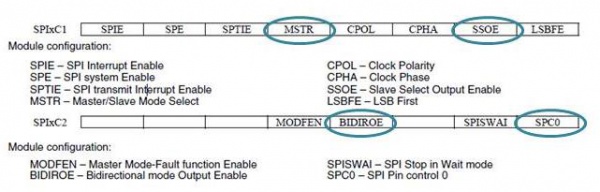

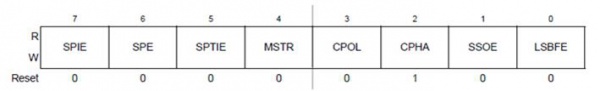

Registro de Control 1 de la SPI (SPIxC1)

Este registro de lectura/escritura incluye la habilitación de control de la SPI y opciones de configuración.

| Bits | Descripción |

|---|---|

| 7

SPIE |

SPI Habilitador de Interrupciones (Para SPRF y MODF): Este es el habilitador de interrupciones para recibir SPI memoria llena (SPRF) y eventos de modo de fallo (MODF).

0 Interrupciones desde SPRF y MODF inhabilitadas (utilizar sondeo) 1 Cuando SPRF o MODF es 1, solicitar una interrupción de Hardware. |

| 6

SPE |

SPI Habilitador de Sistema: La desactivación del SPI detiene cualquier transferencia que esté en curso, borra los buffers de datos e inicializa maquinas de estado internas. SPRF se borra y SPTEF se establece para indicar si el buffer de transmisión de datos está vacío.

0 SPI Sistema inactivo. 1 SPI Sistema habilitado. |

| 5

SPTIE |

SPI Habilitador de Transmisión de Interrupciones: Este es el bit habilitador de interrupción para el buffer de transmisión SPI vacío (SPTEF).

0 Interrupción desde SPTEF inhibido (use sondeo). 1 Cuando SPTEF es 1, solicita interrupción de hardware. |

| 4

MSTR |

Selección de modo Maestro/Esclavo:

0 Módulo SPI configurado como un dispositivo SPI Esclavo. 1 Módulo SPI configurado como un dispositivo SPI Maestro. |

| 3

CPOL |

Polaridad del Reloj: Este bit coloca efectivamente un inversor en serie con la señal de reloj desde un SPI maestro o hacia un SPI esclavo.

0 Reloj SPI Alto-activo. 1 Reloj SPI Bajo-activo. |

| 2

CPHA |

Fase del Reloj: Este bit selecciona uno de dos formatos de reloj para diferentes tipos de dispositivos periféricos sincronizados.

0 Primer borde en SPSCK se produce en la mitad del primer ciclo de una transferencia de datos de 8 ciclos. 1 Primer borde en SPSCK se produce al inicio del primer ciclo de una transferencia de datos de 8 ciclos. |

| 1

SSOE |

Habilitador de salida de Slave Select: Este bit se utiliza en combinación con el bit habilitador de modo de fallo (MODFEN) en SPCR2 y el bit de control te maestro/esclavo (MSTR) para determinar la función del pin (SS) como se muestra en la tabla anexa. |

| 0

LSBFE |

Bit menos significativo primero:

0 Transferencia de datos serial SPI inicia con el bit mas significativo. 1 Transferencia de datos serial SPI inicia con el bit menos significativo. |

TABLA 1: Función del Pin SS.

NOTA: Asegúrese de que la SPI no debe desactivarse (SPE = 0) al mismo tiempo como un cambio de bit para el bit CPHA.

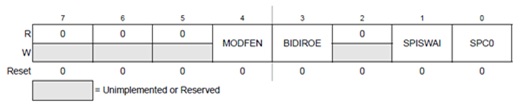

Registro de Control 2 de la SPI (SPIxC2)

Este registro de lectura/escritura incluye la habilitación de control de la SPI y opciones de configuración.

| Bits | Descripción |

|---|---|

| 4

MODFEN |

Habilitador de Función de Fallo en Modo Maestro: cuando el SPI es configurado para modo esclavo, este bit no tiene significado o efecto. (El pin (SS) es la entrada Slave Select) En modo maestro, este bit determina cómo es utilizado el pin (SS). (Tabla 2)

0 Función de modo de fallo deshabilitada, Pin (SS) maestro vuelve a ser un pin de puerto entrada/salida general no controlado por SPI. 1 Función de modo de fallo habilitada, Pin (SS) maestro se comporta como entrada de modo de fallo o salida de Slave Select. |

| 3

BIDIROE |

Habilitador de Salida en Modo Bidireccional: Cuando el modo bidireccional está habilitado por el pin de control de la SPI (SPC0 = 1), BIDIROE determina si el driver de dato de salida SPI esta habilitado para el pin de entrada/salida bidireccional simple. Dependiendo de si la SPI esta configurada como maestro o esclavo, este usa el pin MOSI (MOMI) o MISO (SISO), respectivamente, como el pin de entrada/salida de datos SPI simple. Cuando SPC0 = 0, BIDIROE no tiene significado o efecto.

0 Driver de Salida deshabilitado, así, el pin entrada/salida de datos SPI se comporta como una entrada. 1 Pin entrada/salida SPI habilitado como una salida. |

| 1

SPISWAI |

SPI Parada en Modo de Espera:

0 SPI Relojes continúan operando en modo de espera. 1 SPI Relojes se detienen cuando la MCU entra en modo de espera. |

| 0

SPC0 |

SPI Pin de Control 0: el bit SPC0 elige el modo bidireccional de cable simple. Si MSTR = 0 (modo esclavo), la SPI usa el pin MISO (SISO) para la transferencia de datos SPI bidireccional. Si MSTR = 1 (modo maestro), La SPI usa el pin MOSI (MOMI) para la transferencia de datos SPI bidireccional. Cuando SPC0 = 1, BIDIROE es utilizado para habilitar o deshabilitar el driver de salida para el pin entrada/salida SPI bidireccional simple.

0 SPI usa pines separados para el dato de entrada y el dato de salida. 1 SPI configurado para operaciones bidireccionales de cable simple. |

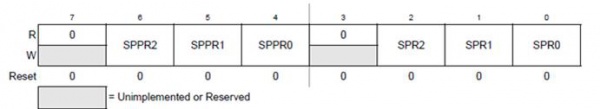

Registro de Tasa de Baudios de la SPI (SPIxBR)

Este registro se utiliza para colocar un pre-escalar y un divisor de tasa de bit para un SPI maestro. Este registro puede ser leído o escrito en cualquier momento.

| Bits | Descripción |

|---|---|

| 6:4

SPPR [2:0] |

SPI Divisor de pre-escala de Tasa de Baudios: Este campo de tres bits selecciona uno de ocho divisores para el pre-escalar de Tasa de Baudios SPI. La entrada de este pre-escalar es el reloj de Tasa de bus (BUSCLK). La salida de este pre-escalar dirige la entrada del divisor de Tasa de Baudios SPI. |

| 2:0

SPR [2:0] |

SPI Divisor de Tasa de Baudios: Este campo de tres bits selecciona uno de ocho divisores para el divisor de velocidad de transferencia SPI. La entrada a este divisor viene del pre-escalar de Tasa de Baudios SPI. La salida de este divisor es el bit de Tasa de reloj SPI para modo maestro. |

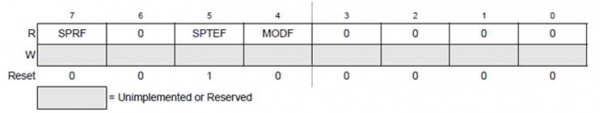

Registro de Estados de la SPI (SPIxS)

Este registro tiene tres bits de estado de solo lectura. Los bits 6, 3, 2, 1 y 0 no están implementados y siempre leen Zero. La escritura no tiene ningún significado o efecto.

| Bits | Descripción |

|---|---|

| 7

SPRF |

SPI Bandera de Buffer de lectura lleno: SPRF es puesto en la complementación de una transferencia para indicar que el dato recibido puede ser leído desde el registro de datos de la SPI (SPIxD). SPRF es limpiado por una lectura SPRF mientras este es colocado, entonces lee el registro de datos de la SPI.

0 No hay dato habilitado en el buffer de dato recibido. 1 Hay dato habilitado en el buffer de dato recibido. |

| 5

SPTEF |

SPI Bandera de Buffer de Transmisión vacío: Este bit es encendido cuando hay un espacio en el bus de transmisión de datos. Es limpiado por la lectura SPIxS con SPTEF encendido, seguido por la escritura de un valor de dato en el buffer de trasmisión en SPIxD. SPIxS debe ser leído con SPTEF = 1 antes de la escritura de dato de SPIxD o dicha escritura SPIxD será ignorada. SPTEF genera una solicitud de interrupción de CPU SPTEF si el bit SPTIE en SPIxC1 también esta encendido. SPTEF es automáticamente encendido cuando un byte de dato transfiere desde el buffer de transmisión hasta el registro de corrimiento. Para un idle SPI (sin dato en el buffer de transmisión o el registro de corrimiento y sin ninguna transferencia en proceso), el dato escrito de SPIxD es transferido del corredor inmediatamente, así, SPTEF es encendido entre dos ciclos de bus permitiendo a un segundo valor de dato de 8-bits ser solicitado dentro del buffer de transmisión. Después de completar la transferencia del valor en el registro de corrimiento, el valor solicitado desde el buffer de transmisión será movido automáticamente al corredor y SPTEF será encendido para indicar que hay un espacio para nuevos datos en el buffer de transmisión. Si no hay un nuevo dato esperando en el buffer de transmisión, SPTEF simplemente permanece encendido y no hay movimientos de datos desde el buffer hacia el corredor.

0 Buffer de Transmisión SPI no vacío. 1 Buffer de Transmisión SPI vacío. |

| 4

MODF |

Bandera de Fallo en Modo Maestro: MODF es encendido si la SPI es configurada como un maestro y la entrada Slave Select va bajo, indicando que algún otro dispositivo SPI es también como un maestro. El pin (SS) se comporta como una entrada de error en modo de fallo solo cuando MSTR = 1, MODFEN = 1 y SSOE = 0; Por otra parte, MODF nunca será encendido. MODF es limpiado leyendo MODF mientras este es 1, entonces escribe del registro SPI de control 1 (SPIxC1).

0 No hay error en modo de fallo. 1 Error en modo de fallo detectado. |

Registro de Datos de la SPI (SPIxD)

Las lecturas de este registro retornan el dato leído desde el buffer de dato recibido. Escrituras de este registro escriben el dato en el buffer de transmisión de dato. Cuando la SPI es configurada como un maestro, escribir datos del buffer de transmisión de datos inicia una transferencia SPI.

El dato no puede ser escrito desde el buffer de transmisión de dato antes de que la bandera de buffer de transmisión SPI vacío (SPTEF) esté encendida, indicando que hay espacio en el buffer de transmisión para solicitar un nuevo byte de transmisión. El dato puede ser leído desde SPIxD en cualquier momento después de que SPRF es encendido y antes de que otra transferencia haya finalizado. Una falla de lectura de dato fuera del buffer de dato recibido antes de que una nueva transferencia finalice causa una recepción de condición de sobrecorrida y el dato desde la nueva transferencia se pierde.

Descripción funcional de la SPI

Una transferencia SPI se inicia chequeando si la bandera del buffer de transmisión está vacía (SPTEF = 1) y escribiendo un byte de dato en el registro de datos SPI (SPIxD) en el dispositivo maestro SPI. Cuando el registro de corrimiento SPI está habilitado, este byte de dato se mueve desde el buffer de transmisión de dato al corredor, SPTEF se enciende para indicar que hay un espacio en el buffer para solicitar una transmisión de carácter, si se decide, y la transferencia serial SPI inicia.

Durante la transferencia SPI, el dato es leído en el pin MISO en un ciclo del reloj (SPSCK) y corrido, cambiando el valor del bit en el pin MOSI medio ciclo de reloj después. Después de ocho ciclos de reloj, el dato que estaba en el registro de corrimiento del maestro ha sido corrido fuera del pin MOSI hacia el esclavo mientras los 8-bits de dato fueron corridos en el pin MISO dentro del registro de corrimiento del maestro. Al final de esa transferencia, el byte de dato recibido es movido desde el corredor hacia adentro del buffer de dato recibido y SPRF se enciende para indicar que el dato puede ser leído a través de SPIxD. Si otro byte de dato esta en espera en el buffer de transmisión al final de una transferencia, este es movido hacia adentro del corredor, SPTEF se enciende e inicia una nueva transferencia.

Normalmente, un dato SPI se transfiere con el bit más significativo primero (MSB). Si el modo bit menos significativo primero está habilitado, el bit LSBFE se enciende y el dato SPI es corrido con LSB primero. Cuando la SPI es configurada como esclavo, su pin (SS) debe ser pasado a nivel bajo antes de que una transferencia inicie y el (SS) debe quedarse en dicho nivel a lo largo de la transferencia. Si un formato reloj donde CPHA = 0 es seleccionado, (SS) debe ser llevado a un “1” lógico entre transferencias sucesivas. Si CPHA = 1, (SS) puede permanecer bajo entre transferencias sucesivas. Debido a que el transmisor y el receptor es doble buffereado, un segundo byte, en adición al byte que está siendo corrido, puede ser solicitado dentro del buffer de transmisión de dato y un caracter recibido previamente puede estar en el buffer de dato recibido mientras uno nuevo está siendo corrido dentro del buffer. La bandera SPTEF indica cuándo el buffer de transmisión tiene espacio para un nuevo caracter. La bandera SPRF indica cuándo un caracter recibido esta disponible en el buffer de dato recibido. El caracter recibido debe ser leído fuera del buffer de recepción (leer SPIxD) antes de que la nueva transferencia finalice o se reciba como resultado de error de sobrecorrida. En el caso de recibir un sobre corrimiento, el nuevo dato se pierde debido a que el buffer de recepción todavía contiene el caracter previo y no estaba listo para aceptar un nuevo dato. No hay indicación para tal condición de sobrecorrida, entonces el diseñador del sistema de aplicación debe asegurarse de que el dato previo haya sido leído desde el buffer de recepción antes de que inicie una nueva transferencia.

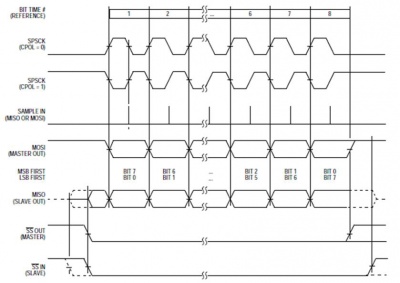

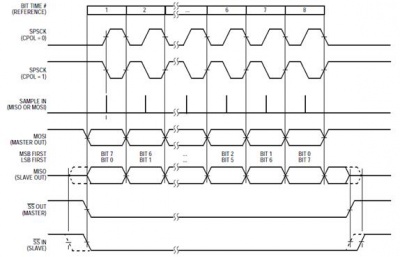

Tiempos del Reloj del SPI

Para acomodar la variedad de extensión de seriales periféricos síncronos desde diferentes diseños, el sistema SPI tiene un bit de prioridad de reloj (CPOL) y un bit de control de fase del reloj (CPHA) para seleccionar uno de dos formatos de reloj para transferencias de datos. CPOL inserta selectivamente un inversor en serie con el reloj. CPHA elige entre dos diferentes relaciones de fases de reloj entre el reloj y el dato.

La figura que se presenta a continuación muestra los formatos de reloj cuando CPHA = 1. En el top de la figura, los tiempos de 8-bits se muestran para referencia con el bit 1 iniciando en la primera carga de SPSCK y el bit 8 terminando medio ciclo SPSCK después de dieciséis cargas de SPSCK. Las líneas de bit más significativo primero y bit menos significativo primero muestran el orden de bits de dato SPI dependiendo de lo colocado en LSBFE. Ambas variaciones de polaridad de SPSCK se muestran, pero solo una de estas formas de onda es aplicada para una transferencia específica, dependiendo del valor en CPOL. La forma de onda SAMPLE IN se aplica a la entrada MOSI de un esclavo o a la entrada MISO de un maestro. La forma de onda MOSI se aplica al pin de salida MOSI desde un maestro y la forma de onda MISO se aplica a la salida MISO desde un esclavo. La forma de onda (SS) ̅ OUT se aplica a la salida Slave Select desde un maestro (provista por MODFEN y SSOE = 1). La salida (SS) ̅ del maestro pasa de activo a bajo medio ciclo SPSCK antes de iniciar la transferencia y pasa de nuevo a alto al final del tiempo del octavo bit de transferencia. La forma de onda (SS) ̅ IN se aplica a la entrada Slave Select de un esclavo.

Cuando CPHA = 1, el esclavo comienza a conducir su salida MISO cuando (SS) ̅ pasa a activo bajo, pero el dato no esta definido hasta el primer planco de SPSCK. El primer flanco de SPSCK corre el primer bit de dato desde el shifter hacia la salida MOSI del maestro y hacia la salida MISO del esclavo. El siguiente flanco del SPSCK causa que tanto el maestro como el esclavo muestreen el valor del bit de dato en sus entradas MISO y MOSI, respectivamente. En el tercer flanco de SPSCK, el shifter SPI corre una posición de bit, dicho corrimiento influye en el valor del bit que fue muestreado, y corre el segundo valor de bit de dato fuera de otro fin de corrimiento a las salidas MOSI y MISO de maestro y esclavo, respectivamente. Cuando CHPA = 1, la entrada (SS) del esclavo no es requerida para ponerse en su alto nivel inactivo entre transferencias.

La figura a la derecha muestra los formatos de reloj cuando CPHA = 0. En la parte superior de la figura, los tiempos del bit 8 se muestran para referenciar con un bit el inicio mientras el esclavo es seleccionado ((SS) IN pasa a bajo), y el bit 8 finaliza en el último flanco de SPSCK. Las líneas de bit más significativo primero y de bit menos significativo primero muestran el orden de bits de dato SPI dependiendo de las configuraciones en LSBFE. Ambas variaciones de la polaridad SPSCK son mostrados, pero solo una de estas formas de onda se aplica para una transferencia específica, dependiendo del valor en CPOL. La forma de onda SAMPLE IN se aplica a la entrada MOSI del esclavo o a la entrada MISO del maestro. La forma de onda MOSI se aplica al pin de salida MOSI desde un maestro y la forma de onda MISO se aplica a la salida MISO desde un esclavo. La forma de onda (SS) OUT se aplica a la salida Slave Select desde un maestro (provista por MODFEN y SSOE = 1). La salida (SS) del maestro va a bajo activo al comienzo del primer tiempo de bit de una transferencia y va de vuelta a alto medio ciclo de SPSCK después del final del tiempo del octavo bit de la transferencia. La forma de onda (SS) IN se aplica a la entrada Slave Select del esclavo. Cuando CPHA = 0, el esclavo comienza a conducir su salida MISO con el primer valor de bit de dato (MSB o LSB dependiendo de LSBFE) cuando (SS) cae a bajo activo.el primer flanco de SPSCK causa que, tanto el maestro como el esclavo, muestreen los valores de bit de dato en sus entradas MISO y MOSI, respectivamente. En el segundo flanco de SPSCK, el shifter SPI corre una posición de bit, lo cual, corre en un valor del bit que acababa de ser muestreado y corre el segundo valor de bit de dato fuera de otro fin del shifter a las salidas MOSI y MISO de maestro y esclavo, respectivamente. Cuando CPHA = 0, la entrada de (SS) del esclavo debe ir a inactividad de alto nivel entre transferencias.

Interrupciones del SPI

Hay tres bits banderas, dos bits mascaras de interrupción y un vector de interrupción asociado con el sistema SPI. La Mascara de Habilitación de Interrupción SPI (SPIE) habilita interrupciones desde la bandera de recepción llena SPI (SPRF) y la Bandera de Modo de Fallo (MODF). La Mascara de Habilitación de Interrupción de Transmisión SPI (SPTIE) habilita interrupciones desde la bandera de buffer de transmisión vacío SPI (SPTEF). Cuando uno de los bits bandera y el bit mascara de interrupción asociado a este se encienden, una interrupción de Hardware solicitada es enviada al CPU. Si los bits mascaras de interrupción están limpios, el Software puede hacer encuesta al bit bandera asociado en lugar de utilizar interrupciones. La rutina de servicio de interrupción SPI (ISR) podría chequear los bits bandera para determinar qué evento causó la interrupción. La rutina de servicio podría también limpiar los bits bandera antes de correr desde ISR (usualmente cerca del comienzo de la ISR).

Modo de Detección de Fallos

Un modo de fallo ocurre y la bandera de modo de fallo se enciende cuando un dispositivo maestro SPI detecta un error en el pin (SS) (provisto del pin (SS) configurado como una señal de entrada en modo de fallo). El pin (SS) es configurado para ser una señal de entrada en modo de fallo cuando MSTR = 1, habilitar el modo de fallo es colocar (MODFEN = 1), y salida Slave Select habilitada es limpiar (SSOE = 0) Una característica de detección en modo de fallo puede ser utilizada en un sistema donde más de un dispositivo SPI pudiera convertirse en un maestro al mismo tiempo. El error es detectado cuando un pin (SS) maestro esta en bajo, indicando que algún otro dispositivo SPI está tratando de dirigir a ese maestro como si fuera un esclavo. Esto podría indicar un conflicto de controlador de salida inofensivo, entonces, el modo de fallo lógico es diseñado para deshabilitar todos los controladores de salida SPI cuando algún error es detectado.

Cuando en modo de fallo es detectado, MODF se enciende y MSTR es limpiado para cambiar la configuración SPI de vuelta a modo esclavo. Los controladores de salida en SPSCK, MOSI y MISO (si no están en modo bidireccional) son deshabilitados. MODF es limpiado cuando es leído mientras está encendido, entonces se escribe en el registro de control 1 SPI (SPIxC1). El Software usuario podría verificar si la condición de error ha sido corregida antes de cambiar el SPI de vuelta a modo maestro.

Protocolos de Configuración de la SPI

Protocolo de Configuracion de la SPI en modo maestro

Para configurar la SPI en modo maestro se deben tomar en cuenta los siguientes aspectos:

• En el programa principal se envía un Byte a la SPI.

• En la MCU, se inicializa la MCU, se deshabilita el Watchdog y se habilita el módulo de reloj de la SPI.

• En la unidad GPIO, se configuran los puertos PTE como salidas y el puerto PTD4 como señal de salida SS.

• En la Interfaz de serial periférico, se configura el módulo.

• En la ISR, se limpian las banderas del módulo.

Con el siguiente fragmento de código se procede a deshabilitar el Watchdog, habilitar las opciones de Reseteo y los Pines de Background:

void MCU_Init(void) {

SOPT1 = 0x23; // Deshabilitamos el Watchdog. Se habilita el Modo de Parada

// y los Pines de Background. Se habilita el Pin de Reseteo.

SCGC1 = 0x00; // Se deshabilita el Bus Reloj de los Periféricos que no se utilizan

SCGC2 = 0x02; // Habilitamos el Bus Reloj del Módulo SPI2.

}

La configuración de entradas/salidas de uso general se realiza habilitando los pines del puerto PTE, el protocolo SPI puede comunicar varios esclavos con un maestro. Para comunicar el maestro con un esclavo especifico la señal SS debe estar en bajo. el puerto PTD3 es configurado como la señal de salida SS y debe ser cambiada por Software utilizando GPIO:

void GPIO_Init(void) {

PTDDD = 0x04; // La Señal SS debe ser generada por Software utilizando GPIO.

PTEDD = 0xFF; // Se configura el Puerto PTE como salida.

PTED = 0x00; // Coloca Zeros en el Puerto PTE.

}

Para inicializar el módulo de Interfaz de serial periférico se utiliza el siguiente código:

void SPI_Init (void) {

SPI2BR = 0x75; // Se selecciona el mas alto divisor pre-escalar de Tasa de Baudios

// y el mas alto divisor de Tasa de Baudios.

SPI2C1 = 0xD0; // Se habilitan las interrupciones SPI, el sistema,

// y se selecciona el Modo Maestro.

SPI2C2 = 0x00; // Los pines para entrada y salida de datos son distintos.

}

A continuación se muestra el programa principal, en el cual se observa que, mientras se permanece en el ciclo infinito, un Byte es enviado por la SPI y el siguiente es enviado después del delay:

void main(void) {

UINT8 counter = 0;

MCU_Init(); // Esta función inicializa la MCU.

GPIO_Init(); // Esta función inicializa los puertos de la MCU.

SPI_Init(); // Esta función inicializa el modula SPI.

EnableInterrupts; // Se habilitan las interrupciones.

for(;;) {

delay(60000); // Esta es la Función Delay.

while (!SPI2S_SPTEF && !PTDD_PTDD3); // Se espera hasta que el buffer de

// transmisión este vació.

PTDD_PTDD3 = 0; // Aquí se coloca el Slave Select en bajo

SPI2D = counter; // Se pone en el buffer SPI un dato para

// enviarlo.

PTED = counter; // Se muestra el valor del contador en los Leds.

counter++; // Se incrementa el Contador.

} // Se cae en el Lazo Infinito.

// Recordar que siempre debe estar ejecutándose

// Esta Función.

}

A continuación se muestra la rutina de servicio de interrupciones, que se utiliza cuando un Byte es enviado por un esclavo hacia el maestro:

void interrupt VectorNumber_Vspi2 SPI_ISR(void) {

// Vector de Interrupcion SPI numero = 12 (S08).

// Vector de Interrupcion SPI numero = 74 (V1).

UINT8 temp;

while (PTDD_PTDD0); // Espera por el Reloj y no retorna un valor

// predeterminado.

PTDD_PTDD3 = 1; // Coloca el Slave Select en Alto.

temp = SPI2S; // Limpia las Banderas de Registros.

temp = SPI2D; // Lee el Registro Dato para limpiar la

// Bandera de Recepción.

}

Protocolo de Configuración de la SPI en modo esclavo

Para configurar la SPI en modo esclavo se deben tomar en cuenta los siguientes aspectos:

• En el programa principal se espera a que ocurra una interrupción SPI.

• En la MCU, se inicializa la MCU, se deshabilita el Watchdog y se habilita el módulo de reloj de la SPI.

• En la unidad GPIO, se configuran los puertos PTE como salidas.

• En la Interfaz de serial periférico, se configura el módulo.

• En la ISR, se muestra el dato recibido en el puerto PTE.

Este modo es parecido al modo maestro, la diferencia se aprecia en el hecho de que el dispositivo esta configurado como esclavo y solo recibe un Byte y lo muestra en el puerto E. El código de inicialización para el modulo SPI seria:

void SPI_Init (void) {

SPI2BR = 0x75; // Se selecciona el divisor de pre-escala de Tasa de Baudios mas Alto.

// y el Divisor de Tasa de Baudios mas Alto.

SPI2C1 = 0xC4; // Se habilitan las Interrupciones SPI, el sistema y se selecciona el Modo Esclavo.

SPI2C2 = 0x00; // Los Pines de Entrada/Salida de datos son distintos.

}

Y esta es la rutina de servicio de interrupciones, la cual se utiliza cuando un Byte se envía por un maestro a un esclavo:

void interrupt VectorNumber_Vspi2 SPI_ISR(void) {

UINT8 temp, buffer;

while (PTDD_PTDD0);

temp = SPI2S; // Se limpia el Registro de Banderas.

buffer = SPI2D; // Se lee en Registro de Datos para limpiar la Bandera de Recepción.

PTED = buffer;

}

Referencias Consultadas

Contributors

AK, Anairam, Any Isabel Rodriguez, JCaceres, Luis E Santana P, Minleung, Misato, Racuna