Diferencia entre revisiones de «Registros IIC»

(Página creada con «hhshs») |

|||

| Línea 1: | Línea 1: | ||

| − | + | ||

| + | La dirección del IIC tiene 10-bit de direccionamiento, 0x11110, se utilizan los primeros 5 bits del primer byte de dirección. Se pueden tener varias combinaciones de leer / escribir, estos formatos son posibles con cambios en los 10-bit de direccionamiento. | ||

| + | |||

| + | |||

| + | '''Definición de Registros:''' Todos los registros y bits de control del IIC se especifican sólo por sus nombres, ya que Freescale proporciona una cabecera para trasladar los nombres a las apropiadas direcciones absolutas. | ||

| + | |||

| + | *'''IIC Address Register (IICxA)''' | ||

| + | |||

| + | |||

| + | [[Archivo:IICxA.png]] | ||

| + | |||

| + | Esta dirección de registro tiene 8 bits donde los 7 de la izquierda a la derecha es la Slave Address(Dirección del Esclavo). Esta dirección contiene la dirección del esclavo que se utiliza el modulo IIC. Este campo es usado en el esquema de dirección de siete bits, donde son los 7 bits más bajos del esquema de direcciones de 10 bits. | ||

| + | |||

| + | |||

| + | |||

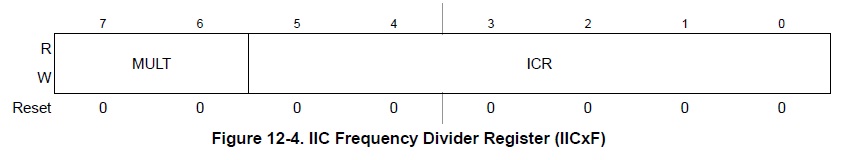

| + | *'''IIC Frequency Divider Register (IICxF)''' | ||

| + | |||

| + | [[Archivo:IICxFreg.jpg]] | ||

| + | |||

| + | Esta dirección de registro tiene 8 bits, donde los bits 7 y 8 son el factor multiplicador(MULT),los 2 bits MULT se usan para definir el factor mul, este factor se utiliza junto con el SCL para generar la baud rate ó la velocidad de transmisión del IIC. Esto 2 bit MULT definen el factor mul de la siguiente manera: | ||

| + | |||

| + | 00 mul = 01 | ||

| + | |||

| + | 01 mul = 02 | ||

| + | |||

| + | 10 mul = 04 | ||

| + | |||

| + | 11 Reserved | ||

| + | |||

| + | Los últimos cinco bits de la izquierda a la derecha de esta dirección de registro son para la velocidad del reloj (ICR), estos bits se utiliza para determinar del reloj de bus para la selección de la tasa de bits. | ||

| + | |||

| + | Los bits MULT y los bits del clock rate se usan para calcular la velocidad de transmisión, el tiempo de retención SDA, el tiempo de inicio del SCL y el tiempo de detenimiento del SCL. Cada una se puede calcular de la siguiente manera: | ||

| + | |||

| + | -IIC baud rate = bus speed (Hz)/(mul * SCL divider) | ||

| + | |||

| + | -SDA hold time = bus period (s) * mul * SDA hold value | ||

| + | |||

| + | -SCL Start hold time = bus period (s) * mul * SCL Start hold value | ||

| + | |||

| + | -SCL Stop hold time = bus period (s) * mul * SCL Stop hold value | ||

| + | |||

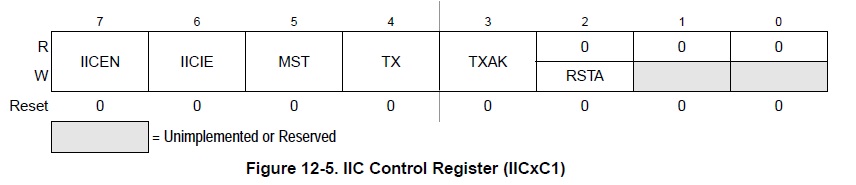

| + | *'''IIC Control Register (IICxC1)''' | ||

| + | |||

| + | |||

| + | [[Archivo:IICxC1.jpg]] | ||

| + | |||

| + | Este registro de control esta definido por 8 bits, el bit 7 es el de habilitación (IICEN) donde con 0 el IIC no esta habilitado y con 1 el IIC esta habilitado. | ||

| + | |||

| + | El siguiente bit "6" es el de la habilitación de interrupción(IICIE), este determina cuando una interrupción fue solicitada, con 0 no fue solicitada la habilitación y con 1 si fue solicitada la interrupción. | ||

| + | |||

| + | El 5 bit es el del modo maestro seleccionado (MST), con este bit si se cambia de de 0 a 1 cuando la señal se genera en el bus y luego se selecciona el modo maestro. Cuando este bit cambia de 1 a 0 se genera una señal de detención o STOP, y el modo de operación cambia de maestro a esclavo. | ||

| + | |||

| + | 0 Slave mode. | ||

| + | |||

| + | 1 Master mode. | ||

| + | |||

| + | El 4 bit es el modo de transmicion seleccionado (TX), con este bit se selecciona el modo de transferencia entre el esclavo y el maestro.En el modo maestro de este bit debe establecerse de acuerdo con el tipo de transferencia requerida. Por lo tanto, para los ciclos de direcciones, este bit siempre será alto.Cuando se establezca en modo esclavo este bit debe establecerse por el software de acuerdo con el bit de SRW en el registro de estado. | ||

| + | |||

| + | Recibe 0. | ||

| + | |||

| + | Transmite 1. | ||

| + | |||

| + | El tercer bit es el de reconocimiento de transmicion habilitada (TXAK), este bit reconoce la transmitir habilitada Este bit especifica el valor llevado a la SDA durante el reconocimiento de datos en ciclos, para tanto receptor maestro como receptor esclavo. | ||

| + | |||

| + | 0 Se envia una señal de recepción al bus después de recibir un data byte. | ||

| + | |||

| + | 1 Ninguna señal de reconocimiento es enviada | ||

| + | |||

| + | El segundo es el de repetir inicio(RSTA) Escribir un 1 en este bit generará una condición de START repetida siempre y cuando sea el maestro. Este bit siempre será leído como bajo. El intento que se repita en el momento equivocado resultará en la pérdida de arbitraje. | ||

| + | |||

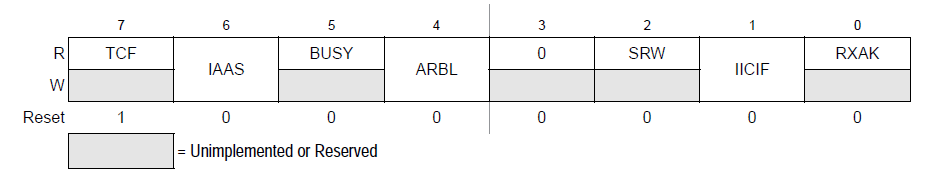

| + | *'''IIC Status Register (IICxS)''' | ||

| + | |||

| + | [[Archivo:IICxS.png]] | ||

| + | |||

| + | Este registro tiene 8 bits donde el bit 7 se llama bandera de transferencia completa(TCF), este bit se establece en la finalizacion de la transferencia de bytes.Tenga en cuenta que este bit sólo es válida durante o inmediatamente después de una transferencia al módulo IIC o desde el modulo IIC.El bit de TCF se elimina mediante la lectura del registro IICxD en el modo receptor o escribiendo en IICxD en el modo de transmisión. | ||

| + | |||

| + | 0 Transfer in progress. | ||

| + | |||

| + | 1 Transfer complete. | ||

| + | |||

| + | El sexto bit es el de dirigido como un esclavo(IAAS), esté bit se establece cuando la dirección de la llamada coincide con la dirección del esclavo programado, o cuando el bit GCAEN se establece y se recibe una llamada general.Escribir el registro IICxC borra este bit. | ||

| + | |||

| + | El quinto bit es el de bus ocupado(BUSY), indica el estado del bus independientemente del esclavo o del maestro. El bit BUSY está | ||

| + | activa cuando se detecta una señal de arranque y se apaga cuando se detecta una señal de STOP. | ||

| + | |||

| + | 0 bus está inactivo. | ||

| + | |||

| + | 1 bus está ocupado. | ||

| + | |||

| + | El cuarto bit es el de arbitraje perdido(ARBL), este bit es activado por hardware cuando se pierde el procedimiento de arbitraje. El bit debe ser | ||

| + | despejado por software, escribiendo un 1 a la misma. | ||

| + | |||

| + | 0 funcionamiento de bus estándar. | ||

| + | |||

| + | 1 La pérdida de arbitraje. | ||

| + | |||

| + | El 2 bit es el de esclavo de lectura/escritura(SRW),cuando es llamado como un esclavo del SRW bits indica el valor del bit de comando R / W de | ||

| + | la dirección solicitante y la envía al maestro. | ||

| + | |||

| + | 0 Esclavo recibir, por escrito maestro a esclavo. | ||

| + | |||

| + | 1 Esclavo de transmisión, maestra de lectura del esclavo. | ||

| + | |||

| + | El bit 1 es el de bandera de interrupcion del ICC (IICIF), se establece cuando una interrupción está pendiente. Este bit debe ser limpiado por software, escribiendo un 1 en la rutina de interrupción. Uno de los siguientes eventos pueden establecer el bit IICIF: | ||

| + | |||

| + | • Una transferencia de bytes completa | ||

| + | • Ajuste de la dirección del esclavo a la dirección llamando | ||

| + | • Arbitraje perdió | ||

| + | 0 No se interrumpen en espera. | ||

| + | 1 interrupción pendiente | ||

| + | |||

| + | el bit 0 Recibe Reconocimiento(RXAK),cuando es baja, indica una señal de confirmación se ha recibido después | ||

| + | la realización de un byte de la transmisión de datos en el bus. Si el bit es alto RXAK significaría que no se | ||

| + | se detecta la señal. | ||

| + | |||

| + | 0 Reconocer recibido. | ||

| + | |||

| + | 1 No se reconocen recibido. | ||

| + | |||

| + | *'''IIC Data I/O Register (IICxD)''' | ||

| + | |||

| + | [[Archivo:IICxD.png]] | ||

| + | |||

| + | Esta dirección de registro tiene 8 bits donde todos los bits dan la informacion de DATA, DATA en modo maestro de transmisión, hace que cuando datos son escritos en el IICxD, se inicie una transferencia de los datos, el bit más significativo se envía primero. En modo maestro de recepción, la lectura de este registro inicia la recepción del siguiente byte de datos. | ||

| + | |||

| + | Cuando se está cambiando el modo maestro de recepción, el modo de inspección debe ser cambiado antes de leer el registro IICxD para evitar una iniciación involuntaria de un maestro recibiendo la transferencia de datos. | ||

| + | |||

| + | En el modo esclavo, las mismas funciones están disponibles después de haberse producido una coincidencia de direcciones. | ||

| + | |||

| + | Tenga en cuenta que el bit TX en IICxC debe reflejar correctamente la dirección deseada de transferencia de los modos maestro y esclavo para que empiece la transmisión. Por ejemplo, si la IIC se configura para modo maestro de transmisión, pero se desea estar en modo maestro de recepción, entonces la lectura de la IICxD no iniciará la recepción. | ||

| + | |||

| + | La lectura de la IICxD devolverá el último byte recibido, mientras que la IIC está configurada tanto en modo maestro de recepción o modo esclavo de recepción. El IICxD no refleja todos los bytes que se transmite en el bus IIC, ni puede verificar el software que un byte se ha escrito para IICxD correctamente leyendo de nuevo. | ||

| + | |||

| + | En el modo maestro de transmisión, el primer byte de los datos escritos en IICxD siguiente afirmación de MST se utiliza para la transferencia de la dirección y debería formar parte de la dirección de llamada (en el bit 7 al bit 1) concatenado con el bit deseado R/W (en la posición de bit 0) | ||

| + | |||

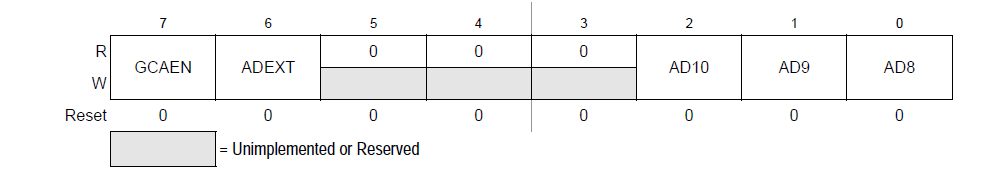

| + | *'''IIC Control Register 2 (IICxC2)''' | ||

| + | |||

| + | [[Archivo:IICxC2.png]] | ||

| + | |||

| + | Esta dirección de registro tiene 8 bits, donde el bit primer bit de izquierda a derecha es el de Dirección general de llamada a activar (GCAEN), donde este bit activara o desactivara la dirección de llamada general. | ||

| + | |||

| + | El bit siguiente al bit GCAEN es el bit de Extensión de dirección (ADEXT), donde controla el numero de bits usado para la dirección del esclavo. | ||

| + | |||

| + | Y los últimos tres bits de los 8 de IICxC2 son de la dirección del esclavo (AD[10:8]). | ||

| + | |||

| + | En el esquema de direcciones de 10 bits la AD [10: 8] contiene los tres bits superiores de la dirección del esclavo. Este campo sólo es válido cuando se establece el bit ADEXT. | ||

Revisión del 12:01 1 jul 2016

La dirección del IIC tiene 10-bit de direccionamiento, 0x11110, se utilizan los primeros 5 bits del primer byte de dirección. Se pueden tener varias combinaciones de leer / escribir, estos formatos son posibles con cambios en los 10-bit de direccionamiento.

Definición de Registros: Todos los registros y bits de control del IIC se especifican sólo por sus nombres, ya que Freescale proporciona una cabecera para trasladar los nombres a las apropiadas direcciones absolutas.

- IIC Address Register (IICxA)

Esta dirección de registro tiene 8 bits donde los 7 de la izquierda a la derecha es la Slave Address(Dirección del Esclavo). Esta dirección contiene la dirección del esclavo que se utiliza el modulo IIC. Este campo es usado en el esquema de dirección de siete bits, donde son los 7 bits más bajos del esquema de direcciones de 10 bits.

- IIC Frequency Divider Register (IICxF)

Esta dirección de registro tiene 8 bits, donde los bits 7 y 8 son el factor multiplicador(MULT),los 2 bits MULT se usan para definir el factor mul, este factor se utiliza junto con el SCL para generar la baud rate ó la velocidad de transmisión del IIC. Esto 2 bit MULT definen el factor mul de la siguiente manera:

00 mul = 01

01 mul = 02

10 mul = 04

11 Reserved

Los últimos cinco bits de la izquierda a la derecha de esta dirección de registro son para la velocidad del reloj (ICR), estos bits se utiliza para determinar del reloj de bus para la selección de la tasa de bits.

Los bits MULT y los bits del clock rate se usan para calcular la velocidad de transmisión, el tiempo de retención SDA, el tiempo de inicio del SCL y el tiempo de detenimiento del SCL. Cada una se puede calcular de la siguiente manera:

-IIC baud rate = bus speed (Hz)/(mul * SCL divider)

-SDA hold time = bus period (s) * mul * SDA hold value

-SCL Start hold time = bus period (s) * mul * SCL Start hold value

-SCL Stop hold time = bus period (s) * mul * SCL Stop hold value

- IIC Control Register (IICxC1)

Este registro de control esta definido por 8 bits, el bit 7 es el de habilitación (IICEN) donde con 0 el IIC no esta habilitado y con 1 el IIC esta habilitado.

El siguiente bit "6" es el de la habilitación de interrupción(IICIE), este determina cuando una interrupción fue solicitada, con 0 no fue solicitada la habilitación y con 1 si fue solicitada la interrupción.

El 5 bit es el del modo maestro seleccionado (MST), con este bit si se cambia de de 0 a 1 cuando la señal se genera en el bus y luego se selecciona el modo maestro. Cuando este bit cambia de 1 a 0 se genera una señal de detención o STOP, y el modo de operación cambia de maestro a esclavo.

0 Slave mode.

1 Master mode.

El 4 bit es el modo de transmicion seleccionado (TX), con este bit se selecciona el modo de transferencia entre el esclavo y el maestro.En el modo maestro de este bit debe establecerse de acuerdo con el tipo de transferencia requerida. Por lo tanto, para los ciclos de direcciones, este bit siempre será alto.Cuando se establezca en modo esclavo este bit debe establecerse por el software de acuerdo con el bit de SRW en el registro de estado.

Recibe 0.

Transmite 1.

El tercer bit es el de reconocimiento de transmicion habilitada (TXAK), este bit reconoce la transmitir habilitada Este bit especifica el valor llevado a la SDA durante el reconocimiento de datos en ciclos, para tanto receptor maestro como receptor esclavo.

0 Se envia una señal de recepción al bus después de recibir un data byte.

1 Ninguna señal de reconocimiento es enviada

El segundo es el de repetir inicio(RSTA) Escribir un 1 en este bit generará una condición de START repetida siempre y cuando sea el maestro. Este bit siempre será leído como bajo. El intento que se repita en el momento equivocado resultará en la pérdida de arbitraje.

- IIC Status Register (IICxS)

Este registro tiene 8 bits donde el bit 7 se llama bandera de transferencia completa(TCF), este bit se establece en la finalizacion de la transferencia de bytes.Tenga en cuenta que este bit sólo es válida durante o inmediatamente después de una transferencia al módulo IIC o desde el modulo IIC.El bit de TCF se elimina mediante la lectura del registro IICxD en el modo receptor o escribiendo en IICxD en el modo de transmisión.

0 Transfer in progress.

1 Transfer complete.

El sexto bit es el de dirigido como un esclavo(IAAS), esté bit se establece cuando la dirección de la llamada coincide con la dirección del esclavo programado, o cuando el bit GCAEN se establece y se recibe una llamada general.Escribir el registro IICxC borra este bit.

El quinto bit es el de bus ocupado(BUSY), indica el estado del bus independientemente del esclavo o del maestro. El bit BUSY está activa cuando se detecta una señal de arranque y se apaga cuando se detecta una señal de STOP.

0 bus está inactivo.

1 bus está ocupado.

El cuarto bit es el de arbitraje perdido(ARBL), este bit es activado por hardware cuando se pierde el procedimiento de arbitraje. El bit debe ser despejado por software, escribiendo un 1 a la misma.

0 funcionamiento de bus estándar.

1 La pérdida de arbitraje.

El 2 bit es el de esclavo de lectura/escritura(SRW),cuando es llamado como un esclavo del SRW bits indica el valor del bit de comando R / W de la dirección solicitante y la envía al maestro.

0 Esclavo recibir, por escrito maestro a esclavo.

1 Esclavo de transmisión, maestra de lectura del esclavo.

El bit 1 es el de bandera de interrupcion del ICC (IICIF), se establece cuando una interrupción está pendiente. Este bit debe ser limpiado por software, escribiendo un 1 en la rutina de interrupción. Uno de los siguientes eventos pueden establecer el bit IICIF:

• Una transferencia de bytes completa • Ajuste de la dirección del esclavo a la dirección llamando • Arbitraje perdió 0 No se interrumpen en espera. 1 interrupción pendiente

el bit 0 Recibe Reconocimiento(RXAK),cuando es baja, indica una señal de confirmación se ha recibido después la realización de un byte de la transmisión de datos en el bus. Si el bit es alto RXAK significaría que no se se detecta la señal.

0 Reconocer recibido.

1 No se reconocen recibido.

- IIC Data I/O Register (IICxD)

Esta dirección de registro tiene 8 bits donde todos los bits dan la informacion de DATA, DATA en modo maestro de transmisión, hace que cuando datos son escritos en el IICxD, se inicie una transferencia de los datos, el bit más significativo se envía primero. En modo maestro de recepción, la lectura de este registro inicia la recepción del siguiente byte de datos.

Cuando se está cambiando el modo maestro de recepción, el modo de inspección debe ser cambiado antes de leer el registro IICxD para evitar una iniciación involuntaria de un maestro recibiendo la transferencia de datos.

En el modo esclavo, las mismas funciones están disponibles después de haberse producido una coincidencia de direcciones.

Tenga en cuenta que el bit TX en IICxC debe reflejar correctamente la dirección deseada de transferencia de los modos maestro y esclavo para que empiece la transmisión. Por ejemplo, si la IIC se configura para modo maestro de transmisión, pero se desea estar en modo maestro de recepción, entonces la lectura de la IICxD no iniciará la recepción.

La lectura de la IICxD devolverá el último byte recibido, mientras que la IIC está configurada tanto en modo maestro de recepción o modo esclavo de recepción. El IICxD no refleja todos los bytes que se transmite en el bus IIC, ni puede verificar el software que un byte se ha escrito para IICxD correctamente leyendo de nuevo.

En el modo maestro de transmisión, el primer byte de los datos escritos en IICxD siguiente afirmación de MST se utiliza para la transferencia de la dirección y debería formar parte de la dirección de llamada (en el bit 7 al bit 1) concatenado con el bit deseado R/W (en la posición de bit 0)

- IIC Control Register 2 (IICxC2)

Esta dirección de registro tiene 8 bits, donde el bit primer bit de izquierda a derecha es el de Dirección general de llamada a activar (GCAEN), donde este bit activara o desactivara la dirección de llamada general.

El bit siguiente al bit GCAEN es el bit de Extensión de dirección (ADEXT), donde controla el numero de bits usado para la dirección del esclavo.

Y los últimos tres bits de los 8 de IICxC2 son de la dirección del esclavo (AD[10:8]).

En el esquema de direcciones de 10 bits la AD [10: 8] contiene los tres bits superiores de la dirección del esclavo. Este campo sólo es válido cuando se establece el bit ADEXT.