Diferencia entre revisiones de «MIPS»

| Línea 52: | Línea 52: | ||

Los diseños más recientes se basan en el R10000. El '''R12000''' ha sido fabricado con tecnología mejorada para comprimir el chip y operar a mayor velocidad de reloj. La revisión '''R14000''' permitía mayores frecuencias, soporte adicional para DDR SRAM en el chip externo de [[caché]] y un bus de datos ''front side'' de 200 MHz para un mejor transferencia. Las últimas versiones fueron llamadas '''R16000''' y '''R16000A''', caracterizándose por una mayor velocidad de reloj, caché L1 adicional y chips de menor tamaño en comparación con los anteriores. | Los diseños más recientes se basan en el R10000. El '''R12000''' ha sido fabricado con tecnología mejorada para comprimir el chip y operar a mayor velocidad de reloj. La revisión '''R14000''' permitía mayores frecuencias, soporte adicional para DDR SRAM en el chip externo de [[caché]] y un bus de datos ''front side'' de 200 MHz para un mejor transferencia. Las últimas versiones fueron llamadas '''R16000''' y '''R16000A''', caracterizándose por una mayor velocidad de reloj, caché L1 adicional y chips de menor tamaño en comparación con los anteriores. | ||

| + | |||

| + | == Enlaces de Interés == | ||

| + | * [[Medio:MIPS_Green_Card.pdf|Mips Green Card]] | ||

| + | |||

== Bibliografía == | == Bibliografía == | ||

* http://es.wikipedia.org/wiki/MIPS_(procesador) | * http://es.wikipedia.org/wiki/MIPS_(procesador) | ||

Revisión actual del 16:43 14 dic 2013

Con el nombre de MIPS (siglas de Microprocessor without Interlocked Pipeline Stages) se conoce a toda una familia de microprocesadores de arquitectura RISC desarrollados por MIPS Technologies.

Los diseños del MIPS son utilizados en la línea de productos informáticos de Silicon Graphics; en muchos sistemas embebidos; en dispositivos para Windows CE; routers Cisco; y videoconsolas como la Nintendo 64 o las PlayStation.

Las primeras arquitecturas MIPS fueron implementadas en 32 bits (generalmente rutas de datos y registros de 32 bits de ancho), si bien versiones posteriores fueron implementadas en 64 bits. Existen cinco revisiones compatibles hacia atrás del conjunto de instrucciones del MIPS, llamadas MIPS I, MIPS II, MIPS III, MIPS IV y MIPS 32/64. En la última de ellas, la MIPS 32/64 Release 2, se define a mayores un conjunto de control de registros. Así mismo están disponibles varias "extensiones", tales como la MIPS-3D, consistente en un simple conjunto de instrucciones Single Instruction Multiple Data (SIMD) en coma flotante dedicadas a tareas 3D comunes, la MDMX(MaDMaX) compuesta por un conjunto más extenso de instrucciones Single Instruction Multiple Data(SIMD)enteras que utilizan los registros de coma flotante de 64 bits, la MIPS16 que añade compresión al flujo de instrucciones para hacer que los programas ocupen menos espacio (presuntamente como respuesta a la tecnología de compresión Thumb de la arquitectura ARM) o la reciente MIPS MT que añade funcionalidades multithreading similares a la tecnología HyperThreading de los procesadores Intel Pentium 4.

Debido a que los diseñadores crearon un conjunto de instrucciones tan claro, los cursos sobre arquitectura de computadores en universidades y escuelas técnicas a menudo se basan en la arquitectura MIPS. El diseño de la familia de CPU's MIPS influiría de manera importante en otras arquitecturas RISC posteriores como los DEC Alpha.

Historia

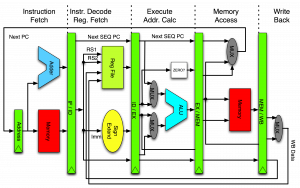

En 1981, un equipo liderado por John L. Hennessy en la Universidad de Stanford comenzó a trabajar en lo que se convertiría en el primer procesador MIPS. La idea básica era mejorar drásticamente el rendimiento mediante el uso de la segmentación, una técnica que ya era entonces muy conocida pero también difícil de implementar. Su funcionamiento puede resumirse en que la ejecución de una instrucción es dividida en varias etapas, comenzando la "etapa 1" de una instrucción antes de que haya finalizado la ejecución de la instrucción anterior. En contraste, los diseños tradicionales esperaban la finalización por completo de una instrucción antes de pasar a la siguiente, de modo que grandes áreas de la CPU permanecían inactivas mientras el proceso continuaba. Además, la frecuencia de reloj de toda la CPU venía dictada por la latencia del ciclo completo, en lugar de por el llamado camino crítico, latencia de la etapa de segmentación que más tarda en completarse.

Otra de las grandes barreras a superar por la segmentación era la necesidad de introducir bloqueos para poder asegurarse de que las instrucciones que necesitan varios ciclos de reloj para completarse dejan de cargar datos desde los registros de segmentación. Estos bloqueos pueden durar cantidades de tiempo considerables, y suponían una gran barrera a mejoras de velocidad posteriores. Por ello, uno de los principales aspectos del diseño del MIPS fue el marcarse como objetivo que todas las subfases (incluyendo el acceso a memoria) de todas las instrucciones tardasen un único ciclo en completarse, dejando así de ser necesarios los bloqueos, y permitiendo un rendimiento de un solo ciclo.

Aunque esta idea de diseño eliminó numerosas instrucciones útiles, destacando el hecho de que la multiplicación y la división necesitarían varias instrucciones, en conjunto se sabía que el rendimiento general del sistema sería drásticamente mejorado al poder funcionar los chips a frecuencias mucho mayores. Este ascenso de la velocidad sería difícil con la intervención de los bloqueos, pues el tiempo necesario es función del tamaño del chip y de la frecuencia de reloj: añadir el hardware necesario para evitarlos reduciría notablemente la velocidad del sistema.

La eliminación de estas instrucciones se convirtió en un tema polémico. Muchos observadores afirmaron que ese diseño (y los procesadores RISC en general) nunca superaría sus ambiciosas expectativas ("Si uno sencillamente sustituye la instrucción compleja de multiplicación por una simple serie de sumas, ¿dónde se produce el incremento de velocidad?"). Este análisis tan simplista ignoraba el hecho de que la velocidad del diseño residía en la segmentación, no en las instrucciones.

En 1984 Hennessy se convenció del futuro potencial comercial del diseño, dejando Stanford para formar MIPS Computer Systems. La empresa presentó su primer diseño, el R2000, en 1985, siendo mejorado con el R3000 de 1988. Estas CPU's de 32 bits fueron la base de la compañía durante los 80, y fueron empleadas principalmente en algunas series de estaciones de trabajo de SGI. Estos diseños comerciales se diferenciaron de los de investigación académica de Stanford en aspectos como la implementación de la mayoría de los bloqueos con hardware y el proporcionar instrucciones completas para la multiplicación y la división, entre otros.

En 1991 MIPS presentó su primer procesador de 64 bits, el R4000. Sin embargo, MIPS tuvo dificultades financieras en su lanzamiento al mercado. El diseño era tan importante para SGI, entonces uno de los pocos grandes clientes de MIPS, que en 1992 compró sin recelo alguno la compañía para evitar que se perdiera el diseño. Como subsidiaria de SGI, la compañía pasó a llamarse MIPS Technologies.

A principios de los 90 MIPS comenzó a otorgar licencias de sus diseños a terceros. Esto probó con justo éxito la simplicidad del núcleo, algo que le permitía ser empleado en numerosas aplicaciones que anteriormente utilizaban diseños CISC mucho menos capaces y de precio y número de puertas similares (comentar que ambas magnitudes están estrechamente relacionadas; el precio de una CPU está generalmente relacionado con el número de puertas y pins externos). Sun Microsystems intentó subirse al carro otorgando licencias de su núcleo SPARC, pero ni llegó a rozar el éxito del MIPS. A finales de los 90 MIPS tenía un caballo de batalla en los procesadores integrados, y en 1997 fue entregado el procesador MIPS 48 millones, convirtiéndose en la primera CPU RISC en desbancar a la famosa familia 68k de Motorola. La familia MIPS tuvo tanto éxito que SGI relanzó a MIPS Technologies en 1998. Más de la mitad de los ingresos de MIPS actualmente proceden de las concesiones de licencias, mientras que gran parte del resto procede de contratos de diseño de núcleos para ser fabricados por terceros.

En 1999 MIPS consolidó su sistema de licencias alrededor de dos diseños básicos, el MIPS32 de 32 bits y el MIPS64 de 64 bits. NEC, Toshiba y SiByte (posteriormente adquirida por Broadcom) obtuvieron licencias para el MIPS64 tan pronto como este procesador fue anunciado; a estas empresas les siguieron otras como Philips, LSI Logic e IDT. Los éxitos se sucedieron, y actualmente los núcleos MIPS son uno de los pesos pesados del mercado de dispositivos como los ordenadores de mano o decodificadores y sintonizadoras de TV. Un indicio de su éxito es el hecho de que Freescale (filial de Motorola) utilice procesadores MIPS en sus aparatos, en lugar de otros propios basados en el PowerPC.

Desde que la arquitectura MIPS es licenciable, ha atraído a numerosas compañías jóvenes a lo largo de los años. Una de las primeras nuevas compañías en diseñar procesadores MIPS fue Quantum Effect Devices. El equipo de diseño de MIPS encargado del R4300 fundó SandCraft, que diseñó el R5432 para NEC y posteriormente el SR7100, uno de los primeros procesadores basados en ejecución fuera de orden para sistemas embebidos. El equipo original de diseño del Digital Equipment Corporation StrongARM finalmente se dividió en dos compañías MIPS: SiByte, fabricante del SB-1250, uno de los primeros sistemas de chip único de alto rendimiento basados en el MIPS; y Alchemy Semiconductor (más tarde comprada por AMD), que fabricaba el sistema de chip único Au-1000 para aplicaciones poco exigentes. Lexra utilizó arquitectura pseudo-MIPS y añadió extensiones DSP para el mercado de los chips de audio y soporte multithreading para el mercado de redes. Debido a que Lexra no era concesionaria de ninguna licencia MIPS, dos pleitos fueron abiertos entre ambas empresas. El primero se resolvió rápidamente al prometer Lexra no seguir anunciando sus procesadores como MIPS-compatibles. El segundo fue largo y dañó los intereses de ambas compañías, terminando con la concesión por parte de MIPS de una licencia gratuita a Lexra, así como el pago de una gran cantidad de dinero.

Familia de CPU's

El primer modelo de CPU comercial de MIPS, el R2000, fue anunciado en 1985. Añadía instrucciones multiciclo para la multiplicación y la división en una unidad independiente integrada en el procesador. Asimismo se añadieron instrucciones para enviar los resultados de esta unidad al núcleo; las cuales necesitaban bloqueos.

El R2000 podía ser iniciado tanto en formato big-endian como little-endian. Tenía 32 registros de propósito general de 32 bits, pero no contaba con un registro de estado, lo que suponía un considerable cuello de botella. Este problema lo compartía con el AMD 29000 y el DEC Alpha. Al contrario que otros registros, el contador de programa no es directamente accesible.

El R2000 además soportaba hasta cuatro co-procesadores, uno de los cuales estaba integrado en la CPU principal para el manejo de excepciones e interrupciones, mientras que los otros tres estaban destinados a otros usos. Una opción era añadir la unidad de punto flotante R2010, que contaba con 32 registros de 32 bits que podían ser empleados como tales para manejar números en simple precisión o bien como 16 registros de 64 bits en doble precisión.

El R3000 sucedería al R2000 en 1988, añadiendo una caché de 32 kB (pronto aumentada a 64 kB) para instrucciones y datos, junto con el soporte de "coherencia caché" para el uso multiprocesador. Mientras hubo defectos en el soporte multiprocesador del R3000, MIPS se las siguió arreglando para que formase parte de varios diseños exitosos de multiprocesador. El R3000 también incluía una Unidad de Manejo de Memoria integrada, característica común entre los procesadores del momento. El R3000 fue el primer diseño exitoso de MIPS en el mercado, y finalmente fueron fabricadas más de 1 millón de unidades. El R3000A, utilizado en la extremadamente exitosa Sony PlayStation, fue una versión acelerada hasta los 40 MHz. Al igual que el R2000, el R3000 fue emparejado con la FPU R3010. Pacemips fabricó el R3400 e IDT el R3500, siendo ambos modelos procesadores R3000s con la FPU R3010 en un único chip. El Toshiba R3900 fue el primer sistema de chip único para los primeros ordenadores de mano con Windows CE.

En la serie R4000, presentada en 1991, se extendió el juego de instrucciones del MIPS para constituir una auténtica arquitectura de 64 bits y se movió la FPU al mismo circuito para crear un sistema de chip único, operando a una velocidad de reloj radicalmente superior (inicialmente 100 MHz). Sin embargo, para poder alcanzar tal frecuencia las cachés fueron reducidas a 8 kB cada una, siendo necesarios tres ciclos de reloj para acceder a ellas. Las altas frecuencias de trabajo fueron alcanzadas gracias a la técnica de segmentación profunda (llamada entonces super-segmentación). Tras el R4000 nació un gran número de versiones mejoradas, incluyendo la R4400 de 1993 con cachés de 16 kB, operaciones de 64 bits sin apenas errores y un controlador para otra caché externa (L2) de 1 MB.

MIPS, actualmente una división de SGI llamada MTI, diseñó la versión de bajo coste R4200, y posteriormente la aún más barata R4300, consistente en un R4200 con bus externo de 32 bits. La Nintendo 64 usa una CPU NEC VR4300 basada en el MIPS de bajo coste R4300i.

Quantum Effect Devices (QED), una compañía aparte fundada por antiguos ingenieros de MIPS, diseñaron el R4600 "Orion", el R4700 "Orion", el R4650 y el R5000. Mientras que el R4000 aumentó la frecuencia a cambio de reducir capacidad de caché, los diseños de QED destacaron por las grandes cachés accesibles en sólo dos ciclos de reloj y por el uso eficiente del área de silicio. Los R4600 y R4700 fueron utilizados en las versiones de bajo coste de las estaciones de trabajo SGI Indy así como en los primeros routers Cisco basados en el MIPS, aquellos de las series 36x0 y 7x00. El R4650 fue empleado en los aparatos originales de WebTV (ahora Microsoft TV). La FPU R5000 trabajaba de forma más eficiente y flexible con números en simple precisión que la R4000, y como resultado, con similar hardware gráfico, las SGI Indy que montaban la FPU R5000 ofrecían mucho mejor rendimiento gráfico que las que contaban con la R4400. SGI rebautizó a las viejas tarjetas gráficas que incorporaron la R5000 para remarcar la mejora. QED posteriormente diseñó las familias RM7000 y RM9000 para sistemas embebidos como redes e impresoras láser. QED fue adquirida por el fabricante de semiconductores PMC-Sierra en agosto de 2000, siendo ésta la última compañía en invertir en la arquitectura MIPS.

El R8000 (1994) fue el primer diseño MIPS superescalar, capaz de ejecutar dos operaciones de ALU y otras dos de memoria en cada ciclo de reloj. El diseño se plasmó en seis chips: una unidad entera (con dos cachés de 16 KB, una para instrucciones y otra L1 de datos), una unidad de punto flotante, tres RAM de caché secundaria totalmente personalizables (dos para accesos a caché secundaria y otra para bus), y un controlador de caché ASIC. El diseño tenía dos unidades segmentadas de suma-multiplicación en doble precisión, las cuales recibían el flujo de datos de la caché secundaria externa de 4 MB. El R8000 fue montado en los servidores SGI Power Challenge a mediados de los 90 y posteriormente en las estaciones de trabajo Power Indigo2. Su rendimiento limitado en operaciones enteras y su elevado coste lo hicieron impopular entre la mayoría de los usuarios, si bien el buen rendimiento de su FPU fue aprovechado por los usuarios científicos; el R8000 estuvo apenas un año en el mercado.

En 1995, fue lanzado el R10000. Este procesador era un diseño de chip único, con mayor velocidad de reloj que el R8000, y mayores cachés primarias de 32 kB para instrucciones y datos. Era también superescalar, pero su gran innovación fue ser "out-of-order". Aún con una FPU más simple, la vasta mejora en las operaciones con enteros, su menor precio y la mayor densidad hicieron del R10000 el preferido por muchos clientes.

Los diseños más recientes se basan en el R10000. El R12000 ha sido fabricado con tecnología mejorada para comprimir el chip y operar a mayor velocidad de reloj. La revisión R14000 permitía mayores frecuencias, soporte adicional para DDR SRAM en el chip externo de caché y un bus de datos front side de 200 MHz para un mejor transferencia. Las últimas versiones fueron llamadas R16000 y R16000A, caracterizándose por una mayor velocidad de reloj, caché L1 adicional y chips de menor tamaño en comparación con los anteriores.