Diferencia entre revisiones de «IIC EC2783 Abril-Julio2016»

(→Registros IIC) |

(→Registros IIC) |

||

| Línea 81: | Línea 81: | ||

Esta dirección de registro tiene 8 bits donde los 7 de la izquierda a la derecha es la Slave Address(Dirección del Esclavo). Esta dirección contiene la dirección del esclavo que se utiliza el modulo IIC. Este campo es usado en el esquema de dirección de siete bits, donde son los 7 bits más bajos del esquema de direcciones de 10 bits. | Esta dirección de registro tiene 8 bits donde los 7 de la izquierda a la derecha es la Slave Address(Dirección del Esclavo). Esta dirección contiene la dirección del esclavo que se utiliza el modulo IIC. Este campo es usado en el esquema de dirección de siete bits, donde son los 7 bits más bajos del esquema de direcciones de 10 bits. | ||

| + | |||

| + | |||

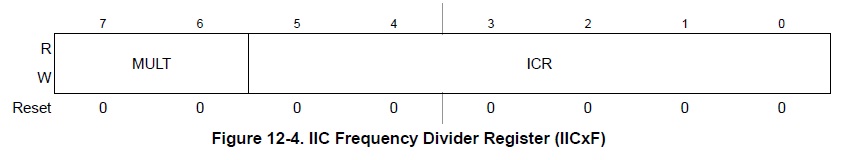

*'''IIC Frequency Divider Register (IICxF)''' | *'''IIC Frequency Divider Register (IICxF)''' | ||

| + | |||

| + | [[Archivo:IICxFreg.jpg]] | ||

Esta dirección de registro tiene 8 bits, donde los bits 7 y 8 son el factor multiplicador(MULT),los 2 bits MULT se usan para definir el factor mul, este factor se utiliza junto con el SCL para generar la baud rate ó la velocidad de transmisión del IIC. Esto 2 bit MULT definen el factor mul de la siguiente manera: | Esta dirección de registro tiene 8 bits, donde los bits 7 y 8 son el factor multiplicador(MULT),los 2 bits MULT se usan para definir el factor mul, este factor se utiliza junto con el SCL para generar la baud rate ó la velocidad de transmisión del IIC. Esto 2 bit MULT definen el factor mul de la siguiente manera: | ||

| Línea 107: | Línea 111: | ||

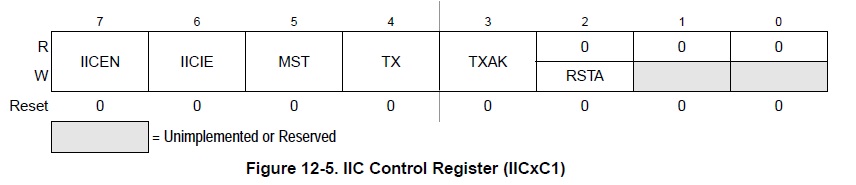

*'''IIC Control Register (IICxC1)''' | *'''IIC Control Register (IICxC1)''' | ||

| + | |||

| + | |||

| + | [[Archivo:IICxC1.jpg]] | ||

Este registro de control esta definido por 8 bits, el bit 7 es el de habilitación (IICEN) donde con 0 el IIC no esta habilitado y con 1 el IIC esta habilitado. | Este registro de control esta definido por 8 bits, el bit 7 es el de habilitación (IICEN) donde con 0 el IIC no esta habilitado y con 1 el IIC esta habilitado. | ||

Revisión del 06:48 1 jul 2016

IIC

Introduccion IIC

El Inter-Integrated Circuit (IIC) provee un método de comunicación entre varios dispositivos. Está diseñado para operar hasta los 100 kbps con la máxima carga del bus y del tiempo. El dispositivo es capaz de operar a tasas de baudios altas, sin sobrecargar el bus. La longitud máxima de comunicación y el número de dispositivos que pueden ser conectados está limitado por la capacitancia del bus, la cual es de 400 pF.

Configuración del módulo:

Los pines SDA y SCL del módulo IIC1 pueden ser reposicionados por software usando el registro SOPT2[IIC1PS] tal como se muestra en la siguiente tabla. Este bit selecciona cual puerto de E/S con propósito general está asociado con la operación del IIC1.

| SOPT2[IIC1PS] | Pines para SDA | Pines para SCL |

|---|---|---|

| 0 por defecto | PTA2 | PTB6 |

| 1 | PTA3 | PTB7 |

Vectores de Interrupción:

Para la serie de microcontroladores MC9S08QE128, los cuales tienen dos IIC, el vector de interrupciones es compartido por ambos módulos IIC. Cuando las interrupciones son habilitadas para ambos módulos, se debe verificar el bit de IICIF (que hace referencia a la bandera de interrupciones) de los registros IIC1S y IIC2S (estos son los registros de status) para determinar cuál módulo es el causante de la interrupción.

Características:

El IIC incluye las siguientes características:

- Compatibilidad con el bus estándar del IIC.

- Operación con múltiples maestros.

- Software programable para una de las 64 frecuencias diferentes del reloj serial.

- Software que permite seleccionar el bit de reconocimiento (acknowledge bit)

- Manejo de interrupciones mediante la transferencia de datos byte por byte.

- Resolución de las interrupciones perdidas con un modo que hace intercambio automático de maestro a esclavo.

- Llamado a las direcciones de identificación de las interrupciones.

- Generación y detección de las señales START y STOP.

- Generación repetida de la señal START.

- Generación y detección del bit acknowledge.

- Detección de la disponibilidad del bus.

- Llamada general de reconocimiento.

- Extensión de la dirección a 10 bits.

Modos de Operación:

Se presenta a continuación una breve descripción de los modos de operación del IIC:

- Modo Corriendo o “Run”: Este es el modo de operación básico. Para conservar la energía en este modo, inhabilite el módulo.

- Modo de espera o “Wait”: El módulo seguirá funcionando mientras que el microcontrolador esté en modo de espera y pueda proporcionar una alarma de despertador.

- Modo detenido o “Stop”: El IIC está inactivo en el modo Stop para reducir el consumo de energía. La instrucción de Stop no afecta a los registros de estados del IIC. Esta instrucción reiniciará el contenido de los registros.

Descripción de Señales externas

Se describe a continuación las señales que son accesibles por cada usuario:

- SCL — Línea del Reloj Serial (Serial Clock Line): Es bidireccional, y es la línea del reloj serial del sistema del IIC.

- SDA - Línea de Data Serial (Serial Data Line): Es la línea de datos serial del sistema del IIC. Es bidireccional.

Registros IIC

La dirección del IIC tiene 10-bit de direccionamiento, 0x11110, se utilizan los primeros 5 bits del primer byte de dirección. Se pueden tener varias combinaciones de leer / escribir, estos formatos son posibles con cambios en los 10-bit de direccionamiento.

Definición de Registros: Todos los registros y bits de control del IIC se especifican sólo por sus nombres, ya que Freescale proporciona una cabecera para trasladar los nombres a las apropiadas direcciones absolutas.

- IIC Address Register (IICxA)

Esta dirección de registro tiene 8 bits donde los 7 de la izquierda a la derecha es la Slave Address(Dirección del Esclavo). Esta dirección contiene la dirección del esclavo que se utiliza el modulo IIC. Este campo es usado en el esquema de dirección de siete bits, donde son los 7 bits más bajos del esquema de direcciones de 10 bits.

- IIC Frequency Divider Register (IICxF)

Esta dirección de registro tiene 8 bits, donde los bits 7 y 8 son el factor multiplicador(MULT),los 2 bits MULT se usan para definir el factor mul, este factor se utiliza junto con el SCL para generar la baud rate ó la velocidad de transmisión del IIC. Esto 2 bit MULT definen el factor mul de la siguiente manera:

00 mul = 01

01 mul = 02

10 mul = 04

11 Reserved

Los últimos cinco bits de la izquierda a la derecha de esta dirección de registro son para la velocidad del reloj (ICR), estos bits se utiliza para determinar del reloj de bus para la selección de la tasa de bits.

Los bits MULT y los bits del clock rate se usan para calcular la velocidad de transmisión, el tiempo de retención SDA, el tiempo de inicio del SCL y el tiempo de detenimiento del SCL. Cada una se puede calcular de la siguiente manera:

-IIC baud rate = bus speed (Hz)/(mul * SCL divider)

-SDA hold time = bus period (s) * mul * SDA hold value

-SCL Start hold time = bus period (s) * mul * SCL Start hold value

-SCL Stop hold time = bus period (s) * mul * SCL Stop hold value

- IIC Control Register (IICxC1)

Este registro de control esta definido por 8 bits, el bit 7 es el de habilitación (IICEN) donde con 0 el IIC no esta habilitado y con 1 el IIC esta habilitado.

El siguiente bit "6" es el de la habilitación de interrupción(IICIE), este determina cuando una interrupción fue solicitada, con 0 no fue solicitada la habilitación y con 1 si fue solicitada la interrupción.

El 5 bit es el del modo maestro seleccionado (MST), con este bit si se cambia de de 0 a 1 cuando la señal se genera en el bus y luego se selecciona el modo maestro. Cuando este bit cambia de 1 a 0 se genera una señal de detención o STOP, y el modo de operación cambia de maestro a esclavo.

0 Slave mode.

1 Master mode.

El 4 bit es el modo de transmicion seleccionado (TX), con este bit se selecciona el modo de transferencia entre el esclavo y el maestro.En el modo maestro de este bit debe establecerse de acuerdo con el tipo de transferencia requerida. Por lo tanto, para los ciclos de direcciones, este bit siempre será alto.Cuando se establezca en modo esclavo este bit debe establecerse por el software de acuerdo con el bit de SRW en el registro de estado.

Recibe 0.

Transmite 1.

El tercer bit es el de reconocimiento de transmicion habilitada (TXAK), este bit reconoce la transmitir habilitada Este bit especifica el valor llevado a la SDA durante el reconocimiento de datos en ciclos, para tanto receptor maestro como receptor esclavo.

0 Se envia una señal de recepción al bus después de recibir un data byte.

1 Ninguna señal de reconocimiento es enviada

El segundo es el de repetir inicio(RSTA) Escribir un 1 en este bit generará una condición de START repetida siempre y cuando sea el maestro. Este bit siempre será leído como bajo. El intento que se repita en el momento equivocado resultará en la pérdida de arbitraje.

- IIC Status Register (IICxS)

Este registro tiene 8 bits donde el bit 7 se llama bandera de transferencia completa(TCF), este bit se establece en la finalizacion de la transferencia de bytes.Tenga en cuenta que este bit sólo es válida durante o inmediatamente después de una transferencia al módulo IIC o desde el modulo IIC.El bit de TCF se elimina mediante la lectura del registro IICxD en el modo receptor o escribiendo en IICxD en el modo de transmisión.

0 Transfer in progress.

1 Transfer complete.

El sexto bit es el de dirigido como un esclavo(IAAS), esté bit se establece cuando la dirección de la llamada coincide con la dirección del esclavo programado, o cuando el bit GCAEN se establece y se recibe una llamada general.Escribir el registro IICxC borra este bit.

El quinto bit es el de bus ocupado(BUSY), indica el estado del bus independientemente del esclavo o del maestro. El bit BUSY está activa cuando se detecta una señal de arranque y se apaga cuando se detecta una señal de STOP.

0 bus está inactivo.

1 bus está ocupado.

El cuarto bit es el de arbitraje perdido(ARBL), este bit es activado por hardware cuando se pierde el procedimiento de arbitraje. El bit debe ser despejado por software, escribiendo un 1 a la misma.

0 funcionamiento de bus estándar.

1 La pérdida de arbitraje.

El 2 bit es el de esclavo de lectura/escritura(SRW),cuando es llamado como un esclavo del SRW bits indica el valor del bit de comando R / W de la dirección solicitante y la envía al maestro.

0 Esclavo recibir, por escrito maestro a esclavo.

1 Esclavo de transmisión, maestra de lectura del esclavo.

El bit 1 es el de bandera de interrupcion del ICC (IICIF), se establece cuando una interrupción está pendiente. Este bit debe ser limpiado por software, escribiendo un 1 en la rutina de interrupción. Uno de los siguientes eventos pueden establecer el bit IICIF:

• Una transferencia de bytes completa • Ajuste de la dirección del esclavo a la dirección llamando • Arbitraje perdió 0 No se interrumpen en espera. 1 interrupción pendiente

el bit 0 Recibe Reconocimiento(RXAK),cuando es baja, indica una señal de confirmación se ha recibido después la realización de un byte de la transmisión de datos en el bus. Si el bit es alto RXAK significaría que no se se detecta la señal.

0 Reconocer recibido.

1 No se reconocen recibido.

- IIC Data I/O Register (IICxD)

Esta dirección de registro tiene 8 bits donde todos los bits dan la informacion de DATA, DATA en modo maestro de transmisión, hace que cuando datos son escritos en el IICxD, se inicie una transferencia de los datos, el bit más significativo se envía primero. En modo maestro de recepción, la lectura de este registro inicia la recepción del siguiente byte de datos.

Cuando se está cambiando el modo maestro de recepción, el modo de inspección debe ser cambiado antes de leer el registro IICxD para evitar una iniciación involuntaria de un maestro recibiendo la transferencia de datos.

En el modo esclavo, las mismas funciones están disponibles después de haberse producido una coincidencia de direcciones.

Tenga en cuenta que el bit TX en IICxC debe reflejar correctamente la dirección deseada de transferencia de los modos maestro y esclavo para que empiece la transmisión. Por ejemplo, si la IIC se configura para modo maestro de transmisión, pero se desea estar en modo maestro de recepción, entonces la lectura de la IICxD no iniciará la recepción.

La lectura de la IICxD devolverá el último byte recibido, mientras que la IIC está configurada tanto en modo maestro de recepción o modo esclavo de recepción. El IICxD no refleja todos los bytes que se transmite en el bus IIC, ni puede verificar el software que un byte se ha escrito para IICxD correctamente leyendo de nuevo.

En el modo maestro de transmisión, el primer byte de los datos escritos en IICxD siguiente afirmación de MST se utiliza para la transferencia de la dirección y debería formar parte de la dirección de llamada (en el bit 7 al bit 1) concatenado con el bit deseado R/W (en la posición de bit 0)

- IIC Control Register 2 (IICxC2)

Esta dirección de registro tiene 8 bits, donde el bit primer bit de izquierda a derecha es el de Dirección general de llamada a activar (GCAEN), donde este bit activara o desactivara la dirección de llamada general.

El bit siguiente al bit GCAEN es el bit de Extensión de dirección (ADEXT), donde controla el numero de bits usado para la dirección del esclavo.

Y los últimos tres bits de los 8 de IICxC2 son de la dirección del esclavo (AD[10:8]).

En el esquema de direcciones de 10 bits la AD [10: 8] contiene los tres bits superiores de la dirección del esclavo. Este campo sólo es válido cuando se establece el bit ADEXT.

== Protocolo IIC ==

El Protocolo Inter-Integrated Circuit (IIC), se compone de 4 partes principales, las cuales componen el envío de un mensaje, descritos a continuación:

Señal de inicio (START Signal): Inicialmente, los buses SCL y SDA se encuentran lógicamente encendidos (en caso de estar disponibles para ser utilizados), por lo cual la señal de inicio, consiste en una bajada del flanco de SDA, mientras SCL se mantiene encendido por parte del maestro. Puede ocurrir un caso en el que se da por repetida una señal de inicio, aun sin finalizado una comunicación previa; esto indica el envío de datos bien sea con otro dispositivo esclavo, o en un modo diferente (lectura/escritura).

Transmisión de la “llave” de esclavo: Este paso consiste en la transmisión de una dirección de 8-bit, los cuales son diferenciados por los primeros 7 bits consecutivos, que representan la “llave” que establece con cuál dispositivo esclavo se desea establecer una comunicación. Cada esclavo mantiene una clave que debe intersectar (lógico AND) con la llave enviada, y solo aquel que coincida con la clave enviada se dispondrá a “escuchar” el mensaje que será enviado a continuación. Con respecto al último bit, éste se refiere a una solicitud de tipo Lectura/Escritura. Para el bit en 1, se desea iniciar una transferencia de lectura del maestro, mientras que para el bit en 0 se desea establecer una comunicación de escritura maestro-esclavo.

Transferencia de datos: Una vez recibida la clave por parte del esclavo correspondiente, con su respectiva dirección de transferencia de datos, se procede a ejecutar en envío de los bytes de información uno a uno, en el cual cada bit representa un clock del reloj, iniciando por el bit as representativo (MSB) y finalizando por el bit menos representativo (LSB). Por último, en el noveno flanco del clock se envía un bit de reconocimiento o de no reconocimiento; en este último caso la transmisión de data no es exitosa y se procede a abortar o a retransmitir según sea el caso.

Señal de STOP: Cuando la transmisión de datos ha finalizado, ambos buses SDA Y SCL vuelven a su estado lógico inicial en 1 y tanto maestro como esclavo dan por finalizada la comunicación.

Funcionamiento del protocolo

Como ya se mencionó, cada 9 flancos de reloj ocurre un reconocimiento del byte inmediatamente enviado. La dirección del esclavo, o “llave” como ya se hizo referencia, se encuentra contenida en una combinación de 10-bits, configurados de la siguiente manera:

El primer byte enviado del maestro al esclavo contiene necesariamente el siguiente contenido:

Bits 0-4 (11110x): Son bits constantes, e indican que una dirección de esclavo será enviada posteriormente.

Bits 5-6 (AD10-AD9): pertenecen a los primeros 2 bits de los 10 que componen la dirección de esclavo.

Bit 7 (R/W): debe estar configurado obligatoriamente en 0 ya que es el maestro quien transmite, y en este caso los esclavos quienes escuchan. NOTA: hasta este punto pueden seguir escuchando mas de un esclavo, ya que la llave será completada por 8-bits, enviados posteriormente.

Luego el maestro debe esperar el bit de reconocimiento, para proceder a enviar la segunda cadena de bit, compuesta por los 8 bits restantes que completan la llave, para la cual solo debe existir una respuesta de reconocimiento, del esclavo respectivo con quien se establece la comunicación.

Dependiendo la dirección de la comunicación, ocurre lo siguiente:

Comunicación Maestro a esclavo: Posteriormente al procedimiento explicado se proceden a enviar los bits de datos, los cuales son recibidos por el esclavo hasta que ocurra la condición de STOP.

Comunicación Esclavo a maestro: Una vez recibido el segundo bit de reconocimiento(A2), se debe enviar un tercer byte con los primeros 7-bits idénticos al primer byte enviado (1110xxx0) con la diferencia del bit 0, el cual es sustituido con 1, para configurar el modo de lectura del maestro.

En la siguiente imagen se muestra gráficamente,

También se puede enviar un mensaje General del tipo “Broadcast”, con llaves de 10 o 7 bits seteando el registro GCAEN.

Interrupciones

El IIC puede generar sólo una interrupción. Para que se genere una interrupción, debe ocurrir cualquiera de los eventos de la tabla siguiente, siempre y cuando el bit IICIE esté activado:

| Fuente de interrupción | Status | Flag | Local Enable |

|---|---|---|---|

| Completar la transferencia de 1 byte | TCF | IICIF | IICIE |

| Ajuste de direcciones de llamada recibidas | IAAS | IICIF | IICIE |

| Pérdida arbitraria | ARBL | IICIF | IICIE |

La interrupción es impulsada por el bit IICIF (del IIC Status Register) y es enmascarada con el bit IICIE (del IIC Control Register). El bit IICIF se puede limpiar asignándole un 1 en la rutina de interrupción. El usuario puede determinar el tipo de interrupción mediante la lectura del Status Register.

Interrupción por transferencia de byte

El bit TCF (transfer complete flag) se establece a flanco de bajada del 9th clock para indicar la completación de la transferencia del byte

Interrupción por detección de dirección

Cuando la dirección de llamadas coincide con la dirección del esclavo programado (IIC address register) o cuando el bit GCAEN está activado y una llamada general es recibida, el bit IAAS en el Status Register es activado. La CPU es interrumpida siempre y cuando se active el bit IICIE. La CPU debe revisar el bit SRW y activar su modo Tx en consecuencia.

Interrupción por pérdida de arbitraje

El IIC es un verdadero bus con múltiples maestros que permite más de un maestro para ser conectado en él. Si dos o más maestros tratan de controlar el bus al mismo tiempo, se determina la prioridad relativa de los maestros en contienda por un procedimiento de arbitraje de datos. El módulo IIC asegura esta interrupción cuando pierde el proceso de arbitraje de datos y el bit ARBL en el Status Register está activado.

El arbitraje se puede perder en las siguientes circunstancias:

- SDA probado como bajo cuando el maestro produce un alto durante un ciclo de dirección o de transmisión de datos.

- SDA probado como bajo cuando el maestro produce un alto durante el bit de aviso de un ciclo de recepción de datos

- Un ciclo de arranque se intenta cuando el bus está ocupado

- Un ciclo repetido de arranque es requerido en modo esclavo

- Se detecta una condición de parada cuando el maestro no lo solicitó

Resets

El IIC se desactiva luego de un RESET. El IIC no puede provocar un reinicio o reseteo del microcontrolador.

Ejemplos IIC

Acelerometro

Formato: Estudiante : Artículo aprobado