I²C (Inter-Integrated Circuit) - MC9S08QE128

Francisco Salanova

El módulo de demostraciones DEMOQE128 de Freescale posee 2 modulos de IIC (Inter-Integrated Circuit). Cada uno tien las siguientes características:

- Compatible con el standart IIC bus.

- Operaciones multi-maestro.

- 64 diferentes frecuencias de reloj seriales programables por software.

- Bit de Acknowledge (acuse de recibido) seleccionable por software.

- Transferencia de datos Byte a Byte por interrupciones.

- Interrupción de perdida de arbitrariedad con cambio automatico de maestro a esclavo.

- Interrupción de identificación de direcciones de llamada.

- Generación y detección de señales START y STOP.

- Generación repetida de la señal START.

- Generación y detección del bit de Acknowledge.

- Detección de bus ocupado.

- Reconocimiento de llamadas generales.

- 10-bit de extensión de dirección.

La interfaz esta diseñada para operar hasta 100 kbps con carga máxima de bus. El dispositivo es capaz de operar a mas altos niveles de baud rate, hasta un máximo de carga de bus de clock/20, con carga de bus reducida. La longitud máxima de comunicación y el nuero de dispositivos que se pueden conectar están limitados por una capacitancia máxima de 400 pF.

Estos módulos también funcionan en los 3 modos de operación del DEMOQE128 como son:

- Run mode Es el modo básico de operación, para conservar energía en este modo se recomienda inhabilitar el modulo.

- Wait mode — El modulo continúa trabajando en este modo y puede generar una interrupción para despertar el MCU.

- Stop mode — El modulo IIC esta inactivo en el modo stop3 para reducir el consumo de energia. La instrucción de STOP no afecta el estado de los registros del IIC. El modo Stop2 resetea el contenido de los registros.

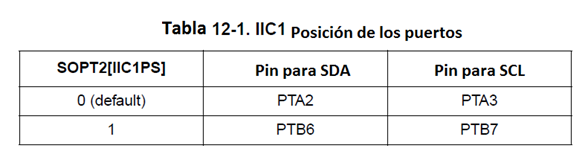

Los pines del IIC1, SDA y SCL pueden ser reubicados por software usando el registro SOPT2[IIC1PS] como se muestra en la tabla Tabla 12-1. El IIC2 no posee puertos re-asignables, estos son PTH6 para SCL2 y PTH7 para SDA2.

Inicialización del modulo en modo esclavo

1. Se escribe el registro IICC2 para:

- Habilitar o inhabilitar las llamadas generales.

- Para seleccionar el modo de direccionmiento entre 10-bit o 7-bit.

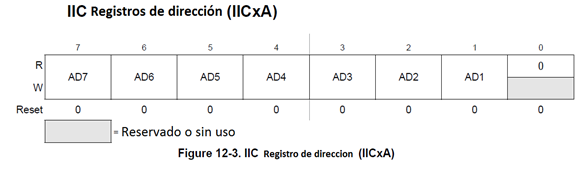

2. Escribir el registro IICA para:

- Para establecer la dirección de esclavo.

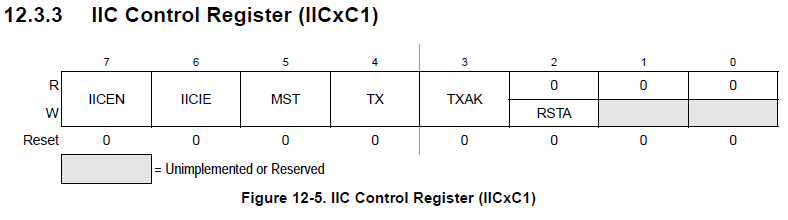

3. Escribir el registro IICC1 para:

- Habilitar el modulo IIC y sus Interrupciones.

4. Inicializar la variables RAM (IICEN = 1 and IICIE = 1) para la transmisión de datos.

5. Inicializar las variables RAM usadas para alcanzar la velocidad deseada del Internal Clock Source.

Inicializacion del modulo en modo maestro

1. Escribir el registro IICF para:

- Para seleccionar el baud rate del IIC.

2. Escribir el registro IICC1 Para

- Habilitar las interrupciones del IIC.

3. Inicializar la variables RAM (IICEN = 1 and IICIE = 1) para la transmisión de datos

4. Inicializar las variables RAM usadas para alcanzar la velocidad deseada del Internal Clock Source.

5. Escribir el registro IICC1 para:

- Habilitar TX (Modo de transmisión).

6. Escribir el registro IICC1 para:

- Habilitar MST (Modo maestro).

7. Escribir el registro IICD:

- Con la dirección del esclavo a comunicarse. (El bit menos significativo de este byte determinara si la comunicación es de recepción como maestro o transmisión como maestro.)

Uso del modulo

Para operaciones como esclavo, un mensaje de IIC entrante que contenga la dirección apropiada comenzara la comunicación IIC. Para operaciones como maestro, la comunicación debe ser iniciada escribiendo el registro IICD.

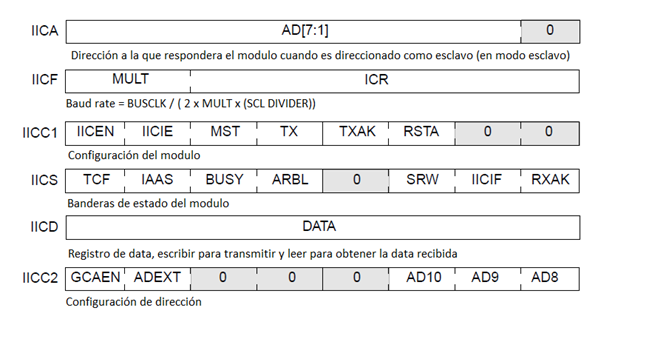

Descipción de los registros

Dirección de esclavo - este campo contiene la dirección de esclavo del modulo IIC. Este campo es usado para el esquema de 7 bits de dirección y los 7 bits bajos del esquema de 10 bits.

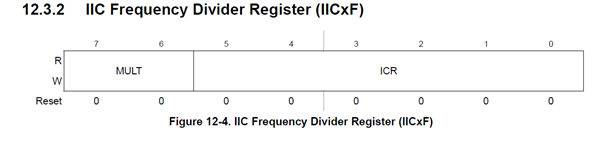

MULT: IIC Multiplier Factor — MULT bits definen el factor de multiplicación. Este factor es usado junto al divisor de SCL para generar el baud rate. Los valores posibles son los siguientes: 00 mul = 01, 01 mul = 02, 10 mul = 04, 11 Reserved.

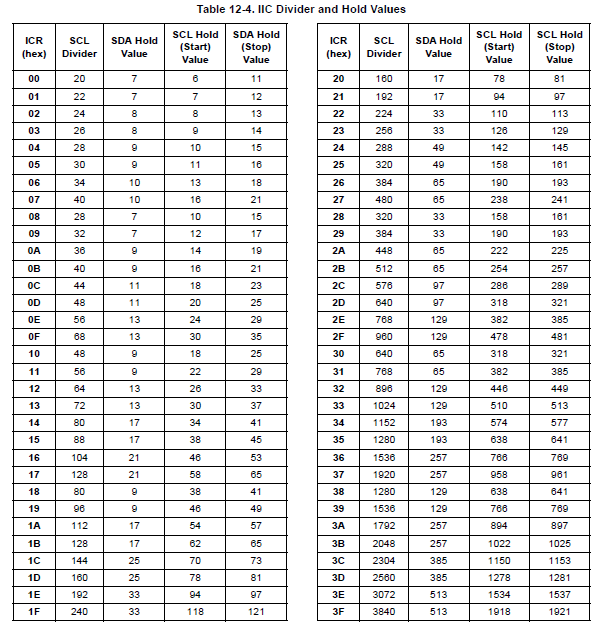

- ICR: IIC Clock Rate —ICR bits son usados para pre-escalar el bus clock para un bit rate seleccionado. Estos bits junto con los MULT bits e usan para determinar el IIC baud rate, el tiempo de espera del SDA, el tiempo de espera del Start del SCL, y el tiempo de espera del Stop del SCL. La tabla siguiente provee los divisores y valores de espera correspondientes para el SCL del ICR. El divisor del SCL multiplicado por el factor mul se usa para generar el IIC baud rate.

- IIC baud rate = velocidad del bus (Hz)/(mul * divisor de SCL)

El tiempo de espera del SDA es el retardo desde el flanco de bajada del SCL hasta el cambio de SDA.

- Tiempo de espera del SDA = periodo del bus (s) * mul * SDA

El tiempo de espera del SCL es el retardo desde el flanco de bajada del SDA, mientras SCL esta en alto (condición inicial) hasta el flanco de bajada de SCL.

- Tiempo de espera inicial del SCL = periodo del bus (s) * mul * tiempo de espera inicial del SCL

El tiempo de espera de STOP del SCL es el retardo desde el flanco de subida del SCL (IIC clock) hasta el flanco de subida del SDA.

- Tiempo de espera de Stop SCL = bus period (s) * mul * SCL Stop hold value

IICEN Habilitar IIC— El bit IICEN habilita el modulo IIC.

0 IIC inhabilitados, 1 IIC esta habilitado.

IICIE Habilita las interrupciones IIC — El bit IICIE determina cuando una interrupcion de IIC es solicitada. 0 IIC interrupciones inhabilitadas. 1 IIC interrupciones habilitadas.

MST Seleccion del modo maestro — El bit MST cambia de 0 a 1 cuando una señal de START es generada en el bus por lo que se selecciona el modo maestro.cuando este bit cambia de 1 a 0 una señal de STOP es generada y el modo de operación cambia de maestro a esclavo. 0 Modo esclavo. 1 Modo maestro.

TX Selecciona el modo de transmicion — El bit TX selecciona la dirección de transición del maestro y del esclavo. En modo maestro este bit se debe escribir de acuerdo al tipo de transferencia requerido. Por lo tanto, para ciclos de diccionario, este bit siempre estará en 1. Cuando se direcciona como esclavo este bit deberá ser escrito por software de acuerdo al bit SRW en el registro de estado. 0 Recibe. 1 Transmite.

TXAK Transmisión de Acknowledge activado — This bit specifies the value driven onto the SDA during data acknowledge

cycles for both master and slave receivers.

0 An acknowledge signal will be sent out to the bus after receiving one data byte.

1 No acknowledge signal response is sent.

2

RSTA

Repeat START — Writing a 1 to this bit will generate a repeated START condition provided it is the current

master. This bit will always be read as a low. Attempting a repeat at the wrong time will result in loss of arbitration.