Diferencia entre revisiones de «I²C (Inter-Integrated Circuit) - MC9S08QE128»

| Línea 254: | Línea 254: | ||

'''Transferencia de Datos''' Antes de que se logre el direccionamiento correcto del esclavo, la transferencia de datos puede proceder byte por byte en la dirección especificada por el bit R/W enviado por el maestro que realizo la llamada. | '''Transferencia de Datos''' Antes de que se logre el direccionamiento correcto del esclavo, la transferencia de datos puede proceder byte por byte en la dirección especificada por el bit R/W enviado por el maestro que realizo la llamada. | ||

| − | todas las transferencias de datos que le sigan a un ciclo de direccionamiento se interpretan cmo transferencia de datos, incluso si contienen informacion de sub-direcciones para el dispositivo esclavo. | + | todas las transferencias de datos que le sigan a un ciclo de direccionamiento se interpretan cmo transferencia de datos, incluso si contienen informacion de sub-direcciones para el dispositivo esclavo.Cada byte de datos tiene 8 bits. |

| − | Cada byte de datos tiene 8 bits. | + | |

| − | SCL | + | |

| + | Los datos solo pueden cambiar mientras SCL esta en cero lógico y deben ser sostenidos en un estado estable mientras SCL esta en uno lógico como muestra la Figura 12-9. | ||

| + | |||

| + | There is one clock pulse on SCL for each data bit, the MSB being | ||

transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the | transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the | ||

receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one | receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one | ||

Revisión del 17:00 16 nov 2012

Francisco Salanova 09-10778

El módulo de demostraciones DEMOQE128 de Freescale posee 2 modulos de IIC (Inter-Integrated Circuit). Cada uno tien las siguientes características:

- Compatible con el standart IIC bus.

- Operaciones multi-maestro.

- 64 diferentes frecuencias de reloj seriales programables por software.

- Bit de Acknowledge (acuse de recibido) seleccionable por software.

- Transferencia de datos Byte a Byte por interrupciones.

- Interrupción de perdida de arbitrariedad con cambio automatico de maestro a esclavo.

- Interrupción de identificación de direcciones de llamada.

- Generación y detección de señales START y STOP.

- Generación repetida de la señal START.

- Generación y detección del bit de Acknowledge.

- Detección de bus ocupado.

- Reconocimiento de llamadas generales.

- 10-bit de extensión de dirección.

La interfaz esta diseñada para operar hasta 100 kbps con carga máxima de bus. El dispositivo es capaz de operar a mas altos niveles de baud rate, hasta un máximo de carga de bus de clock/20, con carga de bus reducida. La longitud máxima de comunicación y el nuero de dispositivos que se pueden conectar están limitados por una capacitancia máxima de 400 pF.

Estos módulos también funcionan en los 3 modos de operación del DEMOQE128 como son:

- Run mode Es el modo básico de operación, para conservar energía en este modo se recomienda inhabilitar el modulo.

- Wait mode — El modulo continúa trabajando en este modo y puede generar una interrupción para despertar el MCU.

- Stop mode — El modulo IIC esta inactivo en el modo stop3 para reducir el consumo de energia. La instrucción de STOP no afecta el estado de los registros del IIC. El modo Stop2 resetea el contenido de los registros.

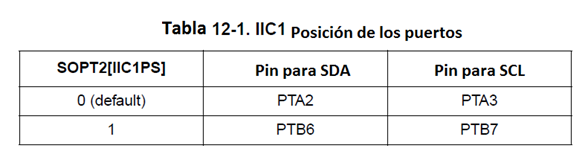

Los pines del IIC1, SDA y SCL pueden ser reubicados por software usando el registro SOPT2[IIC1PS] como se muestra en la tabla Tabla 12-1. El IIC2 no posee puertos re-asignables, estos son PTH6 para SCL2 y PTH7 para SDA2.

Inicialización del modulo en modo esclavo

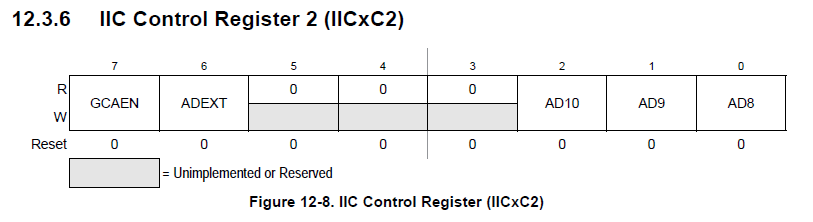

1. Se escribe el registro IICC2 para:

- Habilitar o inhabilitar las llamadas generales.

- Para seleccionar el modo de direccionmiento entre 10-bit o 7-bit.

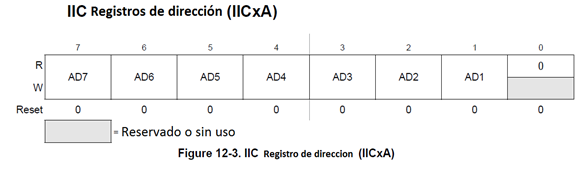

2. Escribir el registro IICA para:

- Para establecer la dirección de esclavo.

3. Escribir el registro IICC1 para:

- Habilitar el modulo IIC y sus Interrupciones.

4. Inicializar la variables RAM (IICEN = 1 and IICIE = 1) para la transmisión de datos.

5. Inicializar las variables RAM usadas para alcanzar la velocidad deseada del Internal Clock Source.

Inicializacion del modulo en modo maestro

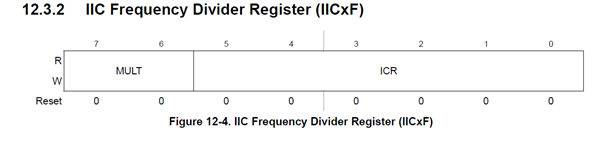

1. Escribir el registro IICF para:

- Para seleccionar el baud rate del IIC.

2. Escribir el registro IICC1 Para

- Habilitar las interrupciones del IIC.

3. Inicializar la variables RAM (IICEN = 1 and IICIE = 1) para la transmisión de datos

4. Inicializar las variables RAM usadas para alcanzar la velocidad deseada del Internal Clock Source.

5. Escribir el registro IICC1 para:

- Habilitar TX (Modo de transmisión).

6. Escribir el registro IICC1 para:

- Habilitar MST (Modo maestro).

7. Escribir el registro IICD:

- Con la dirección del esclavo a comunicarse. (El bit menos significativo de este byte determinara si la comunicación es de recepción como maestro o transmisión como maestro.)

Uso del modulo

Para operaciones como esclavo, un mensaje de IIC entrante que contenga la dirección apropiada comenzara la comunicación IIC. Para operaciones como maestro, la comunicación debe ser iniciada escribiendo el registro IICD.

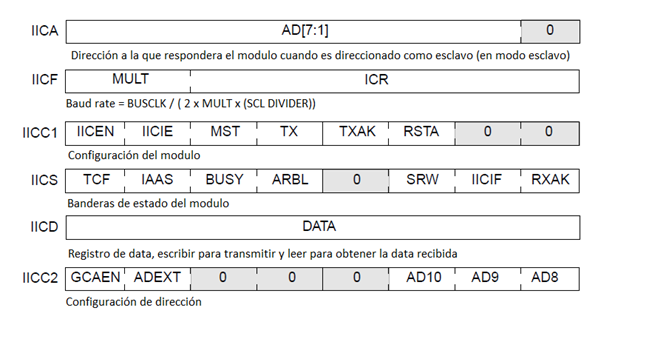

Descipción de los registros

Dirección de esclavo - este campo contiene la dirección de esclavo del modulo IIC. Este campo es usado para el esquema de 7 bits de dirección y los 7 bits bajos del esquema de 10 bits.

MULT: IIC Multiplier Factor — MULT bits definen el factor de multiplicación. Este factor es usado junto al divisor de SCL para generar el baud rate. Los valores posibles son los siguientes:

00 mul = 01

01 mul = 02

10 mul = 04

11 Reserved.

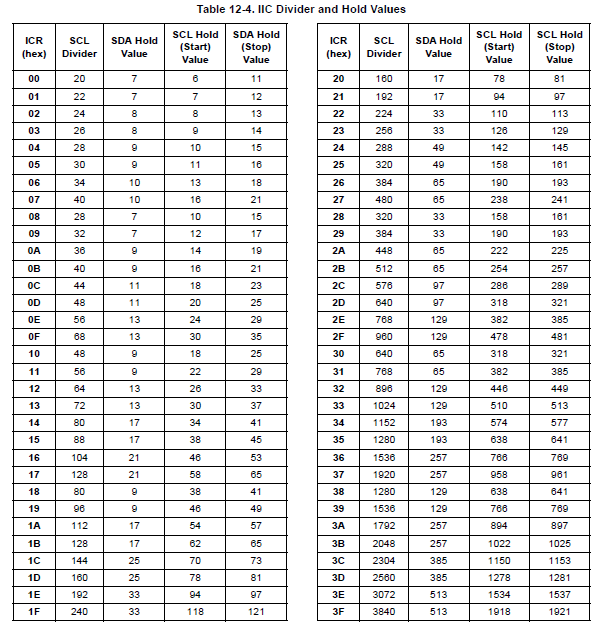

- ICR: IIC Clock Rate —ICR bits son usados para pre-escalar el bus clock para un bit rate seleccionado. Estos bits junto con los MULT bits e usan para determinar el IIC baud rate, el tiempo de espera del SDA, el tiempo de espera del Start del SCL, y el tiempo de espera del Stop del SCL. La tabla siguiente provee los divisores y valores de espera correspondientes para el SCL del ICR. El divisor del SCL multiplicado por el factor mul se usa para generar el IIC baud rate.

- IIC baud rate = velocidad del bus (Hz)/(mul * divisor de SCL)

El tiempo de espera del SDA es el retardo desde el flanco de bajada del SCL hasta el cambio de SDA.

- Tiempo de espera del SDA = periodo del bus (s) * mul * SDA

El tiempo de espera del SCL es el retardo desde el flanco de bajada del SDA, mientras SCL esta en alto (condición inicial) hasta el flanco de bajada de SCL.

- Tiempo de espera inicial del SCL = periodo del bus (s) * mul * tiempo de espera inicial del SCL

El tiempo de espera de STOP del SCL es el retardo desde el flanco de subida del SCL (IIC clock) hasta el flanco de subida del SDA.

- Tiempo de espera de Stop SCL = bus period (s) * mul * SCL Stop hold value

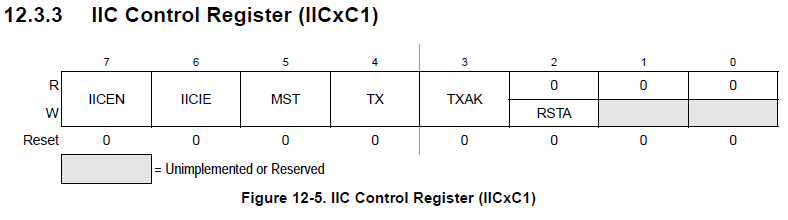

IICEN Habilitar IIC— El bit IICEN habilita el modulo IIC.

0 IIC inhabilitados. 1 IIC esta habilitado.

IICIE Habilita las interrupciones IIC — El bit IICIE determina cuando una interrupcion de IIC es solicitada.

0 IIC interrupciones inhabilitadas. 1 IIC interrupciones habilitadas.

MST Seleccion del modo maestro — El bit MST cambia de 0 a 1 cuando una señal de START es generada en el bus por lo que se selecciona el modo maestro.cuando este bit cambia de 1 a 0 una señal de STOP es generada y el modo de operación cambia de maestro a esclavo.

0 Modo esclavo.

1 Modo maestro.

TX Selecciona el modo de transmicion — El bit TX selecciona la dirección de transición del maestro y del esclavo. En modo maestro este bit se debe escribir de acuerdo al tipo de transferencia requerido. Por lo tanto, para ciclos de diccionario, este bit siempre estará en 1. Cuando se direcciona como esclavo este bit deberá ser escrito por software de acuerdo al bit SRW en el registro de estado.

0 Recibe.

1 Transmite.

TXAK Transmisión de Acknowledge habilitado — este bit especifica el valor enviado al SDA durante el ciclo de acknowledge para los receptores del maestro y esclavo.

0 Una señal de acknowledge se envia al bus despues de recivir un byte de data.

1 Ninguna señal de acknowledge de respuesta es enviada.

RSTA Repetir señal de START — Escribir 1 en este bit generara una señal repetida de START si se es el maestro actual. Este bit siempre se leerá como bajo. Intentar repetir en un momento inadecuado causara la perdida de arbitrariedad.

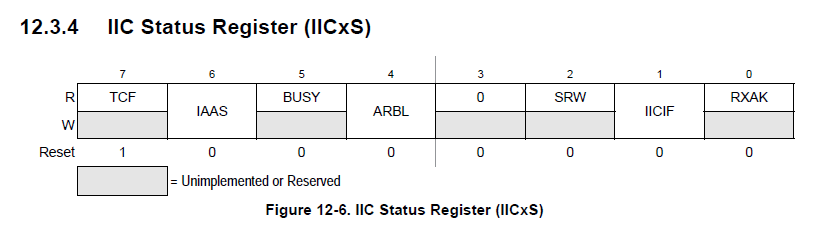

TCF Bandera de transferencia completada — Este bit se escribe en 1 cuando se completa la tranferencia de un byte de data. este bit es unicamente valido durante o inmediatamente después de una transferencia al modulo IIC o desde el modulo IIC. El bit TCF se borra leyendo el registro IICxD en modo de recepcion o escribiendo el registro IICxD en modo de transmisión.

0 Transferencia en progreso.

1 Transferencia completada.

IAAS Direccionado como esclavo — El bit IAAS se escribe en uno cuando la direccion de llamada coincide con la direccion de esclavo programada para el modulo, o cuando el bit GCAEN se escribe en 1 y una llamada general es recivida. Escribir el registro IICxC borra este bit.

0 No direccionado.

1 Direccionado como esclavo.

BUSY Bus ocupado — El bit BUSY indica el estado del bus a pesar de estar e modo esclavo o maestro. El bit BUSY se escribe cuando una señal de START es detectada y se borra cuando una señal de STOP es detectada.

0 Bus esta en espera.

1 Bus esta ocupado.

ARBL Perdida de arbitraiedad — Este bit se activva por hardware cuando el procedimiento de arbitracion se pierde. El bit ARBL se debe borrar por software, escribiendo un 1 en el.

0 Operación Standard del bus.

1 Perdida de arbitrariedad.

SRW Escritura/Lectura en modo esclavo — Cuando se direcciona como esclavo el bit SRW indica el valor del bit de comando R/W de la direccion de llamada enviada al maestro.

0 Recepción modo esclavo, Escritura en el esclavo, en modo maestro.

1 Transmisión modo esclavo, Lectura desde el esclavo, en modo maestro.

IICIF Bandra de interrupcion IIC — El bit IICIF se activa cuando una interrupcion esta pendiente. Este bit debe ser borrado por software, escribiendo un 1 en el en la rutina de interrupción. Cualquiere de los siguientes evntos puede activar el bit IICIF: • Se completo la transferencia de un byte. • Coincidencia de la direccion de esclavo con la direccion de llamada. • Perdida de arbitrariedad.

0 No hay interrupcion pendiente.

1 Hay una interrupcion pendiente.

RXAK Recepcion de Acknowledge— Cuando el bit RXAK esta en bajo, indica que una señal de acknowledge se ha recibido desues de la transmision de un byte de data en el bus. Si el bit RXAK esta en alto significa que no se ha detectado una señal de acknowledge.

0 Señal de acknowledge recibida.

1 No se ha recibido señal de acknowledge.

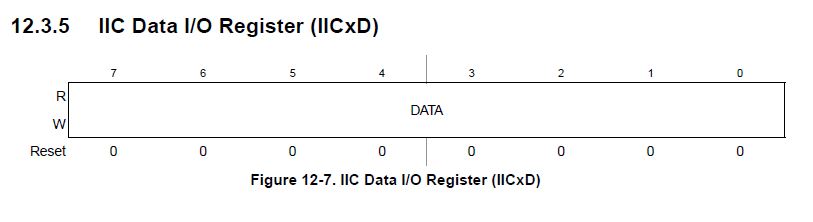

Data — En modo de transmisión maestro, cuando se escribe una data en el registro IICxD, se inicia la transferencia de la data. El bit mas significativo es enviado primero. en modo de transmisión maestro, leer este registro inicia la transferensia del siguiente byte de data.

GCAEN Habilitar direcciones de llamada general — El bit GCAEN Habilita o inhabilita las direcciones de llamada general.

0 Direcciones de llamada general inhabilitadas.

1 Direcciones de llamada general habilitadas.

ADEXT Extension de dirección — El bit ADEXT controla el numero de bits usado para las direcciones de esclavo.

0 Esquema de sireccion de 7-bits

1 Esquema de sireccion de 10-bits

AD Dirección de esclavo — EL campo AD contiene los 3 bits mas altos de la dirección de esclavo en el esquema de 10-bits. Este campo es valido sólo si el bit ADEXT bit esta habilitado.

IIC Protocol

El bus del IIC utiliza na linea de datos serial (SDA) y una linea de reloj serial (SCL) para transferencia de datos. Todos los dispositivos deben tener salidas tipo open-drain o open collector. Un AND lógico se aplica en ambas lineas con resistencias de pull-up externas. El valor de estas resistencias depende del sistema.

Generalmente, una comunicación standard esta compuesta de cuatro partes: • Señal de START • Transmisión de la direccion de esclavo • Transferencia de datos • Señal de STOP La señal de STOP no se debe confundir con la instrucción de CPU STOP.

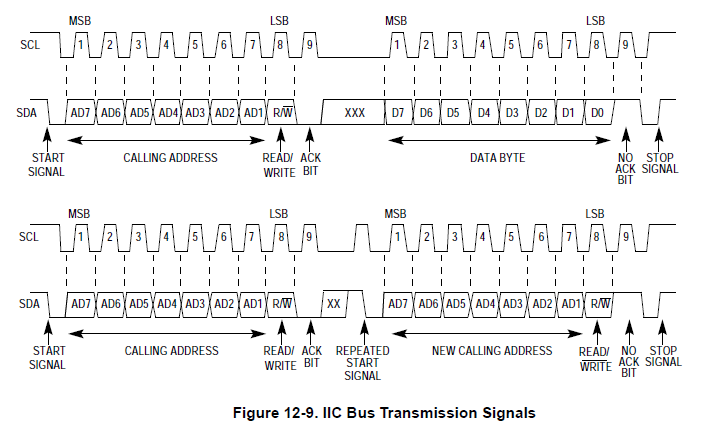

Señal de STARTCuando el bus esta libre, ningun dispisotivo maestro esta controlando el bus (SCL y SDA estan el 1 lógico), un dispositivo maestro debe iniciar la comunicación enviando una señal de START. Com se muestra en la figura 12-9.

Una señal de START se define como el cambio de 1 a cero lógico de la linea SDA mientras SCL esta en 1 lógico. esta señal denota el inicio de una nueva transferencia de datos (cada transmisión de datos debe contener varios bytes de data) y sacar a los esclavos fuera de su estado de espera.

Transmisión de la dirección de esclavo El primer byte de data transmitido inmediatamente despues de la señal de START es la dirección de esclavo transmitida por el maestro. Esta es una dirección de llamada de siete bits seguida por el bit R/W. El bit R/W le dice al esclavo la dirección deseada de la transferencia de datos.

1 = Transferencia tipo lectura, el esclavo transmite data a el maestro.

0 = Transferencia tipo escritura, el maestro transmite data al esclavo.

Sólo el esclavo con una dirección de llamada que coincida con la dirección transmitida por el maestro respondera enviando de vuelta un bit de acknowledge. Esto se logra oniendo en cero lógico la linea SDA en el noveno clock (ver Figura 12-9).

Ningun esclavo en el sisttema debe tener la misma dirección de llamada. Si el modulo IIC es el maestro, no debe transmitir una dirección de llamada de esclavo igual a la suya. El IIC no puede ser maestro y esclavo al mismo tiempo.

Si una perdida de arbitrariedad ocurre durante el ciclo de direccionamiento, el IIC cambiara a modo esclavo.

Transferencia de Datos Antes de que se logre el direccionamiento correcto del esclavo, la transferencia de datos puede proceder byte por byte en la dirección especificada por el bit R/W enviado por el maestro que realizo la llamada.

todas las transferencias de datos que le sigan a un ciclo de direccionamiento se interpretan cmo transferencia de datos, incluso si contienen informacion de sub-direcciones para el dispositivo esclavo.Cada byte de datos tiene 8 bits.

Los datos solo pueden cambiar mientras SCL esta en cero lógico y deben ser sostenidos en un estado estable mientras SCL esta en uno lógico como muestra la Figura 12-9.

There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses. If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer. If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line. In either case, the data transfer is aborted and the master does one of two things: • Relinquishes the bus by generating a STOP signal. • Commences a new calling by generating a repeated START signal. Inter-Integrated Circuit (S08IICV2) MC9S08QE128 MCU Series Reference Manual, Rev. 2 230 Freescale Semiconductor 12.4.1.4 STOP Signal The master can terminate the communication by generating a STOP signal to free the bus. However, the master may generate a START signal followed by a calling command without generating a STOP signal first. This is called repeated START. A STOP signal is defined as a low-to-high transition of SDA while SCL at logical 1 (see Figure 12-9). The master can generate a STOP even if the slave has generated an acknowledge at which point the slave must release the bus. 12.4.1.5 Repeated START Signal As shown in Figure 12-9, a repeated START signal is a START signal generated without first generating a STOP signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus. 12.4.1.6 Arbitration Procedure The IIC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case, the transition from master to slave mode does not generate a STOP condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration. 12.4.1.7 Clock Synchronization Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device’s clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 12-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.