Diferencia entre revisiones de «I²C (Inter-Integrated Circuit) - MC9S08QE128»

(→Inicialización del módulo en modo esclavo) |

(→Inicialización del módulo en modo esclavo) |

||

| (No se muestran 12 ediciones intermedias de 6 usuarios) | |||

| Línea 1: | Línea 1: | ||

| − | ''' | + | <div style="top:+0.3em; text-align: center;font-size:100%; border:1px solid #C7D0F8; background:#F2F5FD;width:80%"> |

| − | + | '''Este artículo está incompleto. Necesita trabajo adicional. Revisar la discusión.'''</div> | |

==Introducción== | ==Introducción== | ||

| Línea 37: | Línea 37: | ||

---- | ---- | ||

| − | ===Inicialización del módulo en modo esclavo | + | ==Diagrama de Bloques== |

| + | |||

| + | |||

| + | [[Archivo:D_bloque.png]] | ||

| + | |||

| + | |||

| + | [[Archivo:Resaltando_los_m_de_iic.png]] | ||

| + | |||

| + | ==Inicialización del módulo en modo esclavo== | ||

1. Se escribe el registro IICC2 para: | 1. Se escribe el registro IICC2 para: | ||

| Línea 147: | Línea 155: | ||

'''TXAK''' Transmisión de Acknowledge habilitado — este bit especifica el valor enviado al SDA durante el ciclo de acknowledge para los receptores del maestro y esclavo. | '''TXAK''' Transmisión de Acknowledge habilitado — este bit especifica el valor enviado al SDA durante el ciclo de acknowledge para los receptores del maestro y esclavo. | ||

| − | 0 Una señal de acknowledge se | + | 0 Una señal de acknowledge se envía al bus después de recibir un byte de data. |

1 Ninguna señal de acknowledge de respuesta es enviada. | 1 Ninguna señal de acknowledge de respuesta es enviada. | ||

| − | '''RSTA''' Repetir señal de START — Escribir 1 en este bit generara una señal repetida de START si se es el maestro actual. Este bit siempre se leerá como bajo. Intentar repetir en un momento inadecuado | + | '''RSTA''' Repetir señal de START — Escribir 1 en este bit generara una señal repetida de START si se es el maestro actual. Este bit siempre se leerá como bajo. Intentar repetir en un momento inadecuado causará la pérdida de arbitrariedad. |

[[Archivo:IIC_status_register.png]] | [[Archivo:IIC_status_register.png]] | ||

| Línea 177: | Línea 185: | ||

0 Operación Standard del bus. | 0 Operación Standard del bus. | ||

| − | 1 | + | 1 Pérdida de arbitrariedad. |

'''SRW''' Escritura/Lectura en modo esclavo — Cuando se direcciona como esclavo el bit SRW indica el valor del bit de comando R/W de la dirección de llamada enviada al maestro. | '''SRW''' Escritura/Lectura en modo esclavo — Cuando se direcciona como esclavo el bit SRW indica el valor del bit de comando R/W de la dirección de llamada enviada al maestro. | ||

| Línea 219: | Línea 227: | ||

'''ADEXT''' Extension de dirección — El bit ADEXT controla el numero de bits usado para las direcciones de esclavo. | '''ADEXT''' Extension de dirección — El bit ADEXT controla el numero de bits usado para las direcciones de esclavo. | ||

| − | 0 Esquema de | + | 0 Esquema de dirección de 7-bits. |

| − | 1 Esquema de | + | 1 Esquema de dirección de 10-bits. |

'''AD''' Dirección de esclavo — EL campo AD contiene los 3 bits mas altos de la dirección de esclavo en el esquema de 10-bits. Este campo es valido sólo si el bit ADEXT bit esta habilitado. | '''AD''' Dirección de esclavo — EL campo AD contiene los 3 bits mas altos de la dirección de esclavo en el esquema de 10-bits. Este campo es valido sólo si el bit ADEXT bit esta habilitado. | ||

| Línea 268: | Línea 276: | ||

Los datos solo pueden cambiar mientras SCL esta en cero lógico y deben ser sostenidos en un estado estable mientras SCL esta en uno lógico como muestra la Figura 12-9. | Los datos solo pueden cambiar mientras SCL esta en cero lógico y deben ser sostenidos en un estado estable mientras SCL esta en uno lógico como muestra la Figura 12-9. | ||

| + | |||

| + | ==Estrechamiento del reloj== | ||

| + | |||

| + | |||

| + | Existen casos en los cuales es necesario bajar la velocidad de transferencia de bit, para ahorrar energía o una cierta cantidad de ciclos en algún proceso dado. El IIC ofrece la ventaja, al tener el sistema Maestro-Esclavo, de realizar dicha opción. Se puede llegar a esta condición, unicamente bajando el periodo SCL (''Serial Clock'') del sistema Esclavo, '''cuando''' el periodo del SCL del sistema Maestro es bajado. | ||

| + | |||

| + | |||

| + | |||

| + | SCL-SLAVE (low period) > SCL-MASTER (low period) -> ''Clock Stretching successful'' | ||

| + | |||

| + | |||

| + | ==Llamado General a dirección== | ||

| + | |||

| + | |||

| + | Estos llamados pueden llegar a ser pedidos en formatos de direcciones de 7 o 10 bits. Para el caso en que el bit de GCAEN (''General Call Adress Enable'') se encuentra en 1, el IIC iguala la dirección del llamado general, como su propia dirección esclavo, y cuando este responde a dicho llamado, actua como un receptor-esclavo, seguido del 'set' al bit de IAAS después de cada ciclo de dirección. | ||

| + | |||

| + | |||

| + | |||

| + | Es importante recalcar, que el sistema debe leer el registro IICD, luego de transmitir el primer byte. De dicha manera, se comprueba si la dirección en cuestión en su dirección esclavo, o, un llamado general. De ser el valor igual a 00, fue un llamado general. | ||

| + | |||

| + | |||

| + | |||

| + | Por último, si el bit GCAEN mencionado anteriormente se encuentra en 0, el IIC ignora cualquier dato brindado por un llamado general. | ||

| Línea 277: | Línea 308: | ||

| − | ==Interrupciones== | + | ==[[Interrupciones]]== |

| Línea 285: | Línea 316: | ||

| − | ==Interrupción de transferencia de byte== | + | ===Interrupción de transferencia de byte=== |

| Línea 291: | Línea 322: | ||

| − | ==Interrupción de detección de dirección== | + | ===Interrupción de detección de dirección=== |

Cuando la dirección de llamada coincide con la dirección de esclavo programada en el registro de direccióno cuando el bit GCAEN es activado y una llamada general es recibida, el bit IAAS se activa. El CPU es interrumpido cuando llega una interrupción. El CPU debe verificar el bit SRW y escribirlo de acuerdo al modo de Tx correcto. | Cuando la dirección de llamada coincide con la dirección de esclavo programada en el registro de direccióno cuando el bit GCAEN es activado y una llamada general es recibida, el bit IAAS se activa. El CPU es interrumpido cuando llega una interrupción. El CPU debe verificar el bit SRW y escribirlo de acuerdo al modo de Tx correcto. | ||

| − | ==Interrupción de pérdida de arbitrariedad== | + | ===Interrupción de pérdida de arbitrariedad=== |

| Línea 310: | Línea 341: | ||

==Referencias == | ==Referencias == | ||

*[http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf''MC9S08QE128RM Reference Manual''] | *[http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf''MC9S08QE128RM Reference Manual''] | ||

| + | |||

| + | *[http://www.freescale.com/files/microcontrollers/doc/user_guide/DEMOQE128UM.pdf ''DEMOQE128 User Manual''] | ||

[[Categoría: MC9S08QE128]] | [[Categoría: MC9S08QE128]] | ||

Revisión actual del 18:07 6 abr 2013

Contenido

Introducción

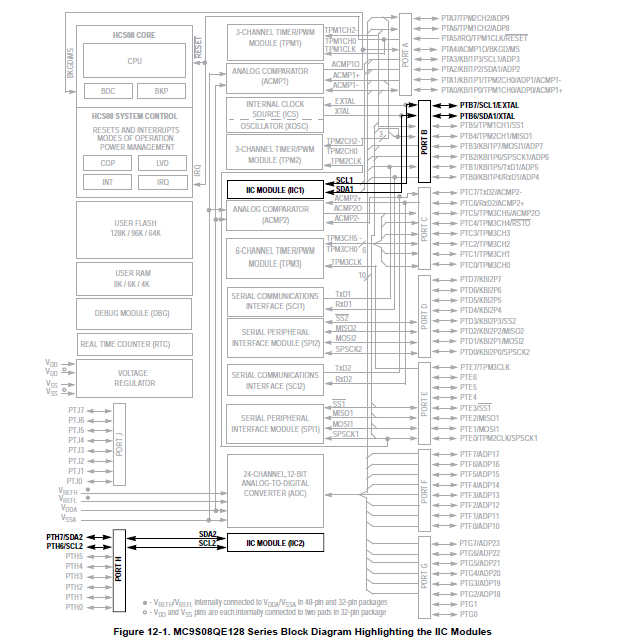

El módulo de demostraciones DEMOQE128 de Freescale posee 2 módulos de IIC (Inter-Integrated Circuit). Cada uno tien las siguientes características:

- Compatible con el standart IIC bus.

- Operaciones multi-maestro.

- 64 diferentes frecuencias de reloj seriales programables por software.

- Bit de Acknowledge (acuse de recibido) seleccionable por software.

- Transferencia de datos Byte a Byte por interrupciones.

- Interrupción de perdida de arbitrariedad con cambio automático de maestro a esclavo.

- Interrupción de identificación de direcciones de llamada.

- Generación y detección de señales START y STOP.

- Generación repetida de la señal START.

- Generación y detección del bit de Acknowledge.

- Detección de bus ocupado.

- Reconocimiento de llamadas generales.

- 10-bit de extensión de dirección.

La interfaz esta diseñada para operar hasta 100 kbps con carga máxima de bus. El dispositivo es capaz de operar a mas altos niveles de baud rate, hasta un máximo de carga de bus de clock/20, con carga de bus reducida. La longitud máxima de comunicación y el número de dispositivos que se pueden conectar están limitados por una capacitancia máxima de 400 pF.

Estos módulos también funcionan en los 3 modos de operación del DEMOQE128 como son:

- Run mode Es el modo básico de operación, para conservar energía en este modo se recomienda inhabilitar el modulo.

- Wait mode — El módulo continúa trabajando en este modo y puede generar una interrupción para despertar el MCU.

- Stop mode — El módulo IIC esta inactivo en el modo stop3 para reducir el consumo de energía. La instrucción de STOP no afecta el estado de los registros del IIC. El modo Stop2 resetea el contenido de los registros.

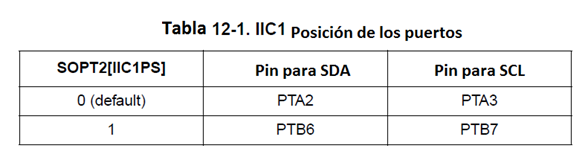

Los pines del IIC1, SDA y SCL pueden ser reubicados por software usando el registro SOPT2[IIC1PS] como se muestra en la tabla Tabla 12-1. El IIC2 no posee puertos re-asignables, estos son PTH6 para SCL2 y PTH7 para SDA2.

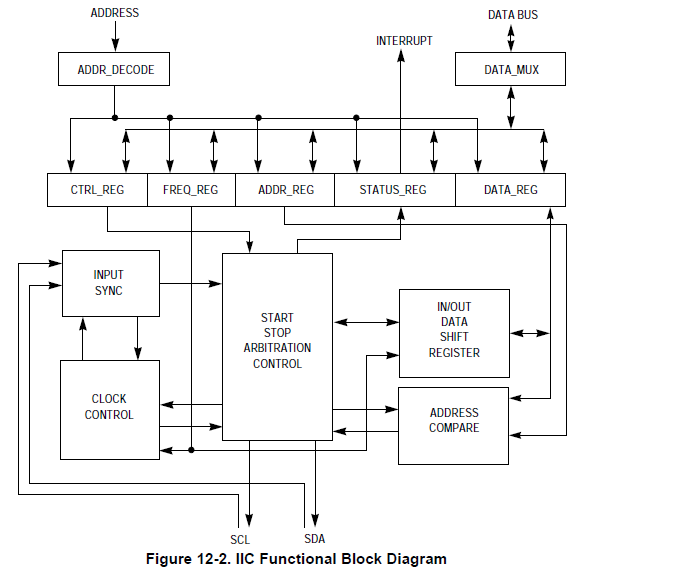

Diagrama de Bloques

Inicialización del módulo en modo esclavo

1. Se escribe el registro IICC2 para:

- Habilitar o inhabilitar las llamadas generales.

- Para seleccionar el modo de direccionamiento entre 10-bit o 7-bit.

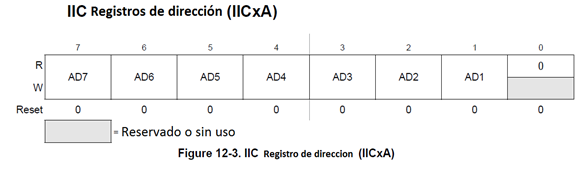

2. Escribir el registro IICA para:

- Para establecer la dirección de esclavo.

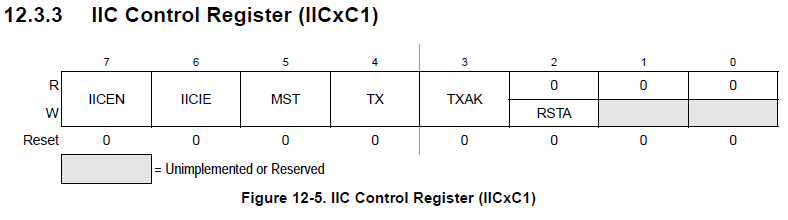

3. Escribir el registro IICC1 para:

- Habilitar el módulo IIC y sus Interrupciones.

4. Inicializar la variables RAM (IICEN = 1 and IICIE = 1) para la transmisión de datos.

5. Inicializar las variables RAM usadas para alcanzar la velocidad deseada del Internal Clock Source.

Inicialización del modulo en modo maestro

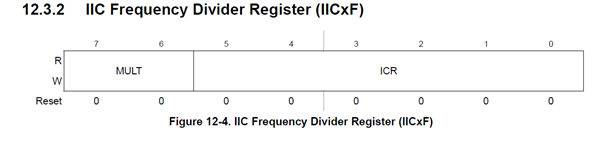

1. Escribir el registro IICF para:

- Para seleccionar el baud rate del IIC.

2. Escribir el registro IICC1 para:

- Habilitar las interrupciones del IIC.

3. Inicializar la variables RAM (IICEN = 1 and IICIE = 1) para la transmisión de datos.

4. Inicializar las variables RAM usadas para alcanzar la velocidad deseada del Internal Clock Source.

5. Escribir el registro IICC1 para:

- Habilitar TX (Modo de transmisión).

6. Escribir el registro IICC1 para:

- Habilitar MST (Modo maestro).

7. Escribir el registro IICD:

- Con la dirección del esclavo a comunicarse. (El bit menos significativo de este byte determinará si la comunicación es de recepción como maestro o transmisión como maestro).

Uso del módulo

Para operaciones como esclavo, un mensaje de IIC entrante que contenga la dirección apropiada comenzara la comunicación IIC. Para operaciones como maestro, la comunicación debe ser iniciada escribiendo el registro IICD.

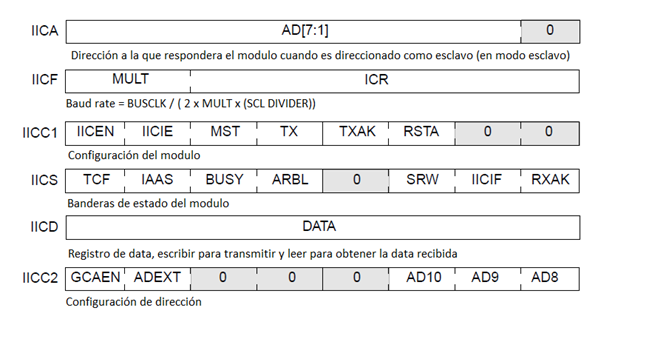

Descripción de los registros

Dirección de esclavo - este campo contiene la dirección de esclavo del modulo IIC. Este campo es usado para el esquema de 7 bits de dirección y los 7 bits bajos del esquema de 10 bits.

MULT: IIC Multiplier Factor — MULT bits definen el factor de multiplicación. Este factor es usado junto al divisor de SCL para generar el baud rate. Los valores posibles son los siguientes:

00 mul = 01

01 mul = 02

10 mul = 04

11 Reserved.

- ICR: IIC Clock Rate —ICR bits son usados para pre-escalar el bus clock para un bit rate seleccionado. Estos bits junto con los MULT bits e usan para determinar el IIC baud rate, el tiempo de espera del SDA, el tiempo de espera del Start del SCL, y el tiempo de espera del Stop del SCL. La tabla siguiente provee los divisores y valores de espera correspondientes para el SCL del ICR. El divisor del SCL multiplicado por el factor mul se usa para generar el IIC baud rate.

- IIC baud rate = velocidad del bus (Hz)/(mul * divisor de SCL).

El tiempo de espera del SDA es el retardo desde el flanco de bajada del SCL hasta el cambio de SDA.

- Tiempo de espera del SDA = periodo del bus (s) * mul * SDA.

El tiempo de espera del SCL es el retardo desde el flanco de bajada del SDA, mientras SCL esta en alto (condición inicial) hasta el flanco de bajada de SCL.

- Tiempo de espera inicial del SCL = periodo del bus (s) * mul * tiempo de espera inicial del SCL.

El tiempo de espera de STOP del SCL es el retardo desde el flanco de subida del SCL (IIC clock) hasta el flanco de subida del SDA.

- Tiempo de espera de Stop SCL = bus period (s) * mul * SCL Stop hold value.

IICEN Habilitar IIC— El bit IICEN habilita el modulo IIC.

0 IIC inhabilitados. 1 IIC esta habilitado.

IICIE Habilita las interrupciones IIC — El bit IICIE determina cuando una interrupción de IIC es solicitada.

0 IIC interrupciones inhabilitadas. 1 IIC interrupciones habilitadas.

MST Selección del modo maestro — El bit MST cambia de 0 a 1 cuando una señal de START es generada en el bus por lo que se selecciona el modo maestro. Cuando este bit cambia de 1 a 0 una señal de STOP es generada y el modo de operación cambia de maestro a esclavo.

0 Modo esclavo.

1 Modo maestro.

TX Selecciona el modo de transmisión — El bit TX selecciona la dirección de transición del maestro y del esclavo. En modo maestro este bit se debe escribir de acuerdo al tipo de transferencia requerido. Por lo tanto, para ciclos de diccionario, este bit siempre estará en 1. Cuando se direcciona como esclavo este bit deberá ser escrito por software de acuerdo al bit SRW en el registro de estado.

0 Recibe.

1 Transmite.

TXAK Transmisión de Acknowledge habilitado — este bit especifica el valor enviado al SDA durante el ciclo de acknowledge para los receptores del maestro y esclavo.

0 Una señal de acknowledge se envía al bus después de recibir un byte de data.

1 Ninguna señal de acknowledge de respuesta es enviada.

RSTA Repetir señal de START — Escribir 1 en este bit generara una señal repetida de START si se es el maestro actual. Este bit siempre se leerá como bajo. Intentar repetir en un momento inadecuado causará la pérdida de arbitrariedad.

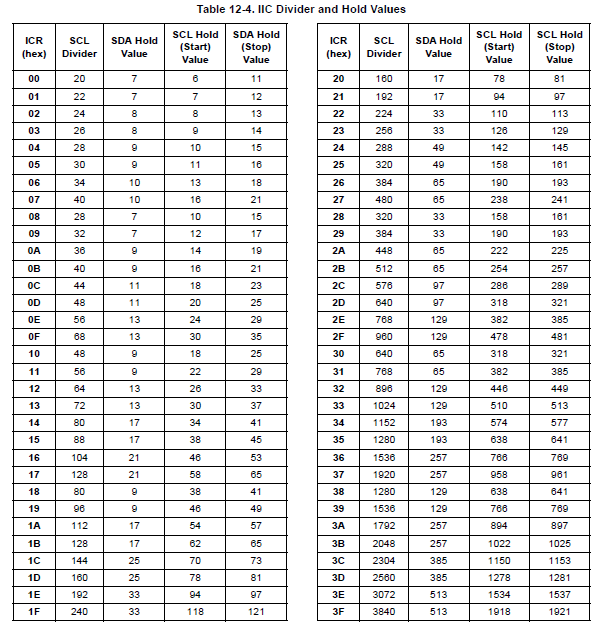

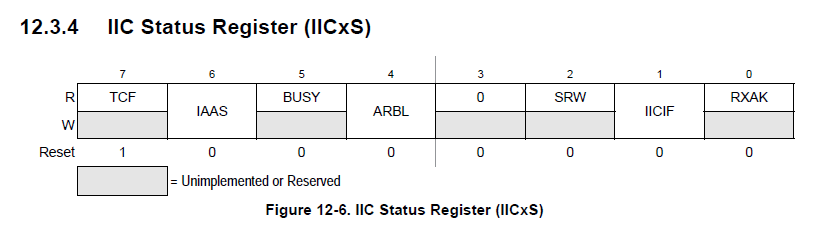

TCF Bandera de transferencia completada — Este bit se escribe en 1 cuando se completa la transferencia de un byte de data. este bit es únicamente válido durante o inmediatamente después de una transferencia al modulo IIC o desde el modulo IIC. El bit TCF se borra leyendo el registro IICxD en modo de recepción o escribiendo el registro IICxD en modo de transmisión.

0 Transferencia en progreso.

1 Transferencia completada.

IAAS Direccionado como esclavo — El bit IAAS se escribe en uno cuando la dirección de llamada coincide con la dirección de esclavo programada para el modulo, o cuando el bit GCAEN se escribe en 1 y una llamada general es recibida. Escribir el registro IICxC borra este bit.

0 No direccionado.

1 Direccionado como esclavo.

BUSY Bus ocupado — El bit BUSY indica el estado del bus a pesar de estar e modo esclavo o maestro. El bit BUSY se escribe cuando una señal de START es detectada y se borra cuando una señal de STOP es detectada.

0 Bus esta en espera.

1 Bus esta ocupado.

ARBL Perdida de arbitrariedad — Este bit se activa por hardware cuando el procedimiento de arbitración se pierde. El bit ARBL se debe borrar por software, escribiendo un 1 en el.

0 Operación Standard del bus.

1 Pérdida de arbitrariedad.

SRW Escritura/Lectura en modo esclavo — Cuando se direcciona como esclavo el bit SRW indica el valor del bit de comando R/W de la dirección de llamada enviada al maestro.

0 Recepción modo esclavo, Escritura en el esclavo, en modo maestro.

1 Transmisión modo esclavo, Lectura desde el esclavo, en modo maestro.

IICIF Bandra de interrupción IIC — El bit IICIF se activa cuando una interrupción esta pendiente. Este bit debe ser borrado por software, escribiendo un 1 en el en la rutina de interrupción. Cualquiera de los siguientes eventos puede activar el bit IICIF: • Se completó la transferencia de un byte. • Coincidencia de la dirección de esclavo con la dirección de llamada. • Pérdida de arbitrariedad.

0 No hay interrupción pendiente.

1 Hay una interrupción pendiente.

RXAK Recepción de Acknowledge— Cuando el bit RXAK esta en bajo, indica que una señal de acknowledge se ha recibido después de la transmisión de un byte de data en el bus. Si el bit RXAK esta en alto significa que no se ha detectado una señal de acknowledge.

0 Señal de acknowledge recibida.

1 No se ha recibido señal de acknowledge.

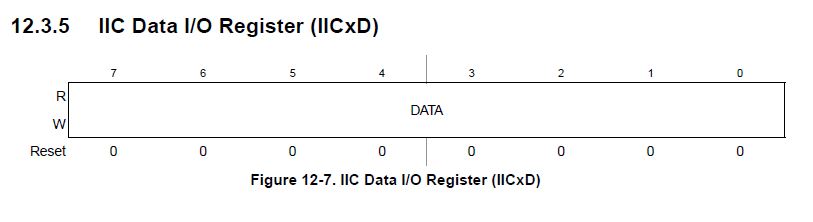

Data — En modo de transmisión maestro, cuando se escribe una data en el registro IICxD, se inicia la transferencia de la data. El bit mas significativo es enviado primero. En modo de transmisión maestro, leer este registro inicia la transferencia del siguiente byte de data.

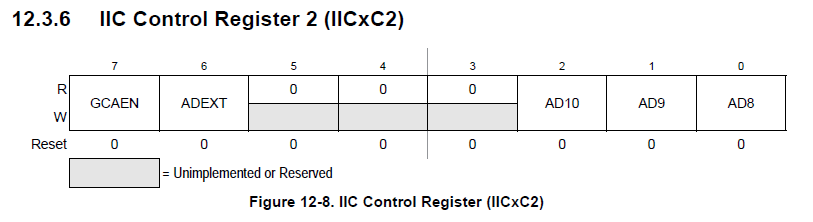

GCAEN Habilitar direcciones de llamada general — El bit GCAEN Habilita o inhabilita las direcciones de llamada general.

0 Direcciones de llamada general inhabilitadas.

1 Direcciones de llamada general habilitadas.

ADEXT Extension de dirección — El bit ADEXT controla el numero de bits usado para las direcciones de esclavo.

0 Esquema de dirección de 7-bits.

1 Esquema de dirección de 10-bits.

AD Dirección de esclavo — EL campo AD contiene los 3 bits mas altos de la dirección de esclavo en el esquema de 10-bits. Este campo es valido sólo si el bit ADEXT bit esta habilitado.

IIC Protocol

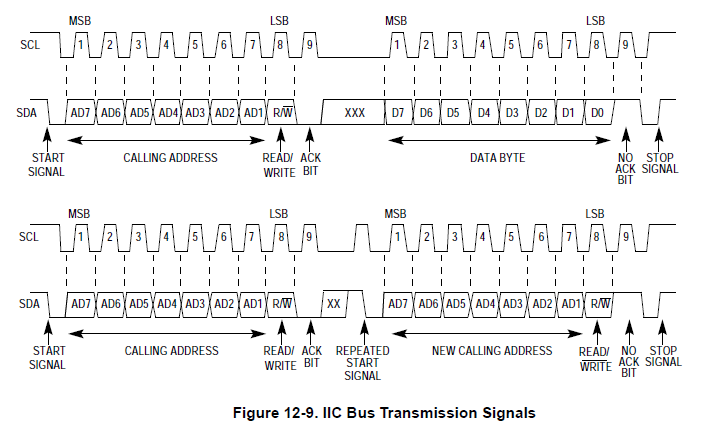

El bus del IIC utiliza na linea de datos serial (SDA) y una linea de reloj serial (SCL) para transferencia de datos. Todos los dispositivos deben tener salidas tipo open-drain o open collector. Un AND lógico se aplica en ambas líneas con resistencias de pull-up externas. El valor de estas resistencias depende del sistema.

Generalmente, una comunicación standard esta compuesta de cuatro partes: • Señal de START. • Transmisión de la dirección de esclavo. • Transferencia de datos. • Señal de STOP. La señal de STOP no se debe confundir con la instrucción de CPU STOP.

Señal de START

Cuando el bus esta libre, ningún dispositivo maestro esta controlando el bus (SCL y SDA estan el 1 lógico), un dispositivo maestro debe iniciar la comunicación enviando una señal de START. Como se muestra en la figura 12-9. Una señal de START se define como el cambio de 1 a cero lógico de la linea SDA mientras SCL esta en 1 lógico. esta señal denota el inicio de una nueva transferencia de datos (cada transmisión de datos debe contener varios bytes de data) y sacar a los esclavos fuera de su estado de espera.

Transmisión de la dirección de esclavo

El primer byte de data transmitido inmediatamente después de la señal de START es la dirección de esclavo transmitida por el maestro. Esta es una dirección de llamada de siete bits seguida por el bit R/W. El bit R/W le dice al esclavo la dirección deseada de la transferencia de datos.

1 = Transferencia tipo lectura, el esclavo transmite data a el maestro.

0 = Transferencia tipo escritura, el maestro transmite data al esclavo.

Sólo el esclavo con una dirección de llamada que coincida con la dirección transmitida por el maestro responderá enviando de vuelta un bit de acknowledge. Esto se logra poniendo en cero lógico la línea SDA en el noveno clock (ver Figura 12-9).

Ningún esclavo en el sistema debe tener la misma dirección de llamada. Si el módulo IIC es el maestro, no debe transmitir una dirección de llamada de esclavo igual a la suya. El IIC no puede ser maestro y esclavo al mismo tiempo.

Si una pérdida de arbitrariedad ocurre durante el ciclo de direccionamiento, el IIC cambiará a modo esclavo.

Transferencia de Datos

Antes de que se logre el direccionamiento correcto del esclavo, la transferencia de datos puede proceder byte por byte en la dirección especificada por el bit R/W enviado por el maestro que realizó la llamada. todas las transferencias de datos que le sigan a un ciclo de direccionamiento se interpretan como transferencia de datos, incluso si contienen información de sub-direcciones para el dispositivo esclavo.Cada byte de datos tiene 8 bits.

Los datos solo pueden cambiar mientras SCL esta en cero lógico y deben ser sostenidos en un estado estable mientras SCL esta en uno lógico como muestra la Figura 12-9.

Estrechamiento del reloj

Existen casos en los cuales es necesario bajar la velocidad de transferencia de bit, para ahorrar energía o una cierta cantidad de ciclos en algún proceso dado. El IIC ofrece la ventaja, al tener el sistema Maestro-Esclavo, de realizar dicha opción. Se puede llegar a esta condición, unicamente bajando el periodo SCL (Serial Clock) del sistema Esclavo, cuando el periodo del SCL del sistema Maestro es bajado.

SCL-SLAVE (low period) > SCL-MASTER (low period) -> Clock Stretching successful

Llamado General a dirección

Estos llamados pueden llegar a ser pedidos en formatos de direcciones de 7 o 10 bits. Para el caso en que el bit de GCAEN (General Call Adress Enable) se encuentra en 1, el IIC iguala la dirección del llamado general, como su propia dirección esclavo, y cuando este responde a dicho llamado, actua como un receptor-esclavo, seguido del 'set' al bit de IAAS después de cada ciclo de dirección.

Es importante recalcar, que el sistema debe leer el registro IICD, luego de transmitir el primer byte. De dicha manera, se comprueba si la dirección en cuestión en su dirección esclavo, o, un llamado general. De ser el valor igual a 00, fue un llamado general.

Por último, si el bit GCAEN mencionado anteriormente se encuentra en 0, el IIC ignora cualquier dato brindado por un llamado general.

Resets

EL módulo IIC se inhabilita después de cada reset. EL IIC no puede causar un reset del MCU.

Interrupciones

El IIC genera una sola interrupción.

Las interrupciones se producen con cualquiera de los eventos de la tabla 12-11 y cuando el bit IICIEesta activado. La bandera IICIF debe ser borrada por software escribiendo un 1 en el, en la rutina de interrupción.

Interrupción de transferencia de byte

La bandera TCF se activa en el borde de bajada al noveno clock para indicar que se ha completado una transferencia.

Interrupción de detección de dirección

Cuando la dirección de llamada coincide con la dirección de esclavo programada en el registro de direccióno cuando el bit GCAEN es activado y una llamada general es recibida, el bit IAAS se activa. El CPU es interrumpido cuando llega una interrupción. El CPU debe verificar el bit SRW y escribirlo de acuerdo al modo de Tx correcto.

Interrupción de pérdida de arbitrariedad

La arbitrariedad se pierde en cualquiera de estas circunstancias:

• Cuando se baja la línea SDA cuando el maestro la mantiene en alto durante un ciclo de dirección o de transmisión. • Cuando se baja la línea SDA cuando el maestro la mantiene en alto durante el envío del bit de acknowledge en un ciclo de datos. • Al tratar de llevarse a cabo un ciclo de START cuando el bus esta ocupado. • Una ciclo de START repetido es solicitado en modo esclavo. • Una condición de STOP es detectada cuando el maestro no la solicitó. Este bit debe ser borrado por software escribiendo un 1 lógico en el.