ADC (Conversor Analógico-Digital) - MC9S08QE128

El módulo ADC del microcontrolador Freescale MC9S08QE128 toma como entrada analógica la señal que resulta al variar el potenciómetro y lo convierte en un valor binario ajustable a 12, 10 y 8 bits

El conversor posee dos señales llamadas Voltage Reference High (V REFH) y Voltage Reference Low (V REFL) y podrá convertir muestras entre V SSAD (Tierra Analógica) y V DDAD que va entre 1.8 y 3.6 Volts

Contenido

Características

El módulo ADC posee:

- Algoritmo de aproximación lineal de 12 bits de resolución

- 32 canales que permiten hasta 28 entradas analógicas

- Formato de salida digital en 12, 10 u 8 bits

- Modo de conversion simple o continua

- Interrupción y bandera para conversiones completadas

- Tiempo de muestreo configurable para el dato de salida

- Reloj para la entrada seleccionable de entre 4 fuentes

- Modos wait y stop3 para operaciones con menos ruido

- Trigger de conversión por hardware seleccionable

- Comparador automatico (mayor que, menor que, igual a) con interrupcion para un valor programable

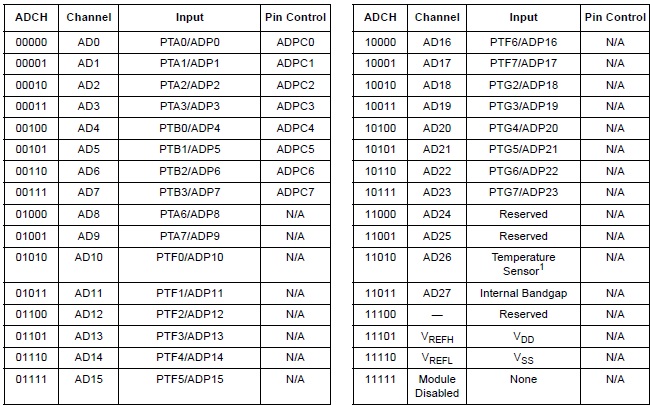

Asignación de canales

El ADC permite hacer las conversiones para cualquier canal entre AD0 y AD23. Si el registro que guarda el canal en el que se quiere trabajar ADCSC1_ADCH(4:0) es igual a 11111, entonces el subsistema que se encarga de convertir será apagado

Sensor de Temperatura

El ADC posee un sensor de temperatura cuya salida esta conectada al canal analógico AD26 y está definida por:

De donde Vtemp es el voltaje del AD26 a la temperatura del ambiente, Vtemp25 es el voltaje del AD26 a 25°C que por datasheet del micro se sabe que es 701.2 mV y m es la pendiente del voltaje vs temperatura que se sabe por datasheet que es 1.646mV desde -40°C hasta 25°C y 1.769 mV desde 25°C hasta 85°C

Para usar el sensor de temperatura será necesario llenar los 5 bits menos significativos del registro ADCSC1 que corresponden al canal que se usará, con el número decimal 26 en binario (11010)

Hardware Trigger

El trigger que inicia una conversión en el ADC puede ser vía software activándolo en un instante de tiempo programable o también puede ser vía hardware. Para esto, el Real Time Counter (RTC) puede ser habilitado como el trigger para cada conversión que se vaya a hacer con el ADC. Basta con configurar el ADCSC2_ADTRG = 1 y asi el ADC hará la conversión cada vez que haya un flanco de subida en el ADHWT que sucederá cuando el RTCINT coincida con RTCMOD

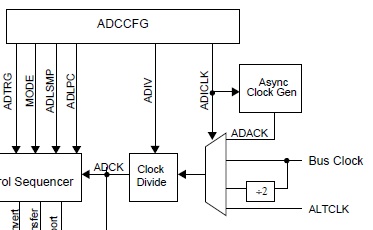

Selección del Clock

Una de las características del ADC es que tiene 4 relojes como fuente para escoger.

El primero es el bus clock, este se selecciona por defecto después de cada reset y trabajará a la misma frecuencia que esté trabajando el micro

La segunda opción es tomar como fuente el mismo bus clock pero el módulo del ADC nos permite dividirlo por 2, 4 y 8 para variar la velocidad de conversión

El tercero es el ALTCLK (alternate clock) que se establece como el ICSERCLK del micro y funciona como el external reference clock La última opción para escoger el clock con el que se quiere trabajar es el ADACK que es un reloj asíncrono que se genera por otro reloj fuente del ADC y se mantiene activo cuando el micro esta en modo stop3 o wait permietiendo conversiones en ambos modos para operaciones con menor ruido

Sin importar el reloj que se haya escogido como fuente, es necesario que la frecuencia con la que se vaya a trabajar esté dentro del rango de frecuencia para el ADCK. Dicho rango esta entre 0.4 Mhz y 8.0 Mhz para conversiones rápidas (High Speed Conversion, bit ADLPC =0) y entre 0.4 Mhz y 4.0 Mhz para conversiones que permiten ahorrar potencia (Low power conversión, bit ADLPC =1).

Modos de conversión

El módulo del ADC permite dos modos de conversión, estas son conversión continua y conversión simple. Estas se pueden configurar con el bit ADC0 del registro de estatus y control ADCSC1 (ver Registros de Control).

- Si fue seleccionado el Hardware trigger y se configura el ADC0 para conversión continua, cada vez que le llegue un flanco de subida a ADHWT el módulo hará la conversión. Si el ADC0 se configura para conversión simple el módulo hará una conversión cuando le llegue un flanco de subida a ADHWT y no iniciará otra si no que se mantendrá ocioso

- Si fue seleccionado Software trigger y se configura configura el ADC0 para conversión continua, cada vez que se escriba en el registro de control ADCSC1 el módulo hará la conversión. Si el ADC0 se configura para conversión simple el módulo hará una conversión cada vez que se escriba en el registro de control ADCSC1 y no iniciará otra si no que se mantendrá ocioso

Registros

Estatus y Control

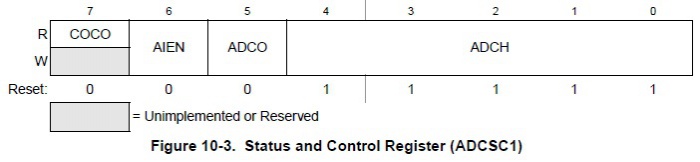

ADCSC1 Estatus y Control 1

Cada vez que se escriba en este registro, se abortará la conversión en curso y se iniciará otra nueva.

- BIT 7 – COCO (Conversion Complete Flag)

Cuando la función de comparar está deshabilitada (ACFE =0), se establecerá la bandera COCO=1 cada vez que que se complete una conversión, de lo contrario será igual a cero (COCO =0). Cuando la función de comparar está habilitada (ACFE =1), se establecerá la bandera COCO =1 cada vez que se haya completado una conversión y el resultado de ésta sea TRUE, de lo contrario COCO =0. El bit COCO se borra cada vez que se escriba en ADCSC1 o cada vez que se lea el registro ADCRL.

- BIT 6 – AIEN (Interrupt Enable)

Este bit habilita las interrupciones que se establecen cuando se ha completado una conversión. Si AIEN =0 se deshabilitan las interrupciones al completar una conversión. Si AIEN =1 se habilitarán las interrupciones cada vez que la bandera COCO se establezca.

- BIT 5 –ADCO (Continuous Conversion Enable)

Si ADCO =0 se selecciona el modo de conversion simple (ver Modos de Conversion). Si ADCO =1 se selecciona el modo de conversión continuo (ver Modos de Conversion).

- BITS 4:0 –ADCH Input cannel select

En estos 5 bits mas bajos del registro ADCSC1 se coloca el valor en binario del canal en el que se quiere trabajar, si el modo de conversión continuo fue seleccionado, se pueden poner estos 5 bits en 1 al finalizar las conversiones para prevenir que otra sea ejecutada, si fue escogido el modo de conversión simple esto no es necesario. (ver Asignacion de Canales)

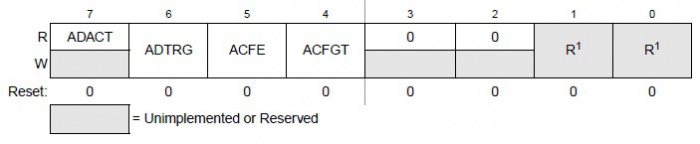

ADCSC2 Estatus y Control 2

Este registro controla la función de comparar, el trigger a usar para la conversión y el indicador de conversión activa

- BIT 7 – ADACT (Conversion Active)

Este bit indica cuando una conversion se esta ejecutando, se establece cuando se inicia una conversión y se borra cuando la misma conversión se completa o se aborta. Si ADACT =0 no se esta ejecutando ninguna conversión. Si ADACT =1 hay una conversión ejecutándose.

- BIT 6 – ADTRG (Conversion Trigger Select)

Este bit se usa para seleccionar qué tipo de trigger se va a usar para inciar una conversión. Si ADTRG = 0 se selecciona software trigger, la conversión se hará cada vez que se escriba en el registro ADCSC1 (ver Modos de Operación). Si ADTRG = 1 se selecciona hardware trigger, la conversión se hará cada vez que le llegue un flanco de subida a ADHWT (ver Hardware Trigger y Modos de Operacion).

- BIT 5 - ACFE (Compare Function Enable)

Habilita la función de comparar (ver ADCSC1_COCO). Si ACFE =0 se deshabilita la funcion comparar. Si ACFE =1 se habilita la funcion comparar.

- BIT 4 - ACFGT (Compare Function Greater Than Enable)

Cuando el resultado de la conversión es mayor o igual que el valor de comparación la función de comparación hace el trigger. Si ACFGT=0 se hace el trigger si la entrada es menor que el valor de comparación. Si ACFGT=1 se hace el trigger si la entrada es mayor o igual que el valor de comparación.

- Los bits 3 y 2 son solo de lectura y son siempre cero, los bits 1 y 2 son de lectura y escritura pero están reservados y su valor siempre deberá ser cero

Contributors

AK, Anairam, Artdamato, Dalak, Fdepasquale, Hyma, Jesus Grimón, Julioa44, LitzaPinto, Luis E Santana P, Minleung, Misato, Ncertad, Racuna