Diferencia entre revisiones de «RTC (Real-timer counter) - MC9S08QE128»

(→RTC Status and Control Register (RTCSC):) |

|||

| Línea 32: | Línea 32: | ||

[[Archivo:RTCSC.jpg|700px|center|thumb|Bits del RTCSC]] | [[Archivo:RTCSC.jpg|700px|center|thumb|Bits del RTCSC]] | ||

| + | |||

| + | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F9" cellpadding="4" | ||

| + | |- valign="bottom" style="background:#F2F2F2" | ||

| + | !Bits | ||

| + | !Descripción | ||

| + | |- | ||

| + | |align="center"|7 | ||

| + | RTIF | ||

| + | |'''Real-TImer Interruption Flag:''' esta bandera indica que el valor del contador del RTC ha llegado al valor esperado. Escribir un 0 no tiene efecto en este registro, pero si se escribe un 1 la bandera se limpia. | ||

| + | 0 = el contador no ha llegado al valor esperado. | ||

| + | |||

| + | 1 = el contador llegó al valor esperado. | ||

| + | |- | ||

| + | |align="center"|6:5 | ||

| + | RTCLKS | ||

| + | |'''Real-Timer Clock Source Select: '''estos bits selecciona la fuente del reloj de entrada que utilizará el RTC para dividir entre los divisores pre-escalados. Cambiar la fuente del reloj limpia el divisor pre-escalado en RTCPS y el contador en RTCCNT. Es importante que cuando se selecciona un reloj se verifique si está habilitado, para el buen funcionamiento del RTC. Resetear RTCLKS produce que se vuelva 00. | ||

| + | 00 = el reloj seleccionado es LPO, de un 1 KHz de frecuencia. | ||

| + | |||

| + | 01 = el reloj seleccionado es el reloj externo (ERCLK). | ||

| + | |||

| + | 1x = el reloj seleccionado es el reloj interno (IRCLCK), de 32 KHz de frecuencia. | ||

| + | |- | ||

| + | |align="center"|4 | ||

| + | RTIE | ||

| + | |'''Real-Timer Interruption Enable:''' este bit habilita la interrupción por RTC. Si RTIE está habilitado entonces se realizará una interrupción cuando RTIF se vuelva 1. Resetear el bit produce que éste se vuelva 0. | ||

| + | |||

| + | 0 = la interrupción no se habilita, se tiene que proceder por encuesta. | ||

| + | |||

| + | 1 = la interrupción está habilitada, así que se realizará cuando RTIF sea 1. | ||

| + | |- | ||

| + | |align="center"|3:0 | ||

| + | RTCPS | ||

| + | |'''Real-Timer Clock Prescaler Select:''' estos cuatros bits sirven para seleccionar el divisor de base 10 o de base 2 que dividirán la frecuencia del reloj seleccionado. Cambiar el divisor produce que RTCCNT se limpie. Si se resetea RTCPS, el valor se vuelve 0. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

Revisión del 15:52 14 nov 2012

Un Real Timer Counter es un contador interno que mantiene la información del tiempo en unidades humanas, donde la unidad básica es el segundo. El RTC está presente en la mayoría de los dispositivos electrónicos que necesitan llevar un registro del tiempo exacto. El término Real Timer Counter es para diferenciar en los contadores del hardware que son señales electrónicas para controlar los circuitos digitales.

Contenido

Configuración en el MC9S08QE128

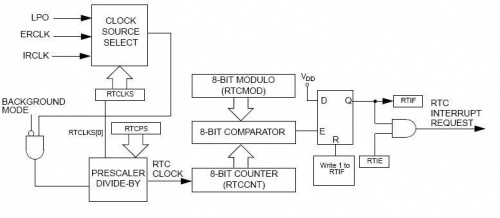

El módulo MC9S08QE128 tiene integrado un Real Timer Counter, que consiste en un comparador uno a uno de 8 bits, un contador uno a uno de 8 bits, diversos divisores pre-escalares de base 2 y de base 10, 3 fuentes de reloj y un vector de interrupción programable.El funcionamiento del RTC se muestra en el siguiente diagrama de bloques:

Se selecciona el reloj correspondiente, mediante el RTCLKS. Siendo estos LPO, low power oscillator, el cual es un reloj interno de 1KHz , ERCLK, reloj externo, IRCLK, reloj interno de 32 KHz, si el BACKGROUND MODE activado el RTC no entra en funcionamiento, se divide por el divisor pre-escalado seleccionado, mediante el RTCPS y el bit 0 del RTCLKS, y esto es guardado en RTCCNT, el cual es comparado bit a bit con RTCMOD, si la comparación es exitosa, se escribe un 1 en RTIF, el cual es limpiado escribiendo un 1 en RTIF,y si, por último RTIE está activo se realiza la solicitud de interrupción por RTC.Modos de funcionamientos:

Wait Mode:

En el modo de espera, el RTC sigue contando si está activado antes de entrar en este modo. Por lo tanto el RTC puede configurarse para que el MCU salga del modo de espera y volver a su funcionamiento normal, si la interrupción por RTC está activa. Si se quiere el menor consumo de corriente en el modo de espera, y si no es necesaria la interrupción, entonces se puede deshabilitar el RTC.

Stop Mode:

En el modo de stop2 y stop3, el RTC sigue corriendo si esta activo antes de producirse la instrucción de STOP, así que por esta razón el RTC puede configurarse para devolver al MCU de un modo de stop, si la interrupción por RTC está activa. Entre los relojes fuentes, el LPO se puede seleccionar en los dos modos de stop, mientras que ERCLK y IRCLK solo se pueden seleccionar en el modo de stop3. De igual manera si se desea el menor consumo de corriente mientras ocurre el modo de stop, se tiene que deshabilitar el RTC, sabiendo que la interrupción por RTC no podrá regresar el MCU a su normal funcionamiento.

Acitve Background Mode:

El RTC suspende cualquier conteo mientras el MCU se encuentra en este modo. El contador se reanuda en el valor que estaba antes suspender el conteo, esto se cumple mientras no se escriba en RTCMOD y los bits de RTCPS Y RTCLKS no sean alterados.

ADC Hardward Trigger:

El RTC se puede configurar para que sea el trigger del Conversor Análogo Digital (ADC) y que se realice la conversión, esto se logra si se activa el ADCSC2[ADTRG]. Cuando esto se realiza el ADC realiza la conversión cada vez que el RTCINT coincide con RTCMOD, es importante saber que la interrupción por RTC no es necesaria que se habilite para que este funcione de esta manera.

Definición de los Registros

RTC Status and Control Register (RTCSC):

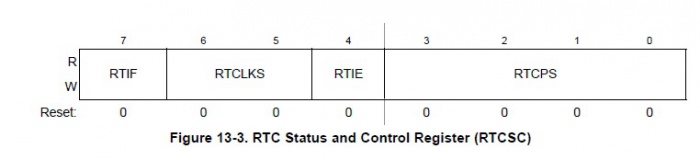

Este registro contiene: la bandera del statu de interrupción (RTIF), el selector del reloj (RTCLKS), el habilitador de la interrupción por RTC (RTIE) y el selector de los divisores pre-escalados (RTCPS). Los bits de estos registros se distribuyen de la siguiente manera:

| Bits | Descripción |

|---|---|

| 7

RTIF |

Real-TImer Interruption Flag: esta bandera indica que el valor del contador del RTC ha llegado al valor esperado. Escribir un 0 no tiene efecto en este registro, pero si se escribe un 1 la bandera se limpia.

0 = el contador no ha llegado al valor esperado. 1 = el contador llegó al valor esperado. |

| 6:5

RTCLKS |

Real-Timer Clock Source Select: estos bits selecciona la fuente del reloj de entrada que utilizará el RTC para dividir entre los divisores pre-escalados. Cambiar la fuente del reloj limpia el divisor pre-escalado en RTCPS y el contador en RTCCNT. Es importante que cuando se selecciona un reloj se verifique si está habilitado, para el buen funcionamiento del RTC. Resetear RTCLKS produce que se vuelva 00.

00 = el reloj seleccionado es LPO, de un 1 KHz de frecuencia. 01 = el reloj seleccionado es el reloj externo (ERCLK). 1x = el reloj seleccionado es el reloj interno (IRCLCK), de 32 KHz de frecuencia. |

| 4

RTIE |

Real-Timer Interruption Enable: este bit habilita la interrupción por RTC. Si RTIE está habilitado entonces se realizará una interrupción cuando RTIF se vuelva 1. Resetear el bit produce que éste se vuelva 0.

0 = la interrupción no se habilita, se tiene que proceder por encuesta. 1 = la interrupción está habilitada, así que se realizará cuando RTIF sea 1. |

| 3:0

RTCPS |

Real-Timer Clock Prescaler Select: estos cuatros bits sirven para seleccionar el divisor de base 10 o de base 2 que dividirán la frecuencia del reloj seleccionado. Cambiar el divisor produce que RTCCNT se limpie. Si se resetea RTCPS, el valor se vuelve 0. |

Contributors

AK, Alecruz185, Anny, Any Isabel Rodriguez, Arieltapia, Arpm92, Dalak, Fdepasquale, Jesus Grimón, Julioa44, Minleung, Misato, Racuna