Diferencia entre revisiones de «Código Acelerometro Rutinas de Interrupción»

| Línea 87: | Línea 87: | ||

tiene hasta ocho fuentes de interrupción. | tiene hasta ocho fuentes de interrupción. | ||

| − | ===Reloj KBI === | + | ====Reloj KBI ==== |

El reloj de bus KBI puede ser activado con el bit KBI en SCGC2. Este bit se restablece después de cualquier | El reloj de bus KBI puede ser activado con el bit KBI en SCGC2. Este bit se restablece después de cualquier | ||

| Línea 93: | Línea 93: | ||

para cuando no esté en uso. | para cuando no esté en uso. | ||

| − | ===Características=== | + | ====Características==== |

Las características de KBI incluyen: | Las características de KBI incluyen: | ||

| Línea 110: | Línea 110: | ||

Esta sección define el funcionamiento KBI en modo espera, modo detenido y modos de depuración de fondo. | Esta sección define el funcionamiento KBI en modo espera, modo detenido y modos de depuración de fondo. | ||

| − | === KBI en el modo de espera=== | + | ==== KBI en el modo de espera==== |

El KBI continúa operando en el modo de espera si está activado antes de ejecutar la instrucción WAIT. Por lo tanto, | El KBI continúa operando en el modo de espera si está activado antes de ejecutar la instrucción WAIT. Por lo tanto, | ||

| Línea 116: | Línea 116: | ||

habilitando (KBIE = 1). | habilitando (KBIE = 1). | ||

| − | === KBI en modos de parada === | + | ==== KBI en modos de parada ==== |

El KBI opera de forma asíncrona en el modo Stop3 si está activado antes de ejecutar la instrucción STOP. | El KBI opera de forma asíncrona en el modo Stop3 si está activado antes de ejecutar la instrucción STOP. | ||

| Línea 126: | Línea 126: | ||

estado de restablecimiento. | estado de restablecimiento. | ||

| − | ===KBI en modo de fondo Activo=== | + | ====KBI en modo de fondo Activo==== |

Cuando el microcontrolador está en modo de fondo activo, el KBI continuará operando normalmente. | Cuando el microcontrolador está en modo de fondo activo, el KBI continuará operando normalmente. | ||

Revisión del 21:01 30 jun 2016

Acelerómetro MMA7660FC

El MMA7660FC es un output digital I²C, de muy bajo consumo de energía, de perfil capacitivo micro-mecanizado con un filtro de paso bajo, con compensación offset para gravedad cero, ganancia de errores y conversión a valores digitales de seis bits van en una salida de datos configurable por el usuario. El dispositivo puede ser utilizado para cambios de datos del sensor, la orientación del producto y la detección de gesticulaciones a través de un pin de interrupción (INT). El dispositivo es de 3 mm x 3 mm x 0,9 mm encapsulado en un DFN (plano, dual y libre de plomo).

Información técnica

Modos de Operación y tipos de Detecciones

•Modos de Operación:

•Modo sin Corriente

•Modo Apagado

•Modo en Espera

•Modo Activo

• Tipos de detecciones:

•Detección de Orientación

•Detección de Golpe

•Detección de Agite

•Auto-Encendido/Apagado

Interfaz Serial

-Direccionamiento Serial.

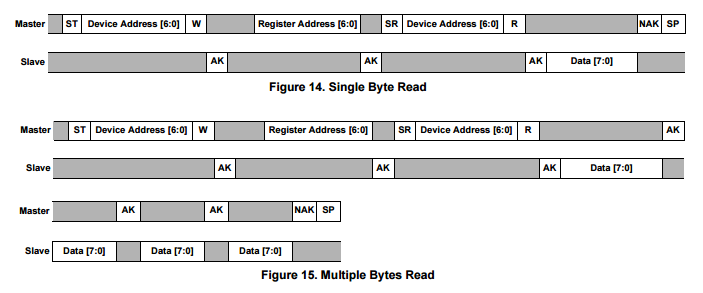

El MMA7660FC funciona como un esclavo que envía y recibe datos a través de una interfaz de 2 hilos I²C. La interfaz utiliza una Serie de Línea de Datos (SDA) y una Línea de Reloj en Serie (SCL) para lograr una comunicación bidireccional entre el maestro (M) y el esclavo (S). Un maestro (típicamente un microcontrolador) inicia todas las transferencias de datos hacia y desde el dispositivo, y genera el reloj SCL que sincroniza la transferencia de datos.

Formato de mensaje de Escritura

Formato de mensaje de lectura

Configuración del TMP

Modulo Periférico Timer/PWM

-- Cuando el MCU entra en el modo de parada, el reloj de los módulos TPM1 y TPM2 se para . los módulos de media

operación . Si la MCU está configurado para entrar en el modo de stop2 o stop1 , los módulos TPM se restablecerán

al despertar de la parada y deben ser reinstaladas .

void StartTPM(byte PS){

TPM1SC = (byte)(0x08 | (0x07&PS));

StartCount = TPM1CNT;

}

word StopTPM(void){

StopCount = (word)(TPM1CNT - StartCount);

TPM1SC = 0;

return StopCount;

}

Rutinas de Interrupción

KBI_ISR

El módulo KBI en se puede considerar como el módulo IRQ extendido. La diferencia entre estos módulos es que el módulo KBI es sensible a varios pines, y el módulo IRQ es sensible a un solo pin. La interrupción del módulo IRQ tiene mayor prioridad que la del módulo KBI. El módulo KBI no necesita ser habilitado desde CONFIG.

En el módulo KBI los modos también son por nivel y/o flanco. Se puede configurar la polaridad en cada pin KBI para que ingrese ya sea por nivel alto y/o flanco de subida o por nivel bajo y/o flanco de bajada. Ademas se puede configurar si un pin queda como pin de propósito general o como pin KBI.

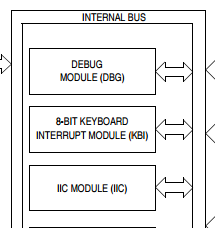

El módulo de interrupciones de teclado (KBI) ofrece hasta ocho fuentes de interrupción externa habilitadas de forma independiente.

Los dispositivos de la Serie MC9S08QE128 contienen dos módulos KBI, llamados KBI1 y KBI2. Cada módulo KBI

tiene hasta ocho fuentes de interrupción.

====Reloj KBI ====

El reloj de bus KBI puede ser activado con el bit KBI en SCGC2. Este bit se restablece después de cualquier reset, que permite que el reloj de bus a este módulo sea activado. Para ahorrar energía, el bit de KBI se puede borrar,desactivar

para cuando no esté en uso.

Características

Las características de KBI incluyen:

• Hasta ocho pines de interrupción del teclado con bits de habilitación para cada uno.

• Cada pin de interrupción del teclado es programable como flanco descendente (o flanco ascendente) solamente, o ambos, flanco descendente y bajo nivel (o ambos flancos de subida y de alto nivel) que interrumpen la sensibilidad.

• Un software permite la activación interrupción del teclado.

• Salir de los modos de bajo consumo.

Modos de operación

Esta sección define el funcionamiento KBI en modo espera, modo detenido y modos de depuración de fondo.

KBI en el modo de espera

El KBI continúa operando en el modo de espera si está activado antes de ejecutar la instrucción WAIT. Por lo tanto, un pasador de KBI habilitado (KBPEx = 1) se puede utilizar para llevar la MCU del modo de espera si la interrupción es KBI habilitando (KBIE = 1).

KBI en modos de parada

El KBI opera de forma asíncrona en el modo Stop3 si está activado antes de ejecutar la instrucción STOP. Por lo tanto, un pasador de KBI habilitado (KBPEx = 1) se puede utilizar para llevar la MCU de modo Stop3 si el KBI

está habilitada (KBIE = 1).

Durante el modo stop2, el KBI se desactiva. Al despertar del modo stop2, el módulo KBI estará en el

estado de restablecimiento.

KBI en modo de fondo Activo

Cuando el microcontrolador está en modo de fondo activo, el KBI continuará operando normalmente.

''interrupt VectorNumber_Vkeyboard ''

#Define KBI_VAL (PTAD&0x0C)>>2

void KBI_ISR(void){

byte d,b;

//capture which pin was pushed

mode = (byte)(KBI_VAL);

//debounce button

for (d=0xff;d>0;d--){

for (b=0x80;b>0;b--){}

}

//clear KBF

KBI1SC_KBACK = 1;

}

IIC_ISR

El Modulo tiene dos registros IIC con hasta 100 kbps de máxima carga del bus ; la operación multi - maestro , direccionamiento de esclavo programable; interrumpir la transferencia de datos byte a byte ;soporta el modo de difusión y 10 bit de direccionamiento

''interrupt VectorNumber_Viicx''

el IIC se puede usar con operaciones donde funge de esclavo, Se enviara una señal que sera la encargada de iniciar la comunicación .

Si se implementa como como maestro inicializaremos la comunicación desde el registro IICD.

void IIC_ISR(void) {

IIC2S_IICIF = 1; // Clear Interrupt Flag

if (IIC2C1_TX) { // Transmit or Receive?

///////////////////// Transmit ////////////////////////////

if (repeat_start_sent) {

IIC2C1_TX = 0; // Switch to RX mode

if (num_to_rec == 1)

IIC2C1_TXAK = 1; // This sets up a NACK

IIC2D; // Dummy read from Data Register

}

else if ((last_byte) & (reading_mma7660_reg)) {

IIC2C1_RSTA = 1; //Repeat start

IIC2D = (mma7660[0] | 0x01); //Set Read bit

repeat_start_sent = 1;

}

else if (last_byte) { // Is the Last Byte?

IIC2C1_MST = 0; // Generate a Stop

}

else if (last_byte != 1) {

if (IIC2S_RXAK) { // Check for ACK

IIC2C1_MST = 0; // No ACk Generate a Stop

}

else if (!IIC2S_RXAK) {

IIC2D = mma7660[count++]; // Transmit Data

if (count == bytes_to_trans)

last_byte = 1;

}

}

} else {

///////////////////// Receive ////////////////////////////

if ((num_to_rec - rec_count) == 2) {

IIC2C1_TXAK = 1; // This sets up a NACK

Master_Read_and_Store();

}

else if ((num_to_rec - rec_count) == 1) {

IIC2C1_MST = 0; // Send STOP

Master_Read_and_Store();

}

else {

Master_Read_and_Store();

}

}

}