Diferencia entre revisiones de «IRQ (External Interrupt Request) - MC9S08QE128»

| Línea 1: | Línea 1: | ||

[[Categoría:MC9S08QE128]] | [[Categoría:MC9S08QE128]] | ||

| − | [[Archivo:IRQpin.jpg]] | + | [[Archivo:IRQpin.jpg|400px|thumb|right|]] |

==''Introducción''== | ==''Introducción''== | ||

Revisión del 12:04 17 mar 2013

Contenido

Introducción

El pin de IRQ se puede usar para activar interrupciones de hardware externas. Dependiendo de la configuración de la MCU, una interrupción por IRQ se genera por nivel bajo o por una transición de nivel alto a nivel bajo en el pin IRQ. Este tipo de interrupción se puede usar para supervisar sistemas externos o eventos.

Las interrupciones externas son manejadas por el registro de control y status del IRQ (IRQSC). Cuando la función del IRQ está habilitada, lógica síncrona supervisa el pin para detectar un flanco descendente o un flanco descendente y nivel bajo. Cuando el MCU está en modo stop o los relojes del sistema estén detenidos, un método asíncrono separado es usado para que el pin IRQ (si este está habilitado) pueda despertar el MCU.

Cada tipo de interrupción tiene una prioridad predefinida asociada. La interrupción del módulo IRQ externa tiene la prioridad más alta, después del evento de Reset y SWI. Cuando ocurren múltiples interrupciones, la CPU primero mira la prioridad de los eventos y servicios del evento con la prioridad más alta, con los otros pendientes.

Configuración del pin IRQ

El IRQPE en el registro IRQSC debe estar habilitado para que el pin IRQ pueda actuar como una entrada por petición de interrupción.

Siendo el IRQ una entrada, el usuario puede escoger la polaridad de los flancos o niveles detectados (IRQEDG) y entre si el pin detecta un flanco o una flaco y nivel (IRQMOD). Cuando el pin de IRQ es habilitado utiliza por default un dispositivo de pull-up o pull-down dependiendo de la polaridad escogida (IRQPDD=0).

La bandera IRQF se levanta cuando se detecta el cambio en el flanco del pin IRQ esperado, y no se puede limpiar la bandera mientras el pin IRQ permanezca en este nivel. La bandera IRQF se limpia forzando IRQACK=1.

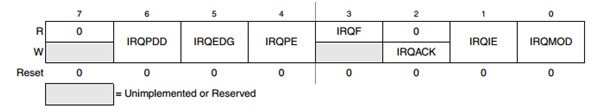

Registro IRQSC

- IRQPDD. Interrupt Request (IRQ) Pull Device Disable: Si el bit IRQPE=1, entonces este bit permite deshabilitar o habilitar los dispositivos de pull-up, dependiendo de la polaridad escogida (IRQPDD). Por default habilita los dispositivos.

- 0 Habilita los dispositivos de pull-up IRQPE=1

- 1 Deshabilita los dispositivos de pull-up IRQPE=1

- IRQEDG. Interrupt Request (IRQ) Edge Select: Este bit permite escoger los la polaridad de los flancos o niveles detectados en el pin IRQ, que causa el levantamiento de la bandera IRQF. Cuando IRQEDG=1 y se habilita el dispositivo de pull-up, este es reconfigurado como un dispositivo opcional pull-down.

- 0 el pin IRQ es sensible a un flanco descendente o un flanco descendente y nivel bajo

- 1 el pin IRQ es sensible a un flanco ascendente o un flanco ascendente y nivel alto

- IRQPE. IRQ Pin Enable: Este bit habilita la función del pin IRQ. IRQPE debe ser 1 para que el pin IRQ pueda actuar como una entrada por petición de interrupción.

- 0 Función del pin IRQ deshabilitada

- 1 Función del pin IRQ habilitada

- IRQF. IRQ Flag: Este bit indica si ha ocurrido una petición de interrupción.

- 0 No se detecto una petición por IRQ

- 1 Se detecto un evento del IRQ

- IRQACK. IRQ Acknowledge: Este bit permite limpiar la bandera IRQF si se fuerza IRQACK=1. Forzarla a 0 no tiene ningún significado o efecto. La lectura de este bit siempre retorna 0.

- IRQIE. IRQ Interrupt Enable: Este bit de control determina si los eventos del IRQ generan una petición de interrupción

- 0 Deshabilitadas las peticiones de interrupción cuando IRQF=1

- 1 Habilitadas las peticiones de interrupción cuando IRQF=1

- IRQMOD. IRQ Detection Mode: Este bit de control determina si el pin de IRQ es sensible a un único flanco o a un flanco y nivel.

- 0 sensible sólo a flancos descendentes o flacos ascendentes

- 1 sensible a flanco descendente y nivel bajo o flanco ascendente y nivel alto

Inicialización

Cuando se habilita por vez primera el pin de IRQ, es posible obtener una falsa bandera de interrupción. Para evitar esta falsa petición de interrupción, se debe inicializar el IRQ de la siguiente manera:

- Limpiar el IRQIE en el IRQSC

- Seleccionar la polaridad del pin forzando el bit apropiado en el IRQEDG del IRQSC

- Si se va a utilizar un dispositivo de pull-up/pull-down, limpiar el bit IRQPDD en el IRQSC

- Habilitar el pin IRQ forzando el bit apropiado en el IRQPE del IRQSC

- Colocar un 1 en el IRQACK del IRQSC para limpiar cualquier falsa interrupción

- Colocar un 1 en el IRQIE del IRQSC para habilitar las interrupciones.

Además del IRQSC se debe configurar el registro SCGC2 (System Clock Gating Control Register 2) para que el pin RESET tenga función IRQ, en vez de RESET. Esto se logra colocando un 0 en el bit RSTPE del registro

BSET IRQSC_IRQPE, IRQSC ; Se habilita el pin IRQ

BSET IRQSC_IRQACK, IRQSC ; Se limpia cualquier posible falsa interrupción previa

BSET IRQSC_IRQIE, IRQSC ; Se habilitan las interrupciones del pin IRQ

Referencias

Contributors

Anny, Artdamato, CeMoron, LuisiVelas, MaAndreinaCane, Racuna, Vegabante