Diferencia entre revisiones de «PWM (Modulación de Ancho de Pulso)»

De Wikitronica

| Línea 3: | Línea 3: | ||

[[Categoría: EC3883 - Laboratorio de Proyectos 3]] | [[Categoría: EC3883 - Laboratorio de Proyectos 3]] | ||

[[Categoría: MC9S08QE128]] | [[Categoría: MC9S08QE128]] | ||

| + | |||

| + | ==Introduccion== | ||

| + | ===Configuracion=== | ||

| + | |||

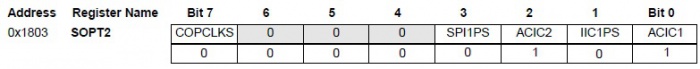

| + | El comparador analogico (ACMP) puede ser configurado para conectarse el a un canal TPM de entrada, colocando el bit SOPT2 [ACICx] en uno. Haciendo esto, el pin del canal 0 del TPM no está disponible de forma externa, es decir no puede ser modificado. La salida del ACMP 1 puede conectarse a TPM1CH0 y la salida del ACMP2 puede conectarse a TPM2CH0. | ||

| + | [[Archivo:Untitled.jpg|700px|center|thumb|'''Configuracion del modulo SOPT2 para conectar el ACMP a los canales del TPM''']] | ||

| + | |||

| + | ===Compuerta de clocks=== | ||

| + | |||

| + | Los buses del reloj de los modulos TPM1, TPM2 y TPM3 pueden activarse o desactivarse usando el modulo SCGC1 [TPMx]. Cuando los bits están en 1, los puertos se habilitan dejando usar los clocks de cada módulo, y en cero se desabilitan. Luego de un reset estos bits se colocan en 1. | ||

| + | |||

| + | ===Vector de interrupciones=== | ||

| + | ===Caracteristicas=== | ||

| + | ===Modos de operacion=== | ||

| + | ==Registros== | ||

| + | ===TPMxSC=== | ||

| + | ===TPMxCNTH:TPMxCNTL=== | ||

| + | ===TPMxMODH:TPMxMODL=== | ||

| + | ===TPMxCnSC=== | ||

| + | ===TPMxCnVH:TPMxCnVL=== | ||

| + | ==Reset== | ||

| + | ==Interrupciones== | ||

Revisión del 10:31 16 nov 2012

Claudio Imbriaco

Contenido

Introduccion

Configuracion

El comparador analogico (ACMP) puede ser configurado para conectarse el a un canal TPM de entrada, colocando el bit SOPT2 [ACICx] en uno. Haciendo esto, el pin del canal 0 del TPM no está disponible de forma externa, es decir no puede ser modificado. La salida del ACMP 1 puede conectarse a TPM1CH0 y la salida del ACMP2 puede conectarse a TPM2CH0.

Compuerta de clocks

Los buses del reloj de los modulos TPM1, TPM2 y TPM3 pueden activarse o desactivarse usando el modulo SCGC1 [TPMx]. Cuando los bits están en 1, los puertos se habilitan dejando usar los clocks de cada módulo, y en cero se desabilitan. Luego de un reset estos bits se colocan en 1.

Vector de interrupciones

Caracteristicas

Modos de operacion

Registros

TPMxSC

TPMxCNTH:TPMxCNTL

TPMxMODH:TPMxMODL

TPMxCnSC

TPMxCnVH:TPMxCnVL

Reset

Interrupciones

Contributors

AK, Dalak, Francjsalanova, Leofragachan, Minleung, Misato, Nivmizzet, Racuna, Vegabante