Diferencia entre revisiones de «Debug Module (DBG)(128k)- MC9S08QE128»

(→Resets) |

(→Referencias y Enlaces) |

||

| Línea 1221: | Línea 1221: | ||

<br> | <br> | ||

*[http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf''MC9S08QE128RM Reference Manual''] | *[http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf''MC9S08QE128RM Reference Manual''] | ||

| − | |||

| − | |||

*[http://es.wikipedia.org/wiki/Depuraci%C3%B3n_de_programas| Debug - Depuración de Programas] | *[http://es.wikipedia.org/wiki/Depuraci%C3%B3n_de_programas| Debug - Depuración de Programas] | ||

<br> | <br> | ||

Revisión del 09:41 26 nov 2012

Contenido

- 1 Módulo de Debug (DBG):

- 2 Características Generales

- 3 Mapa de Memoria

- 4 Registros

- 4.1 Comparador A (Parte Alta DBGCAH)

- 4.2 Comparador B (Parte Alta DBGCBH)

- 4.3 Comparador C (Parte Alta DBGCCH)

- 4.4 Registro FIFO (Parte Alta DBGCFH)

- 4.5 Registros de Extensión de los Comparadores A (DBGCAX) ,B (DBGCBX) y C(DBGCCX)

- 4.6 Registro de Información Extendida FIFO (DBGCFX)

- 4.7 Registro de Control (DBGC)

- 4.8 Registro de Disparador (Trigger - DBGT)

- 4.9 Registro de Estado (DBGS)

- 4.10 Registro de Conteo FIFO (DBGCNT)

- 5 Funcionamiento del Módulo

- 6 FIFO - Almacenamiento de datos

Módulo de Debug (DBG):

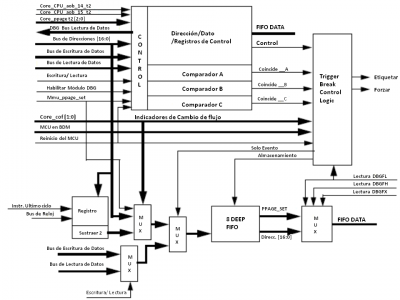

El Módulo de Depuración o ‘Debug Module’ DBG forma parte del desarrollo de sistemas de apoyo del microcontrolador. Si bien el control de depuración de respaldo ‘Background Debug Controller’ (BDC) es la interfaz de depuración primaria del MC9S08QE128, el módulo en circuito DBG opera de manera análoga a éste: es no intrusivo, permite el acceso a los datos de la memoria y mantiene las características tradicionales de depuración como modificar el registro de la CPU, puntos de interrupción, y traza de una sola instrucción.

El módulo DBG, proporciona una interfaz para activar y capturar de forma selectiva, la información del bus. De este modo, implementando un sistema externo se puede reconstruir lo que ocurre en la MCU ciclo a ciclo, sin necesidad de acceder externamente a las direcciones ni datos.

Conceptos

La palabra Debug en el área de programación se refiere a la identificación, eliminación y corrección de fallos o errores en el programa.(2*).

Por tanto al referirse a un Bug dentro del programa, se habla de errores menores o graves que afectan al sistema y la programación y afecta su efectividad y calidad.

Características Generales

El DBG emplea un chip para la emulación en circuito (ICE) con las siguientes características:

| Nº | Característica principal | Descripción |

|---|---|---|

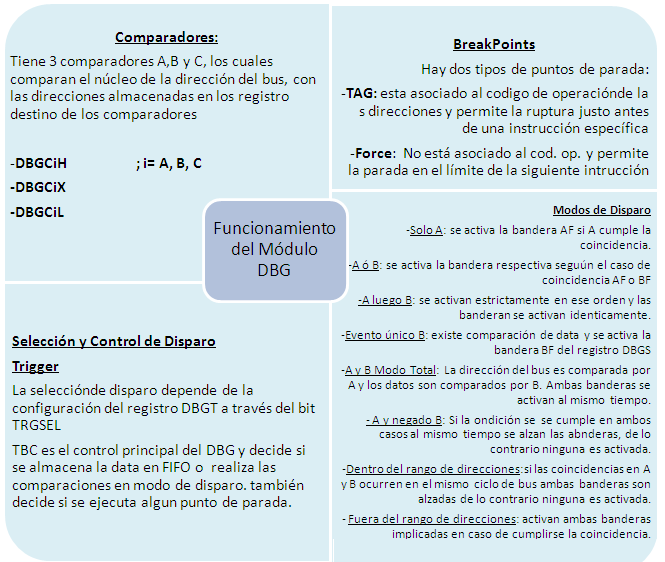

| 1 | Tres comparadores A,B y C con la posibilidad de señalar direcciones en hasta 128 Kbytes de espacio de memoria |

|

| 2 | Nueve modos de disparo o activación (triggers) |

|

| 3 | Organización de la data según FIFO (first in, first out)para almacenamiento de la información del cambio de flujo de data y/o eventos |

|

| 4 | Capacidad de comenzar rastreo desde el reinicio o terminar el rastreo hasta el reinicio |

|

| 5 | Etiqueta y forza puntos de parada (Breakpoints) | --- |

| 6 | No posee, ni depende de los siguientes items: |

|

Ventajas del DBG

¿Para qué se implementa el DBG?

¡Fácil! Permite poder programar el seguimiento e identificación de errores de mi sistema en tiempo real. Representa una medida de prevención de errores cuando se trata de sistemas o programas complejos y extensos. También permite conocer el estado de los resgistros y datos, los cuales soporta hasta 128KBytes en espacio de memoria.El Módulo de Debug opera de modo no intrusivo con un solo pin, no compromete grandes gastos de potencia ni recursos de hardware. Además ofrece múltiples posibilidades de aplicación de 'BREAK POINTS' (puntos de parada o de prueba): por Posición de PC, por Condicionales (A=B, A>B,A<B, entre otros.), lo cual permitirá la identificación de errores en las áreas del sistema de programa deseadas.

En conjunto con el BDM representa una herramienta para asegurar la calidad del programa.

Modos de Operación

EL modulo DBG puede ser habilitado en todos los modos funcionales del MCU. Es deshabilitado si el MCU es asegurado y los comparadores son deshabilitados cuando se ejecuta el comando para modo BDM.

El bus de reloj al DBG puede abrirse o cerrarse usando el bit SCGC2 del DBG. Este bit es puesto en alta (1) luego de cada reinicio, lo cual habilita el bus. Y en caso de que no se requiera el uso del módulo y para conservar la energía, este bit es puesto en nivel bajo (0).

Mapa de Memoria

La siguiente tabla muestra detalladamente los registros de los cuales dispone el módulo y de los cuales puede disponer el usuario final. Además se indica el área de memoria al cual corresponden y el tipo de acceso a los mismos:

| Dirección | Uso | Acceso |

|---|---|---|

| Base + $0000 | Comparador A (Parte Alta DBGCAH) | Lectura/Escritura |

| Base + $0001 | Comparador A (Parte Baja DBGCAL) | Lectura/Escritura |

| Base + $0002 | Comparador B (Parte Alta DBGCBH) | Lectura/Escritura |

| Base + $0003 | Comparador B (Parte Baja DBGCBL) | Lectura/Escritura |

| Base + $0004 | Comparador C (Parte Alta DBGCCH) | Lectura/Escritura |

| Base + $0005 | Comparador C (Parte Baja DBGCCL) | Lectura/Escritura |

| Base + $0006 | Registro FIFO (Parte Alta DBGFH) | Solo Lectura |

| Base + $0007 | Registro FIFO (Parte Baja DBGFL) | Solo Lectura |

| Base + $0008 | Registro de Extensión Comparador A (DBGCAX) | Lectura/Escritura |

| Base + $0009 | Registro de Extensión Comparador B (DBGCBX) | Lectura/Escritura |

| Base + $000A | Registro de Extensión Comparador C (DBGCCX) | Lectura/Escritura |

| Base + $000B | Registro de Información Extendida FIFO (DBGCFX) | Solo Lectura |

| Base + $000C | Registro de Control (DBGC) | Lectura/Escritura |

| Base + $000D | Registro de Disparador (Trigger -DBGT-) | Lectura/Escritura |

| Base + $000E | Registro de Estado (DBGS) | Solo Lectura |

| Base + $000F | Registro de Conteo FIFO (DBGCNT) | Solo Lectura |

Registros

Cada registro disponible para el usuario final tiene una función específica, bien sea para la compararción de datos o direcciónes o para la organización de los mismos. Se presenta a continuación una herramienta de rápida referencia a cada tipo de registro y sus características, ordenados por orden de dirección:

Comparador A (Parte Alta DBGCAH)

Compara los bits de control [15:8]; si en A se compara la dirección del bus con un 1 ó 0 lógico.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| Escritura | " | " | " | " | " | " | " | " |

| Power-on Reset | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

| [15:8]Compara la dirección con 0 lógico | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| [15:8]Compara la dirección con 1 lógico | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Comparador A (Parte Baja DBGCAL)

Compara los bits de control [7:0]; si en A se compara la dirección del bus con un 1 ó 0 lógico.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Escritura | " | " | " | " | " | " | " | " |

| Power-on Reset | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

| [7:0]Compara la dirección con 0 lógico | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| [7:0]Compara la dirección con 1 lógico | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Comparador B (Parte Alta DBGCBH)

Compara los bits de control [15:8]; si en B se compara la dirección del bus con un 1 ó 0 lógico. no es usado en MODO TOTAL

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| Escritura | " | " | " | " | " | " | " | " |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

| [15:8]Compara la dirección con 0 lógico | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| [15:8]Compara la dirección con 1 lógico | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Comparador B (Parte Baja DBGCBL)

Compara los bits de control [7:0]; si en B se compara la dirección del bus con un 1 ó 0 lógico.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Escritura | " | " | " | " | " | " | " | " |

| Power-on Reset | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

| [7:0]Compara la dirección con 0 lógico/con dato en Modo total | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| [7:0]Compara la dirección con 1 lógico/con dato en Modo total | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Comparador C (Parte Alta DBGCCH)

Compara los bits de control [15:8]; si en C se compara la dirección del bus con un 1 ó 0 lógico.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| Escritura | " | " | " | " | " | " | " | " |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

| [15:8]Compara la dirección con 0 lógico | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| [15:8]Compara la dirección con 1 lógico | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Comparador C (Parte Baja DBGCCL)

Compara los bits de control [7:0]; si en C se compara la dirección del bus con un 1 ó 0 lógico.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Escritura | " | " | " | " | " | " | " | " |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

| [7:0]Compara la dirección con 0 lógico/con dato en Modo total | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| [7:0]Compara la dirección con 1 lógico/con dato en Modo total | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Registro FIFO (Parte Alta DBGCFH)

Los bits de datos de alta FIFO proporcionan acceso a los bits [15:08] de datos en la FIFO. Este registro no se utiliza en el Modo de Solo evento y leerá un $ 00 para palabras FIFO válidos.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| Escritura | x | x | x | x | x | x | x | x |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

Registro FIFO (Parte Baja DBGCFL)

los bits bajos de FIFO, contienen el byte menos significativo de la FIFO. Cuando se leen palabras por FIFO, primero lee DBGFX y DBGFH, antes leer DBGFL, porque este causa que el apuntador de FIFO avance a la siguiente dirección. No es necesario en el Modo de solo evento.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Escritura | x | x | x | x | x | x | x | x |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | U | U | U | U | U | U |

Registros de Extensión de los Comparadores A (DBGCAX) ,B (DBGCBX) y C(DBGCCX)

RWAEN: controla si está habilitado lectura/escritura para A/ B (Modo total)/C. for Comparator A.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | RWAEN | RWA | PAGSEL | 0 | 0 | 0 | 0 | Bit 16 |

| Escritura | RWAEN | RWA | PAGSEL | x | x | x | x | Bit 16 |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | U | 0 | 0 | 0 | 0 | U |

| Funciones por Bits | Usado R/W en comparación =1 No Usado R/W en comparación =0

|

Se comparará: Ciclo de Escritura =0 Ciclo de Lectura=1

|

* =0 ** =1

|

x | x | x | x | Comparar bit con: 1 lógico =1 0 lógico =0

|

-* =0 . Corresponde a una dirección de la CPU de 17 bits con un cero en el bit 16 ó una dirección lineal de 17 bits del apuntador. -**=1 . Corresponde a una comparación de una dirección de la memoria flash.

Registro de Información Extendida FIFO (DBGCFX)

PPACC:Este bit indica si la información capturada en la palabra actual es FIFO y está asociada con un acceso extendido a través del mecanismo ppage o no. Esto está indicado por la señal interior cuando mmu_ppage_sel= 1, el acceso es a través del mecanismo de ppage.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | PPACC | 0 | 0 | 0 | 0 | 0 | 0 | Bit 16 |

| Escritura | x | x | x | x | x | x | x | x |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | 0 | 0 | 0 | 0 | 0 | 0 | U |

| Funciones por Bits | Dato de solo evento =1 Dirección de memoria flash =0

|

x | x | x | x | x | x | Bit más significativo de la dirección de 17 bits del núcleo.

|

Registro de Control (DBGC)

DBGEN: habilita el módulo DBG.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | DBGEN | ARM | TAG | BRKEN | 0 | 0 | 0 | LOOP1 |

| Escritura | DBGEN | ARM | TAG | BRKEN | x | x | x | LOOP1 |

| Power-on Reset | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | 0 | U | 0 | 0 | 0 | 0 | U |

| Funciones por Bits | DBG Habilitado =1 DBG no habilitado =0

|

Depurador armado =1 DBG no armado =0

|

Force requerido =0 Tag requerido =0

|

Parada de CPU habilitada =1 Parada de CPU no habilitada =0

|

x | x | x | Modo captura normal =0 Modo Loop1 =1

|

Registro de Disparador (Trigger - DBGT)

TRGSEL: determina la condición de disparo de los comparadores

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | TRGSEL | BEGIN | 0 | 0 | TRG | TRG | TRG | TRG |

| Escritura | TRGSEL | BEGIN | x | x | TRG | TRG | TRG | TRG |

| Power-on Reset | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | U | U | 0 | 0 | U | U | U | U |

| Funciones por Bits | Activo en cualquier comparación de dirección de acceso =1 Activo si es ejecutado el código de operación =0

|

Activo al final de almacenar data =0 Activo antes de almacenar data =1

|

x | x | Modo de DBG | Modo de DBG | Modo de DBG | Modo de DBG |

Registro de Estado (DBGS)

AF: indica si el comparador A realizó coincidencia.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | AF | BF | CF | 0 | 0 | 0 | 0 | ARMF |

| Escritura | x | x | x | x | x | x | x | x |

| Power-on Reset | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| Reinicio End-Run | U | U | U | 0 | 0 | 0 | 0 | 0 |

| Funciones por Bits | A hizo match =1 si no =0

|

B hizo match =1 si no =0

|

C hizo match =1 si no =0

|

x | x | x | Depurador armado =1 si no =0

|

Registro de Conteo FIFO (DBGCNT)

CNT: este conjunto de bit indican la cantidad de data válida almacenada por FIFO. Se detendrá cada 8 palabras válidas.

| Función de campo | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Lectura | 0 | 0 | 0 | 0 | CNT | CNT | CNT | CNT |

| Escritura | x | x | x | x | x | x | x | x |

| Power-on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reinicio End-Run | 0 | 0 | 0 | 0 | U | U | U | U |

| Funciones por Bits | x | x | x | x | # de palabras válidas | # de palabras válidas | # de palabras válidas | # de palabras válidas |

Funcionamiento del Módulo

FIFO - Almacenamiento de datos

Toda la data almacenada en FIFO cambiará de flujo de dirección para cualquier modo de operación excepto para el Modo de solo evento. En éste modo sólo el valor del bus de datos es almacenado. Por otra parte, la dirección guardada en FIFO estará determinada por el cambio de flujo de indicadores desde el núcleo.

- La señal de Core_Cof(1), indica que la corriente dirección es el destino de dirección de algún salto o instrucción indirecta tipo JSR o JMP.

- La señal Core_Cof(0) indica que un salto condicional fue tomado y a su vez la fuente de la dirección del sato fue almacenada.

Almacenamiento de data al inicio de Disparo y al final de Disparo

Inicio de Disparo:Este tipo de almacenamiento puede ser usado en cualquier modo de operación. Una vez que que el Módulo DBG es habilitado, la data no se almacena hasta que coincide con la condición de disparo. Así el módulo se encontrará armado hasta que haya almacenado palabras en la FIFO.

Final de Disparo: es usado en todos los modos de operación exceptuando el modo de solo evento.Una vez que que el Módulo DBG es habilitado, la data no se almacena hasta que coincide con la condición de disparo.

- Si la señal core_cof[1]es acertada, la dirección actual es almacenada en FIFO

- Si la señal core_cof[0] es acertada, la dirección registrada durante el previo ciclo, es decrementada en 2 y almacenada.

Resets

El módulo DBG no puede causar el reinicio del MCU. Existen dos modos de respuesta a reinicios, dependiendo de las características previas al evento que produjo el reinicio:

Las condiciones para empezar la traza por defecto son:

- DBGCAX=0x00; _ //no hay extensión de dirección

- DBGCAH=0xFF; _ // parte alta de la dirección del bus.

- DBGCAL=0xFE; _ // El comparador A es puesto en alta para coincidir cuando aparezca la dirección de CPU 0xFFFE aparezca durante el vector de busqueda.

- DBGC=0xC0; _ // Para habilitar el Módulo y el armado del mismo.

- DBGT=0x40; _ // Selecciona el tipo de disparo y el modo de operación.

Referencias y Enlaces

Contributors

Any Isabel Rodriguez, Jesus Grimón, LitzaPinto, Minleung, Misato