Diferencia entre revisiones de «ADC (Conversor Analógico-Digital) - MC9S08QE128»

(→Ejemplo con vector de interrupcion) |

|||

| Línea 5: | Línea 5: | ||

[[Archivo:potenciometro2.jpg|500px|right|thumb|Potenciometro ADC]] | [[Archivo:potenciometro2.jpg|500px|right|thumb|Potenciometro ADC]] | ||

| − | ==Características== | + | == Características == |

El módulo ADC posee: | El módulo ADC posee: | ||

| Línea 20: | Línea 20: | ||

* ''Comparador automático (mayor que, menor que, igual a) con interrupción para un valor programable'' | * ''Comparador automático (mayor que, menor que, igual a) con interrupción para un valor programable'' | ||

| − | ===Asignación de canales=== | + | === Asignación de canales === |

[[Archivo:canales.jpg|700px|center|thumb|canales ADC]] | [[Archivo:canales.jpg|700px|center|thumb|canales ADC]] | ||

| Línea 27: | Línea 27: | ||

Si el registro que guarda el canal en el que se quiere trabajar ADCSC1_ADCH(4:0) es igual a 11111, entonces el subsistema que se encarga de convertir será apagado | Si el registro que guarda el canal en el que se quiere trabajar ADCSC1_ADCH(4:0) es igual a 11111, entonces el subsistema que se encarga de convertir será apagado | ||

| − | ====Sensor de Temperatura==== | + | ==== Sensor de Temperatura ==== |

El ADC posee un sensor de temperatura cuya salida esta conectada al canal analógico AD26 y está definida por: | El ADC posee un sensor de temperatura cuya salida esta conectada al canal analógico AD26 y está definida por: | ||

| Línea 37: | Línea 37: | ||

Para usar el sensor de temperatura será necesario llenar los 5 bits menos significativos del registro ADCSC1 que corresponden al canal que se usará, con el número decimal 26 en binario (11010) | Para usar el sensor de temperatura será necesario llenar los 5 bits menos significativos del registro ADCSC1 que corresponden al canal que se usará, con el número decimal 26 en binario (11010) | ||

| − | ===Hardware Trigger=== | + | === Hardware Trigger === |

El trigger que inicia una conversión en el ADC puede ser vía software activándolo en un instante de tiempo programable o también puede ser vía hardware. Para esto, el Real Time Counter ([[RTC (Real-timer counter) - MC9S08QE128|RTC]]) puede ser habilitado como el trigger para cada conversión que se vaya a hacer con el ADC. | El trigger que inicia una conversión en el ADC puede ser vía software activándolo en un instante de tiempo programable o también puede ser vía hardware. Para esto, el Real Time Counter ([[RTC (Real-timer counter) - MC9S08QE128|RTC]]) puede ser habilitado como el trigger para cada conversión que se vaya a hacer con el ADC. | ||

| − | |||

| − | |||

| − | ===Selección del Clock=== | + | Basta con configurar el ADCSC2_ADTRG = 1 y asi el ADC hará la conversión cada vez que haya un flanco de subida en el ADHWT que sucederá cuando el RTCINT coincida con RTCMOD |

| + | |||

| + | === Selección del Clock === | ||

Una de las características del ADC es que tiene 4 relojes como fuente para escoger. | Una de las características del ADC es que tiene 4 relojes como fuente para escoger. | ||

| + | |||

[[Archivo:adcclocks.jpg|700px|right|thumb|Bloques_Clocks_ADC]] | [[Archivo:adcclocks.jpg|700px|right|thumb|Bloques_Clocks_ADC]] | ||

| + | |||

El primero es el bus clock, este se selecciona por defecto después de cada reset y trabajará a la misma frecuencia que esté trabajando el micro | El primero es el bus clock, este se selecciona por defecto después de cada reset y trabajará a la misma frecuencia que esté trabajando el micro | ||

| Línea 56: | Línea 58: | ||

Sin importar el reloj que se haya escogido como fuente, es necesario que la frecuencia con la que se vaya a trabajar esté dentro del rango de frecuencia para el ADCK. Dicho rango esta entre 0.4 Mhz y 8.0 Mhz para conversiones rápidas (High Speed Conversion, bit ADLPC =0) y entre 0.4 Mhz y 4.0 Mhz para conversiones que permiten ahorrar potencia (Low power conversión, bit ADLPC =1). | Sin importar el reloj que se haya escogido como fuente, es necesario que la frecuencia con la que se vaya a trabajar esté dentro del rango de frecuencia para el ADCK. Dicho rango esta entre 0.4 Mhz y 8.0 Mhz para conversiones rápidas (High Speed Conversion, bit ADLPC =0) y entre 0.4 Mhz y 4.0 Mhz para conversiones que permiten ahorrar potencia (Low power conversión, bit ADLPC =1). | ||

| − | ===Modos de conversión=== | + | === Modos de conversión === |

| − | El módulo del ADC permite dos modos de conversión, estas son conversión continua y conversión simple. Estas se pueden configurar con el bit ADC0 del registro de estatus y control ADCSC1 (ver Registros de Control). | + | El módulo del ADC permite dos modos de conversión, estas son conversión continua y conversión simple. Estas se pueden configurar con el bit ADC0 del registro de estatus y control ADCSC1 (ver Registros de Control). |

| − | *Si fue seleccionado el '''Hardware trigger''' y se configura el ADC0 para '''conversión continua''', cada vez que le llegue un flanco de subida a ADHWT el módulo hará la conversión. Si el ADC0 se configura para '''conversión simple''' el módulo hará una conversión cuando le llegue un flanco de subida a ADHWT y no iniciará otra si no que se mantendrá ocioso | + | * Si fue seleccionado el '''Hardware trigger''' y se configura el ADC0 para '''conversión continua''', cada vez que le llegue un flanco de subida a ADHWT el módulo hará la conversión. Si el ADC0 se configura para '''conversión simple''' el módulo hará una conversión cuando le llegue un flanco de subida a ADHWT y no iniciará otra si no que se mantendrá ocioso |

| − | *Si fue seleccionado '''Software trigger''' y se configura configura el ADC0 para '''conversión continua''', cada vez que se escriba en el registro de control ADCSC1 el módulo hará la conversión. Si el ADC0 se configura para '''conversión simple''' el módulo hará una conversión cada vez que se escriba en el registro de control ADCSC1 y no iniciará otra si no que se mantendrá ocioso | + | * Si fue seleccionado '''Software trigger''' y se configura configura el ADC0 para '''conversión continua''', cada vez que se escriba en el registro de control ADCSC1 el módulo hará la conversión. Si el ADC0 se configura para '''conversión simple''' el módulo hará una conversión cada vez que se escriba en el registro de control ADCSC1 y no iniciará otra si no que se mantendrá ocioso |

| − | ==Registros== | + | == Registros == |

| − | ===Estatus y Control=== | + | === Estatus y Control === |

| − | ====ADCSC1 Estatus y Control 1==== | + | ==== ADCSC1 Estatus y Control 1 ==== |

Cada vez que se escriba en este registro, se abortará la conversión en curso y se iniciará otra nueva. | Cada vez que se escriba en este registro, se abortará la conversión en curso y se iniciará otra nueva. | ||

| Línea 74: | Línea 76: | ||

[[Archivo:adcsc1.jpg|700px|center|thumb|Registro ADCSC1]] | [[Archivo:adcsc1.jpg|700px|center|thumb|Registro ADCSC1]] | ||

| − | *BIT 7 – '''COCO (Conversion Complete Flag)''' | + | * BIT 7 – '''COCO (Conversion Complete Flag)''' |

| + | |||

Cuando la función de comparar está inhabilitada (''ACFE =0''), se establecerá la bandera '''COCO=1''' cada vez que que se complete una conversión, de lo contrario será igual a cero ('''COCO =0'''). | Cuando la función de comparar está inhabilitada (''ACFE =0''), se establecerá la bandera '''COCO=1''' cada vez que que se complete una conversión, de lo contrario será igual a cero ('''COCO =0'''). | ||

| Línea 81: | Línea 84: | ||

El bit COCO se borra cada vez que se escriba en ADCSC1 o cada vez que se lea el registro ADCRL. | El bit COCO se borra cada vez que se escriba en ADCSC1 o cada vez que se lea el registro ADCRL. | ||

| − | *BIT 6 – '''AIEN (Interrupt Enable)''' | + | * BIT 6 – '''AIEN (Interrupt Enable)''' |

| + | |||

Este bit habilita las interrupciones que se establecen cuando se ha completado una conversión. | Este bit habilita las interrupciones que se establecen cuando se ha completado una conversión. | ||

| Línea 88: | Línea 92: | ||

Si '''AIEN =1''' se habilitarán las interrupciones cada vez que la bandera COCO se establezca. | Si '''AIEN =1''' se habilitarán las interrupciones cada vez que la bandera COCO se establezca. | ||

| − | *BIT 5 –'''ADCO (Continuous Conversion Enable)''' | + | * BIT 5 –'''ADCO (Continuous Conversion Enable)''' |

Si '''ADCO =0''' se selecciona el modo de conversión simple (ver Modos de Conversión). | Si '''ADCO =0''' se selecciona el modo de conversión simple (ver Modos de Conversión). | ||

| Línea 94: | Línea 98: | ||

Si '''ADCO =1''' se selecciona el modo de conversión continuo (ver Modos de Conversión). | Si '''ADCO =1''' se selecciona el modo de conversión continuo (ver Modos de Conversión). | ||

| − | *BITS 4:0 –'''ADCH Input cannel select''' | + | * BITS 4:0 –'''ADCH Input cannel select''' |

| + | |||

En estos 5 bits mas bajos del registro ADCSC1 se coloca el valor en binario del canal en el que se quiere trabajar, si el modo de conversión continuo fue seleccionado, se pueden poner estos 5 bits en 1 al finalizar las conversiones para prevenir que otra sea ejecutada, si fue escogido el modo de conversión simple esto no es necesario. | En estos 5 bits mas bajos del registro ADCSC1 se coloca el valor en binario del canal en el que se quiere trabajar, si el modo de conversión continuo fue seleccionado, se pueden poner estos 5 bits en 1 al finalizar las conversiones para prevenir que otra sea ejecutada, si fue escogido el modo de conversión simple esto no es necesario. | ||

(ver Asignación de Canales) | (ver Asignación de Canales) | ||

| − | ====ADCSC2 Estatus y Control 2==== | + | ==== ADCSC2 Estatus y Control 2 ==== |

Este registro controla la función de comparar, el trigger a usar para la conversión y el indicador de conversión activa | Este registro controla la función de comparar, el trigger a usar para la conversión y el indicador de conversión activa | ||

| Línea 104: | Línea 109: | ||

[[Archivo:adcsc2.jpg|700px|center|thumb|Registro ADCSC2]] | [[Archivo:adcsc2.jpg|700px|center|thumb|Registro ADCSC2]] | ||

| − | *BIT 7 – '''ADACT (Conversion Active)''' | + | * BIT 7 – '''ADACT (Conversion Active)''' |

| + | |||

Este bit indica cuando una conversión se esta ejecutando, se establece cuando se inicia una conversión y se borra cuando la misma conversión se completa o se aborta. | Este bit indica cuando una conversión se esta ejecutando, se establece cuando se inicia una conversión y se borra cuando la misma conversión se completa o se aborta. | ||

| Línea 111: | Línea 117: | ||

Si ADACT =1 hay una conversión ejecutándose. | Si ADACT =1 hay una conversión ejecutándose. | ||

| − | *BIT 6 – '''ADTRG (Conversion Trigger Select)''' | + | * BIT 6 – '''ADTRG (Conversion Trigger Select)''' |

| + | |||

Este bit se usa para seleccionar qué tipo de trigger se va a usar para inciar una conversión. | Este bit se usa para seleccionar qué tipo de trigger se va a usar para inciar una conversión. | ||

| Línea 118: | Línea 125: | ||

Si ADTRG = 1 se selecciona hardware trigger, la conversión se hará cada vez que le llegue un flanco de subida a ADHWT (ver Hardware Trigger y Modos de Operacion). | Si ADTRG = 1 se selecciona hardware trigger, la conversión se hará cada vez que le llegue un flanco de subida a ADHWT (ver Hardware Trigger y Modos de Operacion). | ||

| − | *BIT 5 - '''ACFE (Compare Function Enable)''' | + | * BIT 5 - '''ACFE (Compare Function Enable)''' |

| + | |||

Habilita la función de comparar (ver ADCSC1_COCO). | Habilita la función de comparar (ver ADCSC1_COCO). | ||

| − | Si ACFE =0 se inhabilita la función comparar. | + | Si ACFE =0 se inhabilita la función comparar. |

Si ACFE =1 se habilita la función comparar. | Si ACFE =1 se habilita la función comparar. | ||

| − | *BIT 4 - '''ACFGT (Compare Function Greater Than Enable)''' | + | * BIT 4 - '''ACFGT (Compare Function Greater Than Enable)''' |

| + | |||

Cuando el resultado de la conversión es mayor o igual que el valor de comparación la función de comparación hace el trigger. | Cuando el resultado de la conversión es mayor o igual que el valor de comparación la función de comparación hace el trigger. | ||

| Línea 132: | Línea 141: | ||

Si ACFGT=1 se hace el trigger si la entrada es mayor o igual que el valor de comparación. | Si ACFGT=1 se hace el trigger si la entrada es mayor o igual que el valor de comparación. | ||

| − | *'''Los bits 3 y 2''' son solo de lectura y son siempre cero, '''los bits 1 y 2''' son de lectura y escritura pero están reservados y su valor '''siempre deberá ser cero''' | + | * '''Los bits 3 y 2''' son solo de lectura y son siempre cero, '''los bits 1 y 2''' son de lectura y escritura pero están reservados y su valor '''siempre deberá ser cero''' |

| − | ===Data Convertida=== | + | === Data Convertida === |

Al relizar cada conversión, el resultado se guarda en los registros ADCRH Y ADCRL. el módulo tiene un mecanismo de bloqueo que previene que la data de ADCRH y | Al relizar cada conversión, el resultado se guarda en los registros ADCRH Y ADCRL. el módulo tiene un mecanismo de bloqueo que previene que la data de ADCRH y | ||

ADCRL sea sobreescrita con una data nueva si la anterior se está leyendo mientras se esté en modo de 12 o 10 bits. Cuando se activa este bloqueo COCO no se | ADCRL sea sobreescrita con una data nueva si la anterior se está leyendo mientras se esté en modo de 12 o 10 bits. Cuando se activa este bloqueo COCO no se | ||

establece para la nueva data bloqueada y esta se pierde. En caso de estar usando el modo de conversión simple con la función de comparación habilitada | establece para la nueva data bloqueada y esta se pierde. En caso de estar usando el modo de conversión simple con la función de comparación habilitada | ||

| − | este bloqueo no tiene efecto alguno sobre las conversiones del ADC, para los demás casos cuando una nueva data es bloqueada y perdida se inicia otra conversión | + | este bloqueo no tiene efecto alguno sobre las conversiones del ADC, para los demás casos cuando una nueva data es bloqueada y perdida se inicia otra conversión |

| − | sin importar el modo de conversión en el que se esté trabajando. | + | sin importar el modo de conversión en el que se esté trabajando. |

Al trabajar con el modo de operación simple se debe tener cuidado con que los registros de data | Al trabajar con el modo de operación simple se debe tener cuidado con que los registros de data | ||

no se lean hasta que la conversión anterior se haya completado. | no se lean hasta que la conversión anterior se haya completado. | ||

| − | ====ADCRH Data Result High Register==== | + | ==== ADCRH Data Result High Register ==== |

En modo de operación de 12 bits, ADCRH guarda los 4 bits mas significativos de la conversión. | En modo de operación de 12 bits, ADCRH guarda los 4 bits mas significativos de la conversión. | ||

| + | |||

[[Archivo:adcrh.jpg|700px|center|thumb|Registro ADCRH]] | [[Archivo:adcrh.jpg|700px|center|thumb|Registro ADCRH]] | ||

| + | |||

Si se trabaja con el modo de operación de 8bit los bits 0, 1, 2 y 3 del registro ADCRH serán iguales a cero. Si se trabaja con el modo de 10bits, los bits 2 y 3 | Si se trabaja con el modo de operación de 8bit los bits 0, 1, 2 y 3 del registro ADCRH serán iguales a cero. Si se trabaja con el modo de 10bits, los bits 2 y 3 | ||

del ADCRH serán iguales a cero. En caso de cambiar el modo de operación, cualquier dato guardado en ADCRH será borrado | del ADCRH serán iguales a cero. En caso de cambiar el modo de operación, cualquier dato guardado en ADCRH será borrado | ||

| − | ====ADCRL Data Result Low Register==== | + | ==== ADCRL Data Result Low Register ==== |

En este registro se guardan los 8 bits mas bajos de la conversión. | En este registro se guardan los 8 bits mas bajos de la conversión. | ||

| + | |||

[[Archivo:adcrl.jpg|700px|center|thumb|Registro ADCRL]] | [[Archivo:adcrl.jpg|700px|center|thumb|Registro ADCRL]] | ||

| Línea 160: | Línea 172: | ||

En caso de cambiar el modo de operación, cualquier dato guardado en ADCRH será borrado. | En caso de cambiar el modo de operación, cualquier dato guardado en ADCRH será borrado. | ||

| − | ===Valor del Dato de Comparación=== | + | === Valor del Dato de Comparación === |

Estos registros guardan el valor del dato con el que se quiere comparar el resultado de la conversión que vaya a ejecutar. | Estos registros guardan el valor del dato con el que se quiere comparar el resultado de la conversión que vaya a ejecutar. | ||

| Línea 169: | Línea 181: | ||

ADCRL | ADCRL | ||

| − | ====ADCCVH Compare Value High Register==== | + | ==== ADCCVH Compare Value High Register ==== |

| + | |||

[[Archivo:adccvh.jpg|700px|center|thumb|Registro ADCCVH]] | [[Archivo:adccvh.jpg|700px|center|thumb|Registro ADCCVH]] | ||

ADCCVH guarda los bits 8, 9, 10 y 11 del valor de comparación, en caso de trabajar en modo de operación menor a 12 bits, el resto del registro se llenará con ceros | ADCCVH guarda los bits 8, 9, 10 y 11 del valor de comparación, en caso de trabajar en modo de operación menor a 12 bits, el resto del registro se llenará con ceros | ||

| − | ====ADCCVL Compare Value Low Register==== | + | ==== ADCCVL Compare Value Low Register ==== |

| + | |||

[[Archivo:adccvl.jpg|700px|center|thumb|Registro ADCCVL]] | [[Archivo:adccvl.jpg|700px|center|thumb|Registro ADCCVL]] | ||

ADCCVL guarda los 8 bits mas bajos del valor de comparación. | ADCCVL guarda los 8 bits mas bajos del valor de comparación. | ||

| − | ===ADCCFG Registro de Configuración=== | + | === ADCCFG Registro de Configuración === |

ADCCFG es usado para seleccionar el modo de operación, la fuente del clock y configurar el módulo para ahorro de energía o tiempo de muestreo largo | ADCCFG es usado para seleccionar el modo de operación, la fuente del clock y configurar el módulo para ahorro de energía o tiempo de muestreo largo | ||

| Línea 185: | Línea 199: | ||

[[Archivo:ADCCFG.jpg|700px|center|thumb|Registro ADCCFG]] | [[Archivo:ADCCFG.jpg|700px|center|thumb|Registro ADCCFG]] | ||

| − | *BIT 7 - '''ADLPC (Low Power Configuration)''' | + | * BIT 7 - '''ADLPC (Low Power Configuration)''' |

| + | |||

Cuando el módulo no se ha configurado para obtener tiempos de muestreo largos en las conversiones, este bit se usa para ahorrar energía | Cuando el módulo no se ha configurado para obtener tiempos de muestreo largos en las conversiones, este bit se usa para ahorrar energía | ||

| Línea 192: | Línea 207: | ||

Si '''ADLPC =1''' Se configura el módulo para ahorro de energía pero se usa la máxima velocidad del clock | Si '''ADLPC =1''' Se configura el módulo para ahorro de energía pero se usa la máxima velocidad del clock | ||

| − | *BITS 6:5 - '''ADIV (Clock Divide Select)''' | + | * BITS 6:5 - '''ADIV (Clock Divide Select)''' |

| + | |||

ADIV selecciona la relación de división usada por el ADC para generar el clock interno ADCK | ADIV selecciona la relación de división usada por el ADC para generar el clock interno ADCK | ||

| + | |||

[[Archivo:clkdivide.jpg|700px|center|thumb|Tabla de relaciones de división]] | [[Archivo:clkdivide.jpg|700px|center|thumb|Tabla de relaciones de división]] | ||

| − | *BIT 4 - '''ADLSMP (Long Sample Time configuration)''' | + | * BIT 4 - '''ADLSMP (Long Sample Time configuration)''' |

ADLSMP escoge entre Long Sample Time y Short Sample time, en long sample time el periodo de la muestra de la señal de entrada que se escoge es mayor y se obtienen | ADLSMP escoge entre Long Sample Time y Short Sample time, en long sample time el periodo de la muestra de la señal de entrada que se escoge es mayor y se obtienen | ||

| Línea 205: | Línea 222: | ||

Si '''ADLSMP =1''' se selecciona long sample time | Si '''ADLSMP =1''' se selecciona long sample time | ||

| − | *BITS 3:2 - '''MODE (Conversion Mode Selection)''' | + | * BITS 3:2 - '''MODE (Conversion Mode Selection)''' |

Estos bits se usan para seleccionar el modo de operación que tendrá la conversión puede ser de 12bits, 10bits u 8bits | Estos bits se usan para seleccionar el modo de operación que tendrá la conversión puede ser de 12bits, 10bits u 8bits | ||

| Línea 211: | Línea 228: | ||

[[Archivo:conversionmodes.jpg|700px|center|thumb|Modos De Operación]] | [[Archivo:conversionmodes.jpg|700px|center|thumb|Modos De Operación]] | ||

| − | *BITS 1:0 - '''ADICLK (Input Clock Select)''' | + | * BITS 1:0 - '''ADICLK (Input Clock Select)''' |

| + | |||

Estos bits se usan para seleccionar de entre las 4 posibles fuentes de clocks para generar el ADCK | Estos bits se usan para seleccionar de entre las 4 posibles fuentes de clocks para generar el ADCK | ||

[[Archivo:clkselect.jpg|700px|center|thumb|Input Clock Select]] | [[Archivo:clkselect.jpg|700px|center|thumb|Input Clock Select]] | ||

| − | + | === Control de Pines === | |

| − | ===Control de Pines=== | + | |

Estos 3 registros APCTL1, APCTL2 y APCTL3 se encargan de deshabilitar los puertos de entrada/salida del micro que estén siendo usados como entradas analógicas. | Estos 3 registros APCTL1, APCTL2 y APCTL3 se encargan de deshabilitar los puertos de entrada/salida del micro que estén siendo usados como entradas analógicas. | ||

| Línea 225: | Línea 242: | ||

'''APCTLY_ADPCX =1''' habilita el puerto X del registro APTCLY | '''APCTLY_ADPCX =1''' habilita el puerto X del registro APTCLY | ||

| − | *APCTL1 controla los pines asociados a los canales del 0 al 7 | + | * APCTL1 controla los pines asociados a los canales del 0 al 7 |

| − | *APCTL2 controla los pines asociados a los canales del 8 al 15 | + | * APCTL2 controla los pines asociados a los canales del 8 al 15 |

| − | *APCTL3 controla los pines asociados a los canales del 16 al 23 | + | * APCTL3 controla los pines asociados a los canales del 16 al 23 |

| − | ==Wait y Modo Stop3== | + | == Wait y Modo Stop3 == |

| − | ===Operación Wait=== | + | === Operación Wait === |

| − | La instrucción WAIT pone al micro en Low-power consumption standby mode, consumiendo poca energía y entrando en modo de espera del cual se recupera muy rápido | + | La instrucción WAIT pone al micro en Low-power consumption standby mode, consumiendo poca energía y entrando en modo de espera del cual se recupera muy rápido |

ya que los clocks fuentes se mantienen activos. Si se está ejecutando una conversión cuando el micro entra en modo WAIT la conversión de todas formas se completará. | ya que los clocks fuentes se mantienen activos. Si se está ejecutando una conversión cuando el micro entra en modo WAIT la conversión de todas formas se completará. | ||

Si se trabaja con el hardware trigger el micro podrá estar en wait mode y cuando llegue el flanco de subida a ADTWH se hará la conversión | Si se trabaja con el hardware trigger el micro podrá estar en wait mode y cuando llegue el flanco de subida a ADTWH se hará la conversión | ||

| Línea 239: | Línea 256: | ||

Cuando se establece COCO se genera una interrupción por haber completado la conversión (si AIEN=1) que despierta al módulo ADC del modo WAIT | Cuando se establece COCO se genera una interrupción por haber completado la conversión (si AIEN=1) que despierta al módulo ADC del modo WAIT | ||

| − | ===Modo Stop3=== | + | === Modo Stop3 === |

Esta instrucción se usa cuando la mayoría de las fuentes de clocks están deshabilitadas y se encarga de poner al micro en Low-power consumption standby mode | Esta instrucción se usa cuando la mayoría de las fuentes de clocks están deshabilitadas y se encarga de poner al micro en Low-power consumption standby mode | ||

| − | ====Modo Stop3 con ADACK deshabilitado==== | + | ==== Modo Stop3 con ADACK deshabilitado ==== |

| − | Si el clock asíncrono ADACK no fue seleccionado como el clock para la conversión, al ejecutar la instrucción Stop3 la conversión se abortará y el módulo entrara | + | Si el clock asíncrono ADACK no fue seleccionado como el clock para la conversión, al ejecutar la instrucción Stop3 la conversión se abortará y el módulo entrara |

en estado ocioso. Los contenidos de los registros ADCRH y ADCRL no se verán afectados por esta instrucción. Al salir del Stop3 mode, se necesitará de un hardware trigger | en estado ocioso. Los contenidos de los registros ADCRH y ADCRL no se verán afectados por esta instrucción. Al salir del Stop3 mode, se necesitará de un hardware trigger | ||

para continuar con las conversiones | para continuar con las conversiones | ||

| − | ====Modo Stop3 con ADACK habilitado==== | + | ==== Modo Stop3 con ADACK habilitado ==== |

| − | Si el clock asíncrono ADACK fue seleccionado como el clock para la conversión, al ejecutar la instruccion Stop3 la conversión se realizará. Las conversiones se | + | Si el clock asíncrono ADACK fue seleccionado como el clock para la conversión, al ejecutar la instruccion Stop3 la conversión se realizará. Las conversiones se |

| − | podrán iniciar estando en Stop3 mode por hardware trigger o si se trabaja en modo de conversión continua (ADCO =0). Cuando se establece COCO se genera una | + | podrán iniciar estando en Stop3 mode por hardware trigger o si se trabaja en modo de conversión continua (ADCO =0). Cuando se establece COCO se genera una |

interrupción por haber completado la conversión (si AIEN=1) que despierta al módulo ADC del modo Stop3 | interrupción por haber completado la conversión (si AIEN=1) que despierta al módulo ADC del modo Stop3 | ||

| − | ==Ejemplos== | + | == Ejemplos == |

| − | ===Ejemplo de uso del ADC en assembler=== | + | === Ejemplo de uso del ADC en assembler === |

<pre> | <pre> | ||

| Línea 265: | Línea 282: | ||

LIST ; ..storage and THIS is it's place | LIST ; ..storage and THIS is it's place | ||

| + | |||

; ------------------------------------------------------------------- | ; ------------------------------------------------------------------- | ||

| − | ;DEFINES | + | ; DEFINES |

ram: SET Z_RAMStart ; $80 | ram: SET Z_RAMStart ; $80 | ||

| Línea 277: | Línea 295: | ||

COP_Disable: EQU $42 | COP_Disable: EQU $42 | ||

| − | ;--------------------------------------------------------------------- | + | ; --------------------------------------------------------------------- |

; MAIN PROGRAM HEADER: | ; MAIN PROGRAM HEADER: | ||

| Línea 284: | Línea 302: | ||

ORG rom | ORG rom | ||

| − | Main: | + | Main: |

lda #COP_Disable ; Se deshabilita el WatchDog | lda #COP_Disable ; Se deshabilita el WatchDog | ||

| Línea 293: | Línea 311: | ||

txs ; ... | txs ; ... | ||

| − | + | ||

| − | ;------------------------------- | + | ; ------------------------------- |

; MCU_Init | ; MCU_Init | ||

| Línea 301: | Línea 319: | ||

clra ; Se deshabilitan los periféricos que no se usan para Bus clock | clra ; Se deshabilitan los periféricos que no se usan para Bus clock | ||

sta SCGC2 | sta SCGC2 | ||

| − | ;------------------------------- | + | |

| + | ; ------------------------------- | ||

; Init LEDs PORTs PTCD (bits 0-5) and PTED (bits 6-7) | ; Init LEDs PORTs PTCD (bits 0-5) and PTED (bits 6-7) | ||

| Línea 309: | Línea 328: | ||

mov #%11111111, PTED ; Los Leds de PTED tienen lógicas negada, se apagan | mov #%11111111, PTED ; Los Leds de PTED tienen lógicas negada, se apagan | ||

| − | mov #$FF, PTCDD ; Se seleccionan los PTCD como salida | + | mov #$FF, PTCDD ; Se seleccionan los PTCD como salida |

mov #$FF, PTEDD ; Se colocan los PTED como salidas | mov #$FF, PTEDD ; Se colocan los PTED como salidas | ||

| − | ;------------------------------------------------------------------ | + | ; ------------------------------------------------------------------ |

| − | ; ADC_configuration | + | ; ADC_configuration |

mov #$20, ADCSC1 ; Modo de conversion continuo seleccionado, Canal ADC0 seleccionado, | mov #$20, ADCSC1 ; Modo de conversion continuo seleccionado, Canal ADC0 seleccionado, | ||

clr ADCSC2 ; Software trigger selected | clr ADCSC2 ; Software trigger selected | ||

| − | mov #$30, ADCCFG ; Input clock/2. Long Sample time, modo de operacion 8-bit conversion | + | mov #$30, ADCCFG ; Input clock/2. Long Sample time, modo de operacion 8-bit conversion |

clr APCTL1 ; Se deshabilita el puerto asociado al canal 0 | clr APCTL1 ; Se deshabilita el puerto asociado al canal 0 | ||

bset APCTL1_ADPC0, APCTL1 ; Select channel for ADC input | bset APCTL1_ADPC0, APCTL1 ; Select channel for ADC input | ||

| Línea 325: | Línea 344: | ||

; ------------------------------------------------------------------ | ; ------------------------------------------------------------------ | ||

| + | |||

ADC_ISR: | ADC_ISR: | ||

| Línea 330: | Línea 350: | ||

sta ~PTCD ; Move ADC value to port C, los Leds se prenden con 0's | sta ~PTCD ; Move ADC value to port C, los Leds se prenden con 0's | ||

sta ~PTED ; ..and to port E | sta ~PTED ; ..and to port E | ||

| − | rti | + | rti |

| + | |||

| + | ; ------------------------------------------------------------- | ||

| − | |||

nop ; <<<NEEDED by CodeWarrior 10.1&2 (not 6.3).<<< | nop ; <<<NEEDED by CodeWarrior 10.1&2 (not 6.3).<<< | ||

| − | ;-------------------------------------------------------------------- | + | |

| + | ; -------------------------------------------------------------------- | ||

; Interrupt Vectors | ; Interrupt Vectors | ||

| Línea 346: | Línea 368: | ||

</pre> | </pre> | ||

| − | ===Ejemplo del uso del ADC en C=== | + | === Ejemplo del uso del ADC en C === |

| − | ====Ejemplo por encuesta==== | + | ==== Ejemplo por encuesta ==== |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| + | ; ''#'' include <hidef.h> /* for EnableInterrupts macro */ | ||

| + | ; ''#'' include "derivative.h" /* include peripheral declarations */ | ||

void main(void) { | void main(void) { | ||

| − | ;//Configuracion_ADC | + | ; //Configuracion_ADC |

| − | + | ||

| − | ADCSC1 = 0x60; // Canal ADCH0, modo conversión continua, interrupciones habilitadas | + | ADCSC1 = 0x60; // Canal ADCH0, modo conversión continua, interrupciones habilitadas |

ADCSC2 = 0x00; // Se deshabilita la función de comparación y se selecciona el software trigger | ADCSC2 = 0x00; // Se deshabilita la función de comparación y se selecciona el software trigger | ||

ADCCFG = 0x40; // Se selecciona Long Sample time y se divide el Bus Clock entre 2 | ADCCFG = 0x40; // Se selecciona Long Sample time y se divide el Bus Clock entre 2 | ||

| − | APCTL1 = 0x00; // Se deshabilita el puerto asociado al canal ADCH0 ya que esta siendo usado como entrada analogica | + | APCTL1 = 0x00; // Se deshabilita el puerto asociado al canal ADCH0 ya que esta siendo usado como entrada analogica |

| − | + | ||

| − | + | ||

EnableInterrupts; /* enable interrupts */ | EnableInterrupts; /* enable interrupts */ | ||

/* include your code here */ | /* include your code here */ | ||

| − | + | ; while(ADCSC1_COCO==0); // Esperar que la conversión se ejecute | |

| − | ;while(ADCSC1_COCO==0); // Esperar que la conversión se ejecute | + | |

| − | ;PTCD= ~(ADCRL); // Muestra el resultado NEGADO de la conversión en los leds de PTCD | + | ; PTCD= ~(ADCRL); // Muestra el resultado NEGADO de la conversión en los leds de PTCD |

for(;;) { | for(;;) { | ||

| Línea 385: | Línea 403: | ||

} | } | ||

| − | ====Ejemplo con vector de interrupción ==== | + | ==== Ejemplo con vector de interrupción ==== |

''#''include <hidef.h> /* for EnableInterrupts macro */ | ''#''include <hidef.h> /* for EnableInterrupts macro */ | ||

''#''include "derivative.h" /* include peripheral declarations */ | ''#''include "derivative.h" /* include peripheral declarations */ | ||

| − | + | ||

void MCU_Init(void) { | void MCU_Init(void) { | ||

| − | + | ||

| − | SOPT1 = 0x23; /* Watchdog disable. Stop Mode Enable. Background Pin enable. RESET pin enable */ | + | SOPT1 = 0x23; /* Watchdog disable. Stop Mode Enable. Background Pin enable. RESET pin enable */ |

SCGC1 = 0x10; /* Bus Clock to the ADC module is enable */ | SCGC1 = 0x10; /* Bus Clock to the ADC module is enable */ | ||

SCGC2 = 0x00; /* Disable Bus clock to unused peripherals */ | SCGC2 = 0x00; /* Disable Bus clock to unused peripherals */ | ||

| Línea 400: | Línea 418: | ||

void ADC_config(void) { | void ADC_config(void) { | ||

| − | ADCSC1 = 0x60; // Canal ADCH0, modo de conversión continua y se habilitan las interrupciones | + | ADCSC1 = 0x60; // Canal ADCH0, modo de conversión continua y se habilitan las interrupciones |

ADCSC2 = 0x00; // Se deshabilita la función de comparación y se selecciona el software trigger | ADCSC2 = 0x00; // Se deshabilita la función de comparación y se selecciona el software trigger | ||

ADCCFG = 0x40; // Se selecciona Long Sample time y se divide el Bus Clock entre 2 | ADCCFG = 0x40; // Se selecciona Long Sample time y se divide el Bus Clock entre 2 | ||

| Línea 411: | Línea 429: | ||

void main(void) { | void main(void) { | ||

| − | ;void MCU_Init(); | + | ; void MCU_Init(); |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| + | ; void ADC_config(); | ||

EnableInterrupts; /* enable interrupts */ | EnableInterrupts; /* enable interrupts */ | ||

| Línea 422: | Línea 437: | ||

/* include your code here */ | /* include your code here */ | ||

| − | |||

while(ADCSC1_COCO==0){ // Esperar que la conversión se ejecute | while(ADCSC1_COCO==0){ // Esperar que la conversión se ejecute | ||

| − | PTCD= ~(ADCRL); | + | PTCD= ~(ADCRL); |

bandera =0; // Muestra el resultado de la conversión en los leds de PTCD | bandera =0; // Muestra el resultado de la conversión en los leds de PTCD | ||

| Línea 448: | Línea 462: | ||

} | } | ||

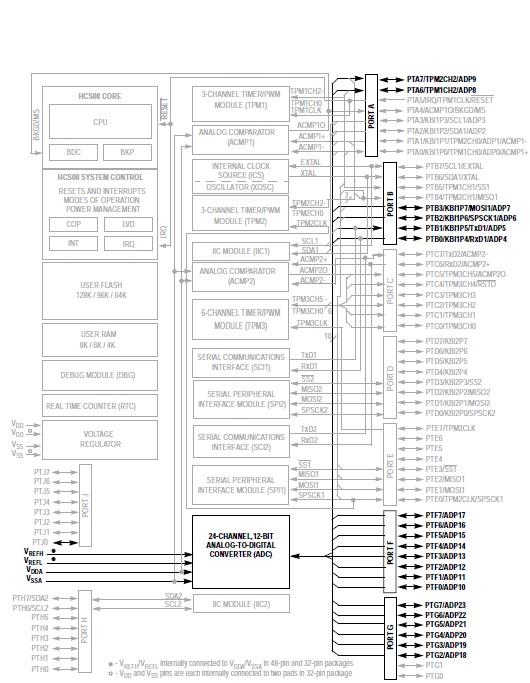

| − | ==Diagrama de Bloques Modulo ADC== | + | == Diagrama de Bloques Modulo ADC == |

[[Archivo:diagramabloques.jpg|700px|center|thumb|Diagrama De Bloques ADC]] | [[Archivo:diagramabloques.jpg|700px|center|thumb|Diagrama De Bloques ADC]] | ||

| Línea 454: | Línea 468: | ||

== Referencias == | == Referencias == | ||

| − | *[http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf '''Reference Manual.''' ''Freescale''] | + | * [http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf '''Reference Manual.''' ''Freescale''] |

[[Categoría: MC9S08QE128]] | [[Categoría: MC9S08QE128]] | ||

Revisión del 21:31 25 nov 2012

El módulo ADC del microcontrolador Freescale MC9S08QE128 toma como entrada analógica la señal que resulta al variar el potenciómetro y la convierte en un valor binario ajustable a 12, 10 y 8 bits

El conversor posee dos señales de referencia llamadas Voltage Reference High (V REFH) y Voltage Reference Low (V REFL) y podrá convertir muestras entre V SSAD (Tierra Analógica) y V DDAD (conectada a V REFH) que va entre 1.8 y 3.6 Volts

Contenido

Características

El módulo ADC posee:

- Algoritmo de aproximación lineal de 12 bits de resolución

- 32 canales que permiten hasta 28 entradas analógicas

- Formato de salida digital en 12, 10 u 8 bits

- Modo de conversión simple o continua

- Interrupción y bandera para conversiones completadas

- Tiempo de muestreo configurable para el dato de salida

- Reloj para la entrada seleccionable de entre 4 fuentes

- Modos wait y stop3 para operaciones con menos ruido

- Trigger de conversión por hardware seleccionable

- Comparador automático (mayor que, menor que, igual a) con interrupción para un valor programable

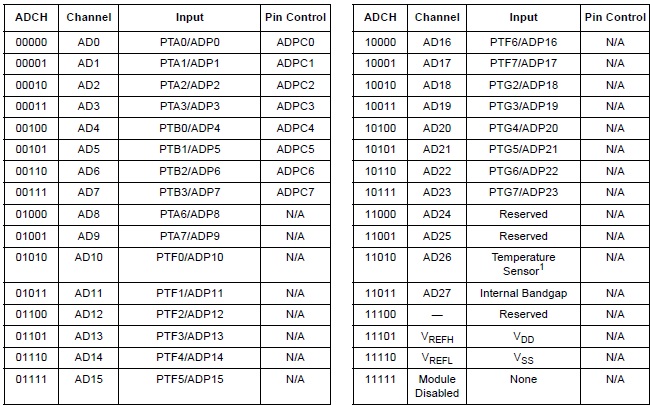

Asignación de canales

El ADC permite hacer las conversiones para cualquier canal entre AD0 y AD23. Si el registro que guarda el canal en el que se quiere trabajar ADCSC1_ADCH(4:0) es igual a 11111, entonces el subsistema que se encarga de convertir será apagado

Sensor de Temperatura

El ADC posee un sensor de temperatura cuya salida esta conectada al canal analógico AD26 y está definida por:

De donde Vtemp es el voltaje del AD26 a la temperatura del ambiente, Vtemp25 es el voltaje del AD26 a 25°C que por datasheet del micro se sabe que es 701.2 mV y m es la pendiente del voltaje vs temperatura que se sabe por datasheet que es 1.646mV desde -40°C hasta 25°C y 1.769 mV desde 25°C hasta 85°C.

Para usar el sensor de temperatura será necesario llenar los 5 bits menos significativos del registro ADCSC1 que corresponden al canal que se usará, con el número decimal 26 en binario (11010)

Hardware Trigger

El trigger que inicia una conversión en el ADC puede ser vía software activándolo en un instante de tiempo programable o también puede ser vía hardware. Para esto, el Real Time Counter (RTC) puede ser habilitado como el trigger para cada conversión que se vaya a hacer con el ADC.

Basta con configurar el ADCSC2_ADTRG = 1 y asi el ADC hará la conversión cada vez que haya un flanco de subida en el ADHWT que sucederá cuando el RTCINT coincida con RTCMOD

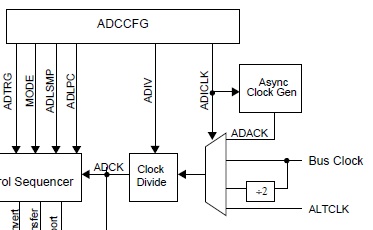

Selección del Clock

Una de las características del ADC es que tiene 4 relojes como fuente para escoger.

El primero es el bus clock, este se selecciona por defecto después de cada reset y trabajará a la misma frecuencia que esté trabajando el micro

La segunda opción es tomar como fuente el mismo bus clock pero el módulo del ADC nos permite dividirlo por 2, 4 y 8 para variar la velocidad de conversión

El tercero es el ALTCLK (alternate clock) que se establece como el ICSERCLK del micro y funciona como el external reference clock La última opción para escoger el clock con el que se quiere trabajar es el ADACK que es un reloj asíncrono que se genera por otro reloj fuente del ADC y se mantiene activo cuando el micro esta en modo stop3 o wait permitiendo conversiones en ambos modos para operaciones con menor ruido

Sin importar el reloj que se haya escogido como fuente, es necesario que la frecuencia con la que se vaya a trabajar esté dentro del rango de frecuencia para el ADCK. Dicho rango esta entre 0.4 Mhz y 8.0 Mhz para conversiones rápidas (High Speed Conversion, bit ADLPC =0) y entre 0.4 Mhz y 4.0 Mhz para conversiones que permiten ahorrar potencia (Low power conversión, bit ADLPC =1).

Modos de conversión

El módulo del ADC permite dos modos de conversión, estas son conversión continua y conversión simple. Estas se pueden configurar con el bit ADC0 del registro de estatus y control ADCSC1 (ver Registros de Control).

- Si fue seleccionado el Hardware trigger y se configura el ADC0 para conversión continua, cada vez que le llegue un flanco de subida a ADHWT el módulo hará la conversión. Si el ADC0 se configura para conversión simple el módulo hará una conversión cuando le llegue un flanco de subida a ADHWT y no iniciará otra si no que se mantendrá ocioso

- Si fue seleccionado Software trigger y se configura configura el ADC0 para conversión continua, cada vez que se escriba en el registro de control ADCSC1 el módulo hará la conversión. Si el ADC0 se configura para conversión simple el módulo hará una conversión cada vez que se escriba en el registro de control ADCSC1 y no iniciará otra si no que se mantendrá ocioso

Registros

Estatus y Control

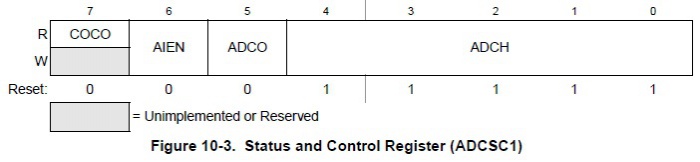

ADCSC1 Estatus y Control 1

Cada vez que se escriba en este registro, se abortará la conversión en curso y se iniciará otra nueva.

- BIT 7 – COCO (Conversion Complete Flag)

Cuando la función de comparar está inhabilitada (ACFE =0), se establecerá la bandera COCO=1 cada vez que que se complete una conversión, de lo contrario será igual a cero (COCO =0).

Cuando la función de comparar está habilitada (ACFE =1), se establecerá la bandera COCO =1 cada vez que se haya completado una conversión y el resultado de ésta sea TRUE, de lo contrario COCO =0.

El bit COCO se borra cada vez que se escriba en ADCSC1 o cada vez que se lea el registro ADCRL.

- BIT 6 – AIEN (Interrupt Enable)

Este bit habilita las interrupciones que se establecen cuando se ha completado una conversión.

Si AIEN =0 se inhabilitan las interrupciones al completar una conversión.

Si AIEN =1 se habilitarán las interrupciones cada vez que la bandera COCO se establezca.

- BIT 5 –ADCO (Continuous Conversion Enable)

Si ADCO =0 se selecciona el modo de conversión simple (ver Modos de Conversión).

Si ADCO =1 se selecciona el modo de conversión continuo (ver Modos de Conversión).

- BITS 4:0 –ADCH Input cannel select

En estos 5 bits mas bajos del registro ADCSC1 se coloca el valor en binario del canal en el que se quiere trabajar, si el modo de conversión continuo fue seleccionado, se pueden poner estos 5 bits en 1 al finalizar las conversiones para prevenir que otra sea ejecutada, si fue escogido el modo de conversión simple esto no es necesario. (ver Asignación de Canales)

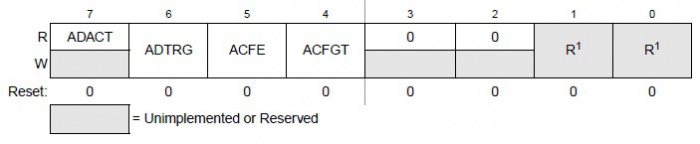

ADCSC2 Estatus y Control 2

Este registro controla la función de comparar, el trigger a usar para la conversión y el indicador de conversión activa

- BIT 7 – ADACT (Conversion Active)

Este bit indica cuando una conversión se esta ejecutando, se establece cuando se inicia una conversión y se borra cuando la misma conversión se completa o se aborta.

Si ADACT =0 no se esta ejecutando ninguna conversión.

Si ADACT =1 hay una conversión ejecutándose.

- BIT 6 – ADTRG (Conversion Trigger Select)

Este bit se usa para seleccionar qué tipo de trigger se va a usar para inciar una conversión.

Si ADTRG = 0 se selecciona software trigger, la conversión se hará cada vez que se escriba en el registro ADCSC1 (ver Modos de Operación).

Si ADTRG = 1 se selecciona hardware trigger, la conversión se hará cada vez que le llegue un flanco de subida a ADHWT (ver Hardware Trigger y Modos de Operacion).

- BIT 5 - ACFE (Compare Function Enable)

Habilita la función de comparar (ver ADCSC1_COCO).

Si ACFE =0 se inhabilita la función comparar.

Si ACFE =1 se habilita la función comparar.

- BIT 4 - ACFGT (Compare Function Greater Than Enable)

Cuando el resultado de la conversión es mayor o igual que el valor de comparación la función de comparación hace el trigger.

Si ACFGT=0 se hace el trigger si la entrada es menor que el valor de comparación.

Si ACFGT=1 se hace el trigger si la entrada es mayor o igual que el valor de comparación.

- Los bits 3 y 2 son solo de lectura y son siempre cero, los bits 1 y 2 son de lectura y escritura pero están reservados y su valor siempre deberá ser cero

Data Convertida

Al relizar cada conversión, el resultado se guarda en los registros ADCRH Y ADCRL. el módulo tiene un mecanismo de bloqueo que previene que la data de ADCRH y ADCRL sea sobreescrita con una data nueva si la anterior se está leyendo mientras se esté en modo de 12 o 10 bits. Cuando se activa este bloqueo COCO no se establece para la nueva data bloqueada y esta se pierde. En caso de estar usando el modo de conversión simple con la función de comparación habilitada este bloqueo no tiene efecto alguno sobre las conversiones del ADC, para los demás casos cuando una nueva data es bloqueada y perdida se inicia otra conversión sin importar el modo de conversión en el que se esté trabajando.

Al trabajar con el modo de operación simple se debe tener cuidado con que los registros de data no se lean hasta que la conversión anterior se haya completado.

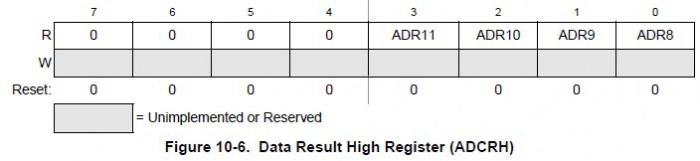

ADCRH Data Result High Register

En modo de operación de 12 bits, ADCRH guarda los 4 bits mas significativos de la conversión.

Si se trabaja con el modo de operación de 8bit los bits 0, 1, 2 y 3 del registro ADCRH serán iguales a cero. Si se trabaja con el modo de 10bits, los bits 2 y 3 del ADCRH serán iguales a cero. En caso de cambiar el modo de operación, cualquier dato guardado en ADCRH será borrado

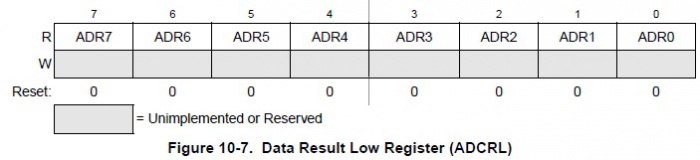

ADCRL Data Result Low Register

En este registro se guardan los 8 bits mas bajos de la conversión.

Cuando ADCRL es leído, COCO bit se borra. si ADCRL no es leído antes de que la siguiente conversión se haga entonces el dato se perderá. En caso de cambiar el modo de operación, cualquier dato guardado en ADCRH será borrado.

Valor del Dato de Comparación

Estos registros guardan el valor del dato con el que se quiere comparar el resultado de la conversión que vaya a ejecutar.

Si se trabaja en modo de operación de 12bits, se compararan los 4 bits mas altos almacenados en ADCCVH (3:0) directamente con los mismos bits del registro ADCRH. Si se trabaja con modo de operación 10 bits se compararan los 2 bits mas altos almacenados en ADCCVH (1:0) directamente con los mismos bits del registro ADCRH. Si se trabaja con modo de operación 8 bits se compararan los 8 bits mas bajos de la conversión almacenados en ADCCVL (7:0) directamente con los mismos bits del registro ADCRL

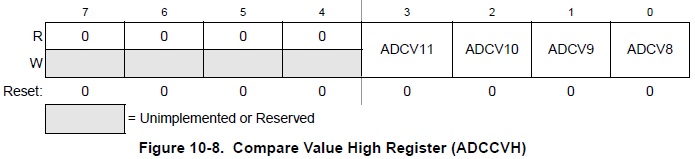

ADCCVH Compare Value High Register

ADCCVH guarda los bits 8, 9, 10 y 11 del valor de comparación, en caso de trabajar en modo de operación menor a 12 bits, el resto del registro se llenará con ceros

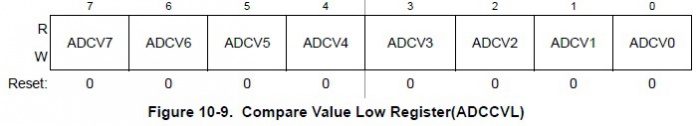

ADCCVL Compare Value Low Register

ADCCVL guarda los 8 bits mas bajos del valor de comparación.

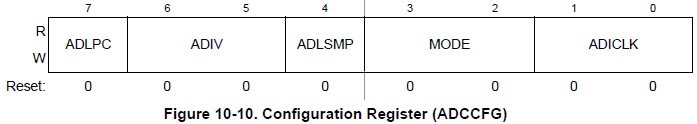

ADCCFG Registro de Configuración

ADCCFG es usado para seleccionar el modo de operación, la fuente del clock y configurar el módulo para ahorro de energía o tiempo de muestreo largo

- BIT 7 - ADLPC (Low Power Configuration)

Cuando el módulo no se ha configurado para obtener tiempos de muestreo largos en las conversiones, este bit se usa para ahorrar energía

Si ADLPC =0 se configura el módulo para alta velocidad

Si ADLPC =1 Se configura el módulo para ahorro de energía pero se usa la máxima velocidad del clock

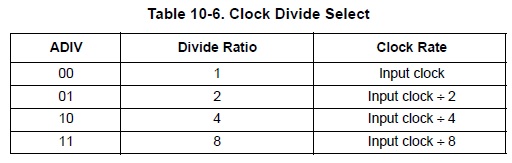

- BITS 6:5 - ADIV (Clock Divide Select)

ADIV selecciona la relación de división usada por el ADC para generar el clock interno ADCK

- BIT 4 - ADLSMP (Long Sample Time configuration)

ADLSMP escoge entre Long Sample Time y Short Sample time, en long sample time el periodo de la muestra de la señal de entrada que se escoge es mayor y se obtienen medidas o resultados mas precisos, en short sample time sucede lo contrario pero la conversión se hace más rápido

Si ADLSMP =0 se escoge short sample time

Si ADLSMP =1 se selecciona long sample time

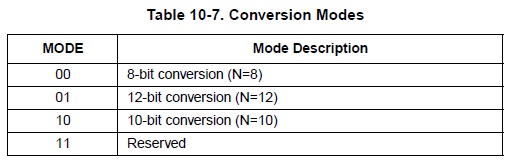

- BITS 3:2 - MODE (Conversion Mode Selection)

Estos bits se usan para seleccionar el modo de operación que tendrá la conversión puede ser de 12bits, 10bits u 8bits

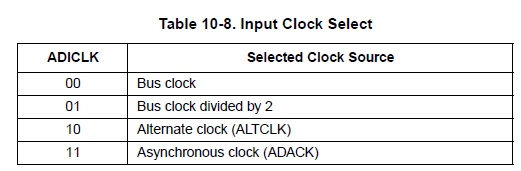

- BITS 1:0 - ADICLK (Input Clock Select)

Estos bits se usan para seleccionar de entre las 4 posibles fuentes de clocks para generar el ADCK

Control de Pines

Estos 3 registros APCTL1, APCTL2 y APCTL3 se encargan de deshabilitar los puertos de entrada/salida del micro que estén siendo usados como entradas analógicas.

APCTLY_ADPCX =0 deshabilita el puerto X del registro APTCLY

APCTLY_ADPCX =1 habilita el puerto X del registro APTCLY

- APCTL1 controla los pines asociados a los canales del 0 al 7

- APCTL2 controla los pines asociados a los canales del 8 al 15

- APCTL3 controla los pines asociados a los canales del 16 al 23

Wait y Modo Stop3

Operación Wait

La instrucción WAIT pone al micro en Low-power consumption standby mode, consumiendo poca energía y entrando en modo de espera del cual se recupera muy rápido ya que los clocks fuentes se mantienen activos. Si se está ejecutando una conversión cuando el micro entra en modo WAIT la conversión de todas formas se completará. Si se trabaja con el hardware trigger el micro podrá estar en wait mode y cuando llegue el flanco de subida a ADTWH se hará la conversión

Cuando se establece COCO se genera una interrupción por haber completado la conversión (si AIEN=1) que despierta al módulo ADC del modo WAIT

Modo Stop3

Esta instrucción se usa cuando la mayoría de las fuentes de clocks están deshabilitadas y se encarga de poner al micro en Low-power consumption standby mode

Modo Stop3 con ADACK deshabilitado

Si el clock asíncrono ADACK no fue seleccionado como el clock para la conversión, al ejecutar la instrucción Stop3 la conversión se abortará y el módulo entrara en estado ocioso. Los contenidos de los registros ADCRH y ADCRL no se verán afectados por esta instrucción. Al salir del Stop3 mode, se necesitará de un hardware trigger para continuar con las conversiones

Modo Stop3 con ADACK habilitado

Si el clock asíncrono ADACK fue seleccionado como el clock para la conversión, al ejecutar la instruccion Stop3 la conversión se realizará. Las conversiones se podrán iniciar estando en Stop3 mode por hardware trigger o si se trabaja en modo de conversión continua (ADCO =0). Cuando se establece COCO se genera una interrupción por haber completado la conversión (si AIEN=1) que despierta al módulo ADC del modo Stop3

Ejemplos

Ejemplo de uso del ADC en assembler

NOLIST INCLUDE 'derivative.inc' LIST ; ..storage and THIS is it's place ; ------------------------------------------------------------------- ; DEFINES ram: SET Z_RAMStart ; $80 rom: SET ROMStart ; $2080 initStack: EQU RAMEnd + 1 ; $1800=$17FF+1. SP = $17FF COP_Disable: EQU $42 ; --------------------------------------------------------------------- ; MAIN PROGRAM HEADER: ABSENTRY Main ORG rom Main: lda #COP_Disable ; Se deshabilita el WatchDog sta SOPT1 ; ..System Options 1 ldhx #initStack ; Set up SP txs ; ... ; ------------------------------- ; MCU_Init lda #$10 ; Habilita el Bus Clock para el módulo ADC sta SCGC1 clra ; Se deshabilitan los periféricos que no se usan para Bus clock sta SCGC2 ; ------------------------------- ; Init LEDs PORTs PTCD (bits 0-5) and PTED (bits 6-7) mov #%11110000, PTCD ; Se prenden 4 LEDs para verificar mov #%11111111, PTED ; Los Leds de PTED tienen lógicas negada, se apagan mov #$FF, PTCDD ; Se seleccionan los PTCD como salida mov #$FF, PTEDD ; Se colocan los PTED como salidas ; ------------------------------------------------------------------ ; ADC_configuration mov #$20, ADCSC1 ; Modo de conversion continuo seleccionado, Canal ADC0 seleccionado, clr ADCSC2 ; Software trigger selected mov #$30, ADCCFG ; Input clock/2. Long Sample time, modo de operacion 8-bit conversion clr APCTL1 ; Se deshabilita el puerto asociado al canal 0 bset APCTL1_ADPC0, APCTL1 ; Select channel for ADC input bset ADCSC1_AIEN, ADCSC1 ; Se habilitan las interrupciones del AIEN bra * ; ------------------------------------------------------------------ ADC_ISR: lda ADCRL ;Se lee la data de ADCRL, COCO se borra! sta ~PTCD ; Move ADC value to port C, los Leds se prenden con 0's sta ~PTED ; ..and to port E rti ; ------------------------------------------------------------- nop ; <<<NEEDED by CodeWarrior 10.1&2 (not 6.3).<<< ; -------------------------------------------------------------------- ; Interrupt Vectors ORG Vadc DC.W ADC_ISR ORG Vreset DC.W Main ; RESET END

Ejemplo del uso del ADC en C

Ejemplo por encuesta

- # include <hidef.h> /* for EnableInterrupts macro */

- # include "derivative.h" /* include peripheral declarations */

void main(void) {

- //Configuracion_ADC

ADCSC1 = 0x60; // Canal ADCH0, modo conversión continua, interrupciones habilitadas ADCSC2 = 0x00; // Se deshabilita la función de comparación y se selecciona el software trigger ADCCFG = 0x40; // Se selecciona Long Sample time y se divide el Bus Clock entre 2 APCTL1 = 0x00; // Se deshabilita el puerto asociado al canal ADCH0 ya que esta siendo usado como entrada analogica

EnableInterrupts; /* enable interrupts */

/* include your code here */

- while(ADCSC1_COCO==0); // Esperar que la conversión se ejecute

- PTCD= ~(ADCRL); // Muestra el resultado NEGADO de la conversión en los leds de PTCD

for(;;) {

__RESET_WATCHDOG(); /* feeds the dog */

/* loop forever */

} /* please make sure that you never leave main */

}

Ejemplo con vector de interrupción

#include <hidef.h> /* for EnableInterrupts macro */

#include "derivative.h" /* include peripheral declarations */

void MCU_Init(void) {

SOPT1 = 0x23; /* Watchdog disable. Stop Mode Enable. Background Pin enable. RESET pin enable */ SCGC1 = 0x10; /* Bus Clock to the ADC module is enable */ SCGC2 = 0x00; /* Disable Bus clock to unused peripherals */

}

void ADC_config(void) {

ADCSC1 = 0x60; // Canal ADCH0, modo de conversión continua y se habilitan las interrupciones ADCSC2 = 0x00; // Se deshabilita la función de comparación y se selecciona el software trigger ADCCFG = 0x40; // Se selecciona Long Sample time y se divide el Bus Clock entre 2 APCTL1 = 0x00; // Se deshabilita el puerto asociado al canal ADCH0 ya que esta siendo usado como entrada analógica

}

byte bandera;

void main(void) {

- void MCU_Init();

- void ADC_config();

EnableInterrupts; /* enable interrupts */

/* include your code here */

while(ADCSC1_COCO==0){ // Esperar que la conversión se ejecute

PTCD= ~(ADCRL);

bandera =0; // Muestra el resultado de la conversión en los leds de PTCD

}

for(;;) {

__RESET_WATCHDOG(); /* feeds the dog */

/* loop forever */

} /* please make sure that you never leave main */

}

void interrupt VectorNumber_Vadc ADC() {

while(ADCSC1_COCO==0); // Esperar que la conversión se ejecute

bandera =1; }

Diagrama de Bloques Modulo ADC

Referencias

Contributors

AK, Anairam, Artdamato, Dalak, Fdepasquale, Hyma, Jesus Grimón, Julioa44, LitzaPinto, Luis E Santana P, Minleung, Misato, Ncertad, Racuna