Diferencia entre revisiones de «Camino de Datos para instrucciones de formato J»

| (No se muestran 7 ediciones intermedias de 4 usuarios) | |||

| Línea 1: | Línea 1: | ||

<p align="justify"> | <p align="justify"> | ||

| − | Las instrucciones de '''salto incondicional''' (J-Instructions) como su nombre lo indica, se trata de instrucciones de saltos entre secciones del código mediante el uso de etiquetas, generalmente se utilizan para realizar tareas especificas dentro del programa ( simulando funciones como en otros lenguajes de programación). | + | Las instrucciones de [[Instrucciones aritméticas, lógicas y de salto incondicional en el Mips#Salto Incondicional|'''salto incondicional''']] (J-Instructions) como su nombre lo indica, se trata de instrucciones de saltos entre secciones del código mediante el uso de etiquetas, generalmente se utilizan para realizar tareas especificas dentro del programa (simulando funciones como en otros lenguajes de programación). |

| − | + | ||

| − | En el lenguaje Assembly de MIPS se pueden observar dos instrucciones de formato J: | + | En el lenguaje Assembly de [[MIPS]] se pueden observar dos instrucciones de formato J: |

* '''j''' ''X'' : Realiza un salto incondicional a la dirección o etiqueta ''X''. | * '''j''' ''X'' : Realiza un salto incondicional a la dirección o etiqueta ''X''. | ||

| Línea 12: | Línea 12: | ||

'''En la arquitectura MIPS de un solo ciclo estas instrucciones son ejecutadas como se muestra a continuación:''' | '''En la arquitectura MIPS de un solo ciclo estas instrucciones son ejecutadas como se muestra a continuación:''' | ||

| − | <p align="justify"> Al ser recibida la señal de salto incondicional en el módulo NEXTPC (J=1) automaticamente se selecciona la segunda entrada del demultiplexor 2a1 que posee | + | <p align="justify"> Al ser recibida la señal de salto incondicional en el módulo NEXTPC (J=1) automaticamente se selecciona la segunda entrada del demultiplexor 2a1 que posee la concatenación de los cuatro (4) bits más significativos del PC actual y los ventiseis (26) bits de la dirección inmediata del destino de la función, este dato de treinta (30) bits es conocido como el '''Jump Target Address''' que posteriormente será utilizado como PC. Adicionalmente se coloca en "uno" (1) al registro PCSrc. |

| − | + | ||

| − | + | ||

</p> | </p> | ||

| − | |||

[[Image:NextPc(structure).png|thumb|center|400px|Módulo Next PC|Estructura interna del bloque NEXT PC]] | [[Image:NextPc(structure).png|thumb|center|400px|Módulo Next PC|Estructura interna del bloque NEXT PC]] | ||

| − | |||

Al estar el registro PCSrc en activo (PCSrc =1) se utiliza la segunda entrada del multiplexor 2a1 que hace pasar el '''Jump Target Address''' al registrp PC, de otra manera el proximo PC será PC+4. | Al estar el registro PCSrc en activo (PCSrc =1) se utiliza la segunda entrada del multiplexor 2a1 que hace pasar el '''Jump Target Address''' al registrp PC, de otra manera el proximo PC será PC+4. | ||

| − | [[Image:J-Instruction(structure).png|thumb|center|600px| | + | |

| + | [[Image:J-Instruction(structure).png|thumb|center|600px|Camino De Datos De La Instrucción J]] | ||

'''En la instruccion J:''' | '''En la instruccion J:''' | ||

| − | - No se escribe ni lee en ninguna dirección de memoria | + | - No se escribe ni lee en ninguna dirección de memoria. |

- No se modifican registros. | - No se modifican registros. | ||

| − | - Es indiferente el valor de los registros RegDst, ExtOp, ALUSrc, ALUCtrl, and MemtoReg | + | - Es indiferente el valor de los registros RegDst, ExtOp, ALUSrc, ALUCtrl, and MemtoReg. |

| + | |||

| + | |||

| + | == Referencias Bibliográficas == | ||

| + | |||

| + | * http://faculty.kfupm.edu.sa/COE/mudawar/coe308/lectures/08-SingleCycleProcessor.pdf | ||

| + | |||

| + | |||

| + | [[Category:EC3731 - Arquitectura del Computador 2]] | ||

| + | [[Category:MIPS]] | ||

Revisión actual del 14:06 8 nov 2013

Las instrucciones de salto incondicional (J-Instructions) como su nombre lo indica, se trata de instrucciones de saltos entre secciones del código mediante el uso de etiquetas, generalmente se utilizan para realizar tareas especificas dentro del programa (simulando funciones como en otros lenguajes de programación). En el lenguaje Assembly de MIPS se pueden observar dos instrucciones de formato J:

- j X : Realiza un salto incondicional a la dirección o etiqueta X.

- jal X : Guarda la dirección de PC en un registro y realiza un salto a la dirección o etiqueta X.

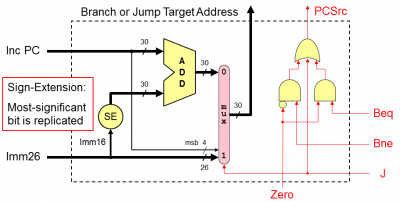

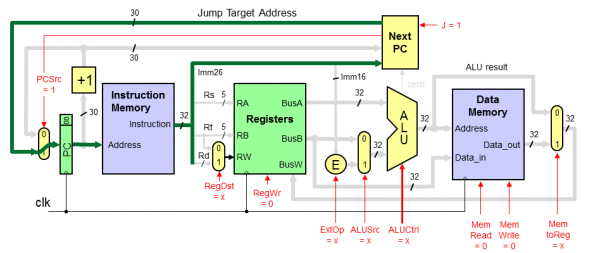

En la arquitectura MIPS de un solo ciclo estas instrucciones son ejecutadas como se muestra a continuación:

Al ser recibida la señal de salto incondicional en el módulo NEXTPC (J=1) automaticamente se selecciona la segunda entrada del demultiplexor 2a1 que posee la concatenación de los cuatro (4) bits más significativos del PC actual y los ventiseis (26) bits de la dirección inmediata del destino de la función, este dato de treinta (30) bits es conocido como el Jump Target Address que posteriormente será utilizado como PC. Adicionalmente se coloca en "uno" (1) al registro PCSrc.

Al estar el registro PCSrc en activo (PCSrc =1) se utiliza la segunda entrada del multiplexor 2a1 que hace pasar el Jump Target Address al registrp PC, de otra manera el proximo PC será PC+4.

En la instruccion J:

- No se escribe ni lee en ninguna dirección de memoria. - No se modifican registros. - Es indiferente el valor de los registros RegDst, ExtOp, ALUSrc, ALUCtrl, and MemtoReg.