Diferencia entre revisiones de «PWM (Modulación de Ancho de Pulso)»

(→Registros del modulo del contador del TPM (TPMxMODH:TPMxMODL)) |

|||

| (No se muestran 49 ediciones intermedias de 11 usuarios) | |||

| Línea 1: | Línea 1: | ||

| − | |||

| − | |||

[[Categoría: EC3883 - Laboratorio de Proyectos 3]] | [[Categoría: EC3883 - Laboratorio de Proyectos 3]] | ||

[[Categoría: MC9S08QE128]] | [[Categoría: MC9S08QE128]] | ||

| − | = | + | <div style="top:+0.3em; text-align: center;font-size:100%; border:1px solid #C7D0F8; background:#F2F5FD;width:80%"> |

| − | + | '''Este artículo está incompleto. Necesita trabajo adicional. Revisar la discusión.'''</div> | |

| − | + | ==Introducción== | |

| − | + | ||

| − | |||

| − | '''SOPT2=0x05''' | + | |

| + | |||

| + | ===Configuración=== | ||

| + | |||

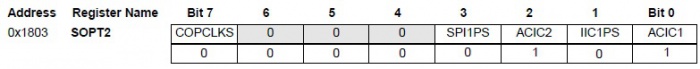

| + | El comparador analógico (ACMP) puede ser configurado para conectarse el a un canal TPM de entrada, colocando el bit SOPT2 [ACICx] en uno. Haciendo esto, el pin del canal 0 del TPM no está disponible de forma externa, es decir no puede ser modificado. La salida del ACMP 1 puede conectarse a TPM1CH0 y la salida del ACMP2 puede conectarse a TPM2CH0. | ||

| + | [[Archivo:Untitled.jpg|700px|center|thumb|'''Configuración del módulo SOPT2 para conectar el ACMP a los canales del TPM'''.]] | ||

| + | |||

| + | |||

| + | |||

| + | Al momento de programar, el código para la configuración anterior sería de esta forma: | ||

| + | |||

| + | '''SOPT2=0x05''' | ||

| + | |||

| + | |||

| + | Donde el valor hexadecimal 0x05 representa los 8 bits del registro SOPT2 que, como se observa en el cuadro anterior, son 00000101. | ||

| + | |||

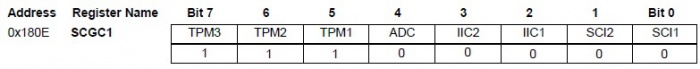

===Compuerta de clocks=== | ===Compuerta de clocks=== | ||

| − | Los clocks de los | + | Los clocks de los módulos TPM1, TPM2 y TPM3 pueden activarse o desactivarse usando el módulo SCGC1 [TPMx]. Cuando los bits están en 1, los puertos se habilitan dejando usar los clocks de cada módulo, y en cero se inhabilitan. Luego de un reset estos bits se colocan en 1. |

| − | [[Archivo:Untitled2.jpg|700px|center|thumb|''' | + | [[Archivo:Untitled2.jpg|700px|center|thumb|'''Habilitación de los clocks del TPM1 TPM2 y TPM3''']] |

| − | Similar al caso anterior, el | + | Similar al caso anterior, el código para la configuración anteriormente descrita es: |

| + | |||

| + | '''SCGC1=0xE0''' | ||

| + | |||

| + | Nuevamente el valor hexadecimal 0xE0 representa los 8 bits del registro SCGC1, los cuales eran 11100000 | ||

| + | |||

| + | |||

| + | Ademas del reloj interno el modulo permite seleccionar entre dehabilitar el temporizador, un reloj de oscilador de cristal o un reloj externo para ser el reloj que controla el pre-escalador y subsecuentemente el contador TPM de 16-bits. | ||

| + | |||

| + | |||

| + | |||

| + | |||

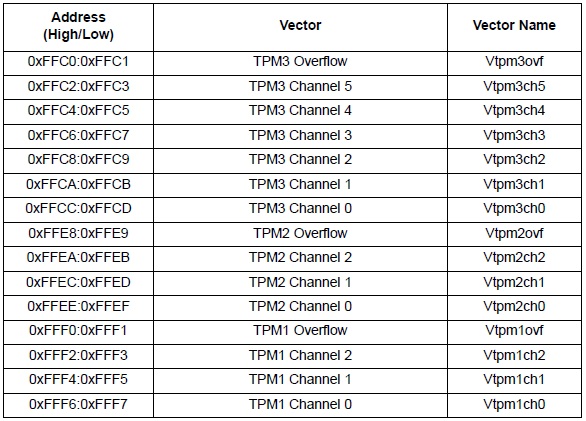

| + | ===Vector de [[interrupciones]]=== | ||

| + | |||

| + | A continuación se presentan los vectores de interrupciones para este módulo: | ||

| + | |||

| + | [[Archivo:Untitled3.jpg|700px|center|thumb|'''Vectores de interrupción del TPM''']] | ||

| + | |||

| + | ===Características=== | ||

| + | |||

| + | El módulo PWM posee las siguientes características: | ||

| + | |||

| + | *Cada canal se puede configurarse para ser capturador de entrada, comparador de salidas, o alineación de flancos PWM. Estos tipos de configuración se discutirán en la sección de modos de operación. | ||

| + | |||

| + | *Escoger la polaridad en las salidas del PWM (positiva o negativa) | ||

| + | |||

| + | *El módulo puede ser configurado como buffer o como alineación central de la modulación del ancho de pulso (CPMW por sus siglas en inglés). | ||

| + | |||

| + | *El timer puede ser modificado para usarse con una escala predeterminada del bus clock, un clock fijo o un clock externo: | ||

| + | |||

| + | #La preescala se define dividiendo el clock del bus entre 1, 2, 4, 8, 16, 32, 64 o 128. El bus clock al que opera el microcontrolador es de 1MHz. | ||

| + | #El clock fijo es sincronizado con el bus clock mediante un circuito sincronizador. | ||

| + | #Para el clock externo, el pin puede compartirse con un pin de un canal o de cualquier otra entrada, por lo tanto hay que tener cuidado al configurar este pin. | ||

| + | |||

| + | *Un interruptor por canal y un contador para las interrupciones. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ===Modos de operación=== | ||

| + | |||

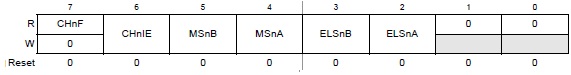

| + | Los canales pueden ser configurados independientemente como capturadores de entrada, comparador de salidas, o alineación de los flancos de PWM. Un bit de control puede modificarse para que todos los canales del módulo sean configurados como alineación de la modulación del ancho de pulso, si este es el caso se inhabilitan las otras opciones de configuración. | ||

| + | Cuando el Microcontrolador esta en BDM background o BDM foreground, el TPM suspende las operaciones y las reanuda apenas el microcontrolador regresa a estado normal. Cuando esta en stop, todos los clocks del Microcontrolador se paran, incluyendo el oscilador principal, por lo tanto el modulo TPM es inhabilitado momentáneamente. En el modo de espera (wait mode), el TPM opera de forma normal ya que no genera una referencia a tiempo real ni el interrupt necesario para despertar el micro de este estado. Los modos de operación son los siguientes: | ||

| + | |||

| + | *'''Modo de captura de entrada:''' Cuando un evento preseleccionado de flanco ocurre en el pin asociado al canal que se esta usando, el valor actual del contador del timer de 16 bits es guardado en el registro de valor del canal y una bandera de interrupción se coloca en uno. Un flanco de subida, flanco de bajada, cualquier flanco o ningún flanco (canal inhabilitado) puede ser seleccionado como el flanco activo que dispara la captura de entrada. | ||

| + | |||

| + | *'''Modo de comparación de salida:''' Cuando el valor en el registro del contador es igual al valor del registro del canal, una bandera de un bit de interrupción se coloca en uno, y una acción de salida seleccionada es forzada en el pin del Microcontrolador. La salida que se ve en el pin puede ser forzada a cero, a uno, intercambiar/conmutar las salidas o simplemente ignorarlo. | ||

| + | |||

| + | *'''Modo de alineación de flancos de PWM:''' El valor del registro de 16 bits +1 define el período de la señal de salida del PWM. El valor del registro del canal define el duty cicle (tiempo en que la señal permanece en un estado activo) de la señal de salida del PWM. También se puede definir la polaridad de la señal de salida. Las interrupciones ocurren apenas termine el período de la señal, es decir en el punto de transición del duty cicle (cuando la señal pasa de activa a inactiva) | ||

| + | |||

| + | *'''Modo de alineacion central del PWM:''' El doble del valor del registro del modulo de 16 bits define el period de las salidas PWM, y los registros de valores de los canales definen la mitad de la duración del duty cycle. El contador del timer cuenta hasta que llega al valor del registro del modulo y luego cuenta desde este valor hasta cero. Mientras el contador esta contando hacia abajo, y el valor del contador es el mismo que el del modulo, la salida PWM se activa. En el caso contrario, es decir cuando esta contando hacia arriba y los valores coinciden, la salida PWM se desactiva. | ||

| + | |||

| + | |||

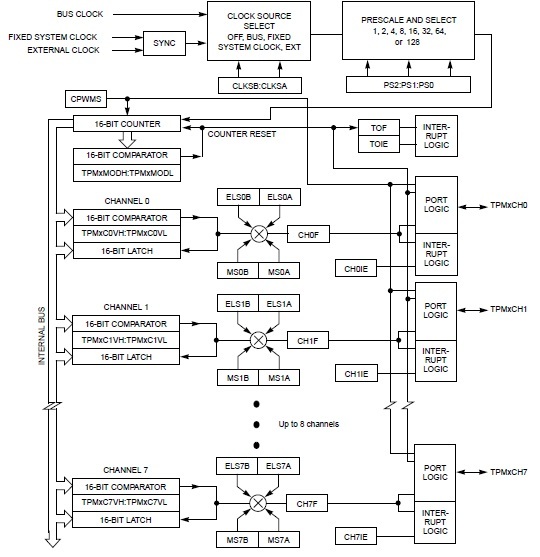

| + | ===Diagrama de bloques=== | ||

| + | |||

| + | El módulo TPM usa un pin de entrada/salida por canal (TPMxCHn), donde n representa el numero del canal. Hay que tener cuidado a usar estos pines ya que los pines de entrada/salida del TPM están asociados a los puertos de entrada/salida generales del microcontrolador. El componente central es el contador de 16 bits, el cual provee el tiempo de referencia para los modos de operación. Los registros del modulo del contador (TPMxMODH:TPMxMODL) registra el valor del modulo. Este dato se puede leer cuando sea, mas si se modifica este dato en la parte baja (TPMxMODL) o en la parte alta (TPMxMODH), se resetea el contador. | ||

| + | |||

| + | [[Archivo:Untitled4.jpg|700px|center|thumb|'''Diagrama de bloques del TPM'''.]] | ||

| + | |||

| + | |||

| + | ==Registros del TPM== | ||

| + | |||

| + | |||

| + | ===Registros de status y control del TPM (TPMxSC)=== | ||

| + | |||

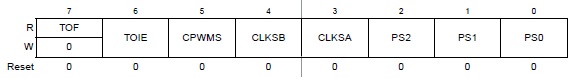

| + | El registro TPMxSC contiene la bandera de overflow y los bits de control para determinar la habilitación de las interrupciones, el modo de operación que se va a usar, el tipo de clock y la escala en caso de ser necesaria. | ||

| + | [[Archivo:Untitled5.jpg|700px|center|thumb|'''Bits del registro TPMxSC'''.]] | ||

| + | |||

| + | *'''TOF (Bit 7):''' Este bit se conoce como la bandera de overflow del timer. Este bit se coloca en uno cuando el contador del TPM se resetea (0x0000) luego de haber alcanzado el valor guardado en el registro de modulo del contador. Para borrar este bit (ponerlo en cero), es necesario leer el registro TPMxSC cuando la bandera este en uno y escribir en este bit un cero. Si llegase a ocurrir otro overflow antes de colocar el bit 7 en cero, la secuencia se resetea por lo tanto la bandera quedaría en uno para que una interrupción del tipo TOF no se pierda debido a una anterior. | ||

| + | |||

| + | *'''TOIE (Bit 6):''' Tambien llamado habilitador de interrupciones de overflow del timer. Si este bit esta en uno se habilita la interrupción debido a overflows. Es decir que aunque el bit de la bandera de overflow este en uno, si este bit esta en cero nunca van a ocurrir interrupciones del tipo TOF. | ||

| + | |||

| + | *'''CPWMS (Bit 5):''' Si este bit esta en uno, se activa el modo de operación de alineación central de PWM para todos los canales, desactivando las demás opciones. Además configura el TPM para que el contador opere tanto hacia arriba como hacia abajo (up/down counting) en vez de solo hacia arriba. Un reset coloca este bit en cero habilitando los demás modos de operación. | ||

| + | |||

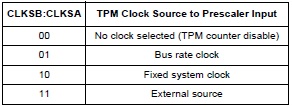

| + | *'''CLKS[B:A] (Bit 4:3):''' Estos dos bits se usan para definir que tipo de clock se va a utilizar. El clock fijo solo sirve cuando el clock del sistema esta basado en un sistema PLL (divisor del clock). En caso de no ser así el clock va a ser el mismo que el bus clock, 1MHz para este caso. La sincronización de un clock externo se genera mediante el modulo del bus clock del TPM, mientras que para el caso de un clock fijo es a través de un circuito sincronizador. | ||

| + | [[Archivo:Untitled6.jpg|700px|center|thumb|'''Tipos de clock (Bit 4:3)'''.]] | ||

| + | |||

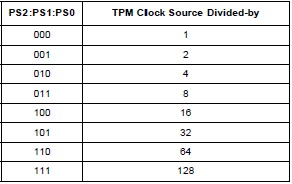

| + | *'''PS[2:0] (Bit 2:0):''' Estos 3 bits se usan para modificar el clock del TPM escogiendo uno de los factores de división que se observan en la siguiente tabla. | ||

| + | [[Archivo:Untitled7.jpg|700px|center|thumb|'''Factor de escalamiento (Bits 2:0)'''.]] | ||

| + | |||

| + | |||

| + | |||

| + | |||

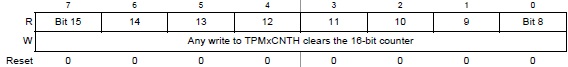

| + | ===Registro de contadores del TPM (TPMxCNTH:TPMxCNTL)=== | ||

| + | |||

| + | |||

| + | Los registros TPMxCNTH y TPMxCNTL contienen el bit más significativo y menos significativo respectivamente del valor en el contador del TPM. Leer cualquiera de los valores en estos registros coloca los datos de ambos en un buffer hasta que se finalice esta operación. Estos registros se resetean apenas se resetee el Microcontrolador o se escriba en el registro TPMxSC. Como ambos son registros de solo lectura, apenas se intente escribir en alguno de ellos se reseteara el contador. | ||

| + | |||

| + | [[Archivo:Untitled8.jpg|700px|center|thumb|'''8 bits mas significativos del contador (TPMxCNTH)'''.]][[Archivo:Untitled8.jpg|700px|center|thumb|'''8 bits menos significativos del contador (TPMxCNTL)'''.]] | ||

| + | |||

| + | |||

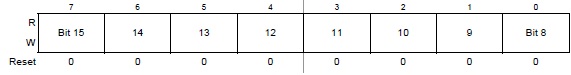

| + | ===Registros del modulo del contador del TPM (TPMxMODH:TPMxMODL)=== | ||

| + | |||

| + | El registro de módulo del TPM contiene el valor para el contador del TPM. Cuando este contador alcance el valor asignado en este registro se reinicia y coloca en uno la bandera de overflow para saber que termino un ciclo. Al escribir en los registros TPMxMODH o TPMxMODL, que representan los 16 bits del módulo, evita que ocurran interrupciones por overflow hasta que se termine de escribir, además de que guarda el valor de los registros en un buffer, y se actualizará dependiendo de los valores en CLKSB:CLKSA entonces: | ||

| + | *CLKSB y CLKSA son cero los registros se van a actualizar apenas se termine de escribir el segundo byte. | ||

| + | *CLKSB y CLKSA son diferentes de cero los registros se van a actualizar cuando se terminen de escribir en ambos. | ||

| + | |||

| + | |||

| + | Con respecto a esto último, es importante destacar que esta actualización se llevará a cabo únicamente cuando el contador cambia desde FFFE a FFFF, si este opera en modo normal (es decir, si cuenta en modo creciente). Para evitar que esto suceda, y que el módulo se actualice en el momento en que queramos sin depender del valor del contador, luego de actualizar el módulo se debe escribir en el registro TPMxSC. Por ello, al momento de configurar el TPM, es preferible primero escribir el valor del módulo, y luego las configuraciones deseadas en el TPMxSC. | ||

| + | |||

| + | |||

| + | Resetear el TPMxMOD coloca los 16 bits del módulo en cero. | ||

| + | |||

| + | [[Archivo:Untitled10.jpg|700px|center|thumb|'''8 bits mas significativos del registro de modulo (TPMxMODH)'''.]] | ||

| + | [[Archivo:Untitled11.jpg|700px|center|thumb|'''8 bits menos significativos del registro de modulo (TPMxMODL)'''.]] | ||

| + | |||

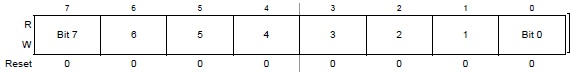

| + | ===Registros de status y control de los canales del TPM (TPMxCnSC)=== | ||

| + | |||

| + | Este registro contiene el bit para la bandera de interrupciones y los bits de control para configurar el modo de operacion del canal. | ||

| + | |||

| + | [[Archivo:Untitled12.jpg|700px|center|thumb|'''Registro de control y status del los canales''']] | ||

| + | |||

| + | *'''CHnF (Bit 7):''' Cuando el canal esta en el modo de captura de entrada, este bit se pondrá en uno cuando ocurra el flanco que se definió como flanco activo. Cuando el canal esta en comparación de salida, en alineación de flancos o alineación central de PWM, el bit CHnF se coloca en uno cuando el valor en el registro del contador es igual al valor en el registro del canal, siempre y cuando el duty cycle no sea ni cero ni cien porciento. La interrupción ocurrirá siempre y cuando este bit este en uno y que las interrupciones estén habilitadas, es decir que el bit CHnIE sea uno. Resetear coloca el bit CHnF en cero. | ||

| + | *'''CHnIE (Bit 6):''' Este bit habilita las interrupciones del canal especifico cuando esta en uno. Resetear modifica este bit y lo fuerza a cero. | ||

| + | *'''MSnB (Bit 5):''' Se conoce también como selección de modo A para los canales. Cuando CPWMS esta en cero y el bit MSnB esta en uno, configura el canal TPM especifico para alineación de flancos PWM. | ||

| + | *'''MSnA (Bit 4):''' Conocido también como modo de selección A para los canales. Cuando CPWMS y MSnB son cero, MSnA va a configurar el canal para capturador de entrada o comparador de salida. | ||

| + | *'''ELSnB:ELSnA (Bits 3 y 2):''' Con estos bits se configura, dependiendo de la configuración de CPWMS:MSnB:MSnA: | ||

| + | |||

| + | # La polaridad con la que se iniciara una captura | ||

| + | # El nivel de control para una comparación exitosa de salida | ||

| + | # La polaridad del módulo PWM | ||

| + | |||

| + | [[Archivo:Untitled13.jpg|700px|center|thumb|'''Selección del modo de operacion de los canales''']] | ||

| + | |||

| + | |||

| + | |||

| + | |||

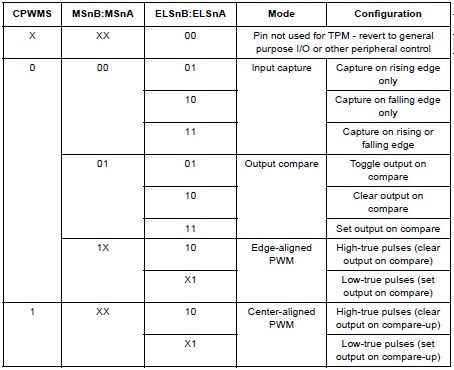

| + | ===Registros del valor de los canales del TPM (TPMxCnVH:TPMxCnVL)=== | ||

| + | |||

| + | Mientras el canal este en el modo de captura de entrada o en el modo de comparación de salidas, leer o escribir alguno de estos dos registros (TPMxCnVH o TPMxCnVL) respectivamente, pondrá los datos de ambos en un buffer hasta que se termine de ejecutar esta acción. Cuando esta en el modo de comparación de salidas, escribir en cualquiera de estos registros. En el caso de escritura ocurrirá y dependiendo de los valores en CLKSB y CLKSA ocurrirá lo siguiente: | ||

| + | *CLKSB y CLKSA son iguales a cero los registros se actualizarán cuando el segundo byte sea escrito. | ||

| + | *CLKSB y CLKSA son distintos de cero y esta en modo de comparación, los registros se actualizarán cuando el segundo byte se halla escrito y en el próximo cambio del contador. | ||

| + | *CLKSB y CLKSA son distintos de cero y este en el modo EPWM o CPWM, entonces los registros serán actualizados luego de que ambos bytes se escriban, y que el contador del TPM cambie. | ||

| + | |||

| + | [[Archivo:Untitled16.jpg|700px|center|thumb|'''Registro del valor del canal (8 bits mas significativos)'''.]] | ||

| + | [[Archivo:Untitled17.jpg|700px|center|thumb|'''Registro del valor del canal (8 bits menos significativos)'''.]] | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

==Reset== | ==Reset== | ||

| − | ==Interrupciones== | + | |

| + | El módulo TPM se resetea cuando ocurre cualquier Reset del Microcontrolador. Al resetear el microcontrolador el registro TPMxSC inhabilita los Clocks del TPM y la bandera de Overflow (TOIE). Además los bits CPWMS, MSnB, MSnA, ELSnB y ELSnA son todos forzados a cero, lo que configura todos los canales al modo de operación de captura de entrada. | ||

| + | |||

| + | |||

| + | ==Ejemplo en C de configuración del PWM== | ||

| + | |||

| + | |||

| + | <syntaxhighlight lang="c"> | ||

| + | #define PRESCALAR 7 | ||

| + | #define MODULO 32768 | ||

| + | #define DUTY75 (MODULO-(MODULO/4)) | ||

| + | #define DUTY25 (MODULO/4) | ||

| + | void main(){ | ||

| + | PTADD = 0; //Entradas | ||

| + | PTAPE=0x4; //Pullup | ||

| + | PTASE=0x4; //SmithTrigger | ||

| + | //inicializacion pwm | ||

| + | TPM1SC_CLKSA = 1; // Se elige como source del reloj para el TPM el "Bus Rate Clock" | ||

| + | TPM1SC_CLKSB = 0; | ||

| + | TPM1SC_PS = PRESCALAR; //y dividido entre 128 | ||

| + | TPM1MOD = MODULO; // Se guarda el valor del modulos para el contador | ||

| + | TPM1C0SC_MS0B = 1; // Se elige la modalidad "PWM edge aligned" | ||

| + | TPM1C0SC_ELS0A = 1; // Corresponde a la configuración de pulso "Low-True" | ||

| + | TPM1C0V = DUTY25; // Con esto obtendremos un duty cycle aprox del 25% | ||

| + | for(;;){ | ||

| + | if(PTAD_PTAD2==0){ | ||

| + | TPM1C0V = DUTY75; //Duty Cycle a 75% | ||

| + | }else TPM1C0V = DUTY25; //Duty Cycle a 25% | ||

| + | } | ||

| + | } | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ==[[Interrupciones]]== | ||

| + | |||

| + | El módulo tiene una interrupción opcional para el contador principal y un interruptor extra para cada canal. Lo que realizará la interrupción de los canales va a depender del modo de operación en el que este el canal. Si el canal esta configurado para recibir una entrada, la bandera de interrupción se coloca en uno cada vez que la entrada deseada es reconocida. Si el canal esta configurado para comparar la salida o para los modos de PWM, la bandera de interrupciones se coloca en uno cada vez que el valor del contador es igual al dato guardado en registro de valores. | ||

| + | |||

| + | Para cada interrupción del TPM, una bandera de un bit se coloca en uno para reconocer las condiciones de interrupción como Overflow, interrupción por captura de entradas o interrupción por comparación de salidas. Para poner este bit en cero hay que leer el registro que posee la bandera y escribir en ella un cero lógico. Si una nueva interrupción es detectada mientras se realizan estas operaciones, la secuencia se resetea y la bandera de interrupción permanece en uno después del paso de escritura para evitar que la interrupción nueva no se ejecute gracias a la anterior. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ===Interrupciones del tipo TOF (interrupción por bandera de overflow)=== | ||

| + | |||

| + | La operación que va a ocurrir por una interrupción del tipo TOF varía dependiendo del modo de operación en que se encuentre el canal TPM, sin embargo las variaciones son mínimas. | ||

| + | Para las interrupciones del tipo TOF normales ocurren apenas el contador cambia de 0xFFFF a 0x0000. Cuando el TPM no esta configurado para alineación central de PWM, la bandera se coloca en uno cuando el contador cambia del valor que esta en el registro de modulo a 0x0000. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ===Interrupciones de alineación central de PWM=== | ||

| + | |||

| + | Cuando CPWMS se coloca en uno, la bandera TOF se activa cada vez que el contador cambia de dirección, es decir que va de contar hacia arriba a contar hacia abajo. Para este caso en particular la bandera de este bit corresponde al final de cada período. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ===Interrupción del tipo de captura de entrada=== | ||

| + | |||

| + | Cuando un canal esta configurado en este modo y los bits de control ELSnB y ELSnA están en alguna de las 4 opciones (flanco de subida, flanco de bajada, cualquier flanco, o canal deshabilitado), cada vez que el flanco seleccionado sea reconocido, la bandera de interrupciones se fuerza en uno. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ===Interrupción del tipo de comparación de salida=== | ||

| + | |||

| + | Cuando un canal esta configurado en este Modo de Operación, la bandera de interrupciones se activa cada vez que el valor del contador es igual al valor que se encuentra guardado en el registro del canal. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ===Interrupcion por finalización de Duty Cycle=== | ||

| + | |||

| + | Para los canales que estén configurados para cualquier operación del tipo PWM existen dos posibilidades. Cuando el canal esta configurado para alineación de flancos, la bandera de interrupciones se coloca en uno cuando el valor del contador es igual al valor guardado en el registro del canal, esto marca la finalización del duty cycle. Cuando el canal esta configurado para alineación central, el contador va a ser igual al valor del registro del canal dos veces por cada periodo (uno cuando el Clock esta contando hacia arriba y otro cuando el Clock esta contando hacia abajo). Para este caso la bandera se coloca en uno al principio y al final del periodo del Duty Cycle. | ||

| + | |||

| + | ==Referencias== | ||

| + | |||

| + | *[http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf''MC9S08QE128RM Reference Manual''] | ||

| + | |||

| + | |||

| + | |||

| + | *[http://www.freescale.com/files/microcontrollers/doc/user_guide/DEMOQE128UM.pdf ''DEMOQE128 User Manual'' DEMOQE rev A] | ||

Revisión actual del 16:59 24 mar 2013

Contenido

- 1 Introducción

- 2 Registros del TPM

- 2.1 Registros de status y control del TPM (TPMxSC)

- 2.2 Registro de contadores del TPM (TPMxCNTH:TPMxCNTL)

- 2.3 Registros del modulo del contador del TPM (TPMxMODH:TPMxMODL)

- 2.4 Registros de status y control de los canales del TPM (TPMxCnSC)

- 2.5 Registros del valor de los canales del TPM (TPMxCnVH:TPMxCnVL)

- 3 Reset

- 4 Ejemplo en C de configuración del PWM

- 5 Interrupciones

- 6 Referencias

Introducción

Configuración

El comparador analógico (ACMP) puede ser configurado para conectarse el a un canal TPM de entrada, colocando el bit SOPT2 [ACICx] en uno. Haciendo esto, el pin del canal 0 del TPM no está disponible de forma externa, es decir no puede ser modificado. La salida del ACMP 1 puede conectarse a TPM1CH0 y la salida del ACMP2 puede conectarse a TPM2CH0.

Al momento de programar, el código para la configuración anterior sería de esta forma:

SOPT2=0x05

Donde el valor hexadecimal 0x05 representa los 8 bits del registro SOPT2 que, como se observa en el cuadro anterior, son 00000101.

Compuerta de clocks

Los clocks de los módulos TPM1, TPM2 y TPM3 pueden activarse o desactivarse usando el módulo SCGC1 [TPMx]. Cuando los bits están en 1, los puertos se habilitan dejando usar los clocks de cada módulo, y en cero se inhabilitan. Luego de un reset estos bits se colocan en 1.

Similar al caso anterior, el código para la configuración anteriormente descrita es:

SCGC1=0xE0

Nuevamente el valor hexadecimal 0xE0 representa los 8 bits del registro SCGC1, los cuales eran 11100000

Ademas del reloj interno el modulo permite seleccionar entre dehabilitar el temporizador, un reloj de oscilador de cristal o un reloj externo para ser el reloj que controla el pre-escalador y subsecuentemente el contador TPM de 16-bits.

Vector de interrupciones

A continuación se presentan los vectores de interrupciones para este módulo:

Características

El módulo PWM posee las siguientes características:

- Cada canal se puede configurarse para ser capturador de entrada, comparador de salidas, o alineación de flancos PWM. Estos tipos de configuración se discutirán en la sección de modos de operación.

- Escoger la polaridad en las salidas del PWM (positiva o negativa)

- El módulo puede ser configurado como buffer o como alineación central de la modulación del ancho de pulso (CPMW por sus siglas en inglés).

- El timer puede ser modificado para usarse con una escala predeterminada del bus clock, un clock fijo o un clock externo:

- La preescala se define dividiendo el clock del bus entre 1, 2, 4, 8, 16, 32, 64 o 128. El bus clock al que opera el microcontrolador es de 1MHz.

- El clock fijo es sincronizado con el bus clock mediante un circuito sincronizador.

- Para el clock externo, el pin puede compartirse con un pin de un canal o de cualquier otra entrada, por lo tanto hay que tener cuidado al configurar este pin.

- Un interruptor por canal y un contador para las interrupciones.

Modos de operación

Los canales pueden ser configurados independientemente como capturadores de entrada, comparador de salidas, o alineación de los flancos de PWM. Un bit de control puede modificarse para que todos los canales del módulo sean configurados como alineación de la modulación del ancho de pulso, si este es el caso se inhabilitan las otras opciones de configuración. Cuando el Microcontrolador esta en BDM background o BDM foreground, el TPM suspende las operaciones y las reanuda apenas el microcontrolador regresa a estado normal. Cuando esta en stop, todos los clocks del Microcontrolador se paran, incluyendo el oscilador principal, por lo tanto el modulo TPM es inhabilitado momentáneamente. En el modo de espera (wait mode), el TPM opera de forma normal ya que no genera una referencia a tiempo real ni el interrupt necesario para despertar el micro de este estado. Los modos de operación son los siguientes:

- Modo de captura de entrada: Cuando un evento preseleccionado de flanco ocurre en el pin asociado al canal que se esta usando, el valor actual del contador del timer de 16 bits es guardado en el registro de valor del canal y una bandera de interrupción se coloca en uno. Un flanco de subida, flanco de bajada, cualquier flanco o ningún flanco (canal inhabilitado) puede ser seleccionado como el flanco activo que dispara la captura de entrada.

- Modo de comparación de salida: Cuando el valor en el registro del contador es igual al valor del registro del canal, una bandera de un bit de interrupción se coloca en uno, y una acción de salida seleccionada es forzada en el pin del Microcontrolador. La salida que se ve en el pin puede ser forzada a cero, a uno, intercambiar/conmutar las salidas o simplemente ignorarlo.

- Modo de alineación de flancos de PWM: El valor del registro de 16 bits +1 define el período de la señal de salida del PWM. El valor del registro del canal define el duty cicle (tiempo en que la señal permanece en un estado activo) de la señal de salida del PWM. También se puede definir la polaridad de la señal de salida. Las interrupciones ocurren apenas termine el período de la señal, es decir en el punto de transición del duty cicle (cuando la señal pasa de activa a inactiva)

- Modo de alineacion central del PWM: El doble del valor del registro del modulo de 16 bits define el period de las salidas PWM, y los registros de valores de los canales definen la mitad de la duración del duty cycle. El contador del timer cuenta hasta que llega al valor del registro del modulo y luego cuenta desde este valor hasta cero. Mientras el contador esta contando hacia abajo, y el valor del contador es el mismo que el del modulo, la salida PWM se activa. En el caso contrario, es decir cuando esta contando hacia arriba y los valores coinciden, la salida PWM se desactiva.

Diagrama de bloques

El módulo TPM usa un pin de entrada/salida por canal (TPMxCHn), donde n representa el numero del canal. Hay que tener cuidado a usar estos pines ya que los pines de entrada/salida del TPM están asociados a los puertos de entrada/salida generales del microcontrolador. El componente central es el contador de 16 bits, el cual provee el tiempo de referencia para los modos de operación. Los registros del modulo del contador (TPMxMODH:TPMxMODL) registra el valor del modulo. Este dato se puede leer cuando sea, mas si se modifica este dato en la parte baja (TPMxMODL) o en la parte alta (TPMxMODH), se resetea el contador.

Registros del TPM

Registros de status y control del TPM (TPMxSC)

El registro TPMxSC contiene la bandera de overflow y los bits de control para determinar la habilitación de las interrupciones, el modo de operación que se va a usar, el tipo de clock y la escala en caso de ser necesaria.

- TOF (Bit 7): Este bit se conoce como la bandera de overflow del timer. Este bit se coloca en uno cuando el contador del TPM se resetea (0x0000) luego de haber alcanzado el valor guardado en el registro de modulo del contador. Para borrar este bit (ponerlo en cero), es necesario leer el registro TPMxSC cuando la bandera este en uno y escribir en este bit un cero. Si llegase a ocurrir otro overflow antes de colocar el bit 7 en cero, la secuencia se resetea por lo tanto la bandera quedaría en uno para que una interrupción del tipo TOF no se pierda debido a una anterior.

- TOIE (Bit 6): Tambien llamado habilitador de interrupciones de overflow del timer. Si este bit esta en uno se habilita la interrupción debido a overflows. Es decir que aunque el bit de la bandera de overflow este en uno, si este bit esta en cero nunca van a ocurrir interrupciones del tipo TOF.

- CPWMS (Bit 5): Si este bit esta en uno, se activa el modo de operación de alineación central de PWM para todos los canales, desactivando las demás opciones. Además configura el TPM para que el contador opere tanto hacia arriba como hacia abajo (up/down counting) en vez de solo hacia arriba. Un reset coloca este bit en cero habilitando los demás modos de operación.

- CLKS[B:A] (Bit 4:3): Estos dos bits se usan para definir que tipo de clock se va a utilizar. El clock fijo solo sirve cuando el clock del sistema esta basado en un sistema PLL (divisor del clock). En caso de no ser así el clock va a ser el mismo que el bus clock, 1MHz para este caso. La sincronización de un clock externo se genera mediante el modulo del bus clock del TPM, mientras que para el caso de un clock fijo es a través de un circuito sincronizador.

- PS[2:0] (Bit 2:0): Estos 3 bits se usan para modificar el clock del TPM escogiendo uno de los factores de división que se observan en la siguiente tabla.

Registro de contadores del TPM (TPMxCNTH:TPMxCNTL)

Los registros TPMxCNTH y TPMxCNTL contienen el bit más significativo y menos significativo respectivamente del valor en el contador del TPM. Leer cualquiera de los valores en estos registros coloca los datos de ambos en un buffer hasta que se finalice esta operación. Estos registros se resetean apenas se resetee el Microcontrolador o se escriba en el registro TPMxSC. Como ambos son registros de solo lectura, apenas se intente escribir en alguno de ellos se reseteara el contador.

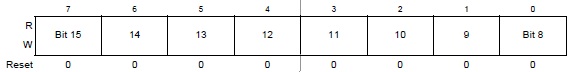

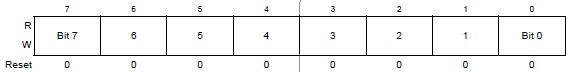

Registros del modulo del contador del TPM (TPMxMODH:TPMxMODL)

El registro de módulo del TPM contiene el valor para el contador del TPM. Cuando este contador alcance el valor asignado en este registro se reinicia y coloca en uno la bandera de overflow para saber que termino un ciclo. Al escribir en los registros TPMxMODH o TPMxMODL, que representan los 16 bits del módulo, evita que ocurran interrupciones por overflow hasta que se termine de escribir, además de que guarda el valor de los registros en un buffer, y se actualizará dependiendo de los valores en CLKSB:CLKSA entonces:

- CLKSB y CLKSA son cero los registros se van a actualizar apenas se termine de escribir el segundo byte.

- CLKSB y CLKSA son diferentes de cero los registros se van a actualizar cuando se terminen de escribir en ambos.

Con respecto a esto último, es importante destacar que esta actualización se llevará a cabo únicamente cuando el contador cambia desde FFFE a FFFF, si este opera en modo normal (es decir, si cuenta en modo creciente). Para evitar que esto suceda, y que el módulo se actualice en el momento en que queramos sin depender del valor del contador, luego de actualizar el módulo se debe escribir en el registro TPMxSC. Por ello, al momento de configurar el TPM, es preferible primero escribir el valor del módulo, y luego las configuraciones deseadas en el TPMxSC.

Resetear el TPMxMOD coloca los 16 bits del módulo en cero.

Registros de status y control de los canales del TPM (TPMxCnSC)

Este registro contiene el bit para la bandera de interrupciones y los bits de control para configurar el modo de operacion del canal.

- CHnF (Bit 7): Cuando el canal esta en el modo de captura de entrada, este bit se pondrá en uno cuando ocurra el flanco que se definió como flanco activo. Cuando el canal esta en comparación de salida, en alineación de flancos o alineación central de PWM, el bit CHnF se coloca en uno cuando el valor en el registro del contador es igual al valor en el registro del canal, siempre y cuando el duty cycle no sea ni cero ni cien porciento. La interrupción ocurrirá siempre y cuando este bit este en uno y que las interrupciones estén habilitadas, es decir que el bit CHnIE sea uno. Resetear coloca el bit CHnF en cero.

- CHnIE (Bit 6): Este bit habilita las interrupciones del canal especifico cuando esta en uno. Resetear modifica este bit y lo fuerza a cero.

- MSnB (Bit 5): Se conoce también como selección de modo A para los canales. Cuando CPWMS esta en cero y el bit MSnB esta en uno, configura el canal TPM especifico para alineación de flancos PWM.

- MSnA (Bit 4): Conocido también como modo de selección A para los canales. Cuando CPWMS y MSnB son cero, MSnA va a configurar el canal para capturador de entrada o comparador de salida.

- ELSnB:ELSnA (Bits 3 y 2): Con estos bits se configura, dependiendo de la configuración de CPWMS:MSnB:MSnA:

- La polaridad con la que se iniciara una captura

- El nivel de control para una comparación exitosa de salida

- La polaridad del módulo PWM

Registros del valor de los canales del TPM (TPMxCnVH:TPMxCnVL)

Mientras el canal este en el modo de captura de entrada o en el modo de comparación de salidas, leer o escribir alguno de estos dos registros (TPMxCnVH o TPMxCnVL) respectivamente, pondrá los datos de ambos en un buffer hasta que se termine de ejecutar esta acción. Cuando esta en el modo de comparación de salidas, escribir en cualquiera de estos registros. En el caso de escritura ocurrirá y dependiendo de los valores en CLKSB y CLKSA ocurrirá lo siguiente:

- CLKSB y CLKSA son iguales a cero los registros se actualizarán cuando el segundo byte sea escrito.

- CLKSB y CLKSA son distintos de cero y esta en modo de comparación, los registros se actualizarán cuando el segundo byte se halla escrito y en el próximo cambio del contador.

- CLKSB y CLKSA son distintos de cero y este en el modo EPWM o CPWM, entonces los registros serán actualizados luego de que ambos bytes se escriban, y que el contador del TPM cambie.

Reset

El módulo TPM se resetea cuando ocurre cualquier Reset del Microcontrolador. Al resetear el microcontrolador el registro TPMxSC inhabilita los Clocks del TPM y la bandera de Overflow (TOIE). Además los bits CPWMS, MSnB, MSnA, ELSnB y ELSnA son todos forzados a cero, lo que configura todos los canales al modo de operación de captura de entrada.

Ejemplo en C de configuración del PWM

#define PRESCALAR 7

#define MODULO 32768

#define DUTY75 (MODULO-(MODULO/4))

#define DUTY25 (MODULO/4)

void main(){

PTADD = 0; //Entradas

PTAPE=0x4; //Pullup

PTASE=0x4; //SmithTrigger

//inicializacion pwm

TPM1SC_CLKSA = 1; // Se elige como source del reloj para el TPM el "Bus Rate Clock"

TPM1SC_CLKSB = 0;

TPM1SC_PS = PRESCALAR; //y dividido entre 128

TPM1MOD = MODULO; // Se guarda el valor del modulos para el contador

TPM1C0SC_MS0B = 1; // Se elige la modalidad "PWM edge aligned"

TPM1C0SC_ELS0A = 1; // Corresponde a la configuración de pulso "Low-True"

TPM1C0V = DUTY25; // Con esto obtendremos un duty cycle aprox del 25%

for(;;){

if(PTAD_PTAD2==0){

TPM1C0V = DUTY75; //Duty Cycle a 75%

}else TPM1C0V = DUTY25; //Duty Cycle a 25%

}

}

Interrupciones

El módulo tiene una interrupción opcional para el contador principal y un interruptor extra para cada canal. Lo que realizará la interrupción de los canales va a depender del modo de operación en el que este el canal. Si el canal esta configurado para recibir una entrada, la bandera de interrupción se coloca en uno cada vez que la entrada deseada es reconocida. Si el canal esta configurado para comparar la salida o para los modos de PWM, la bandera de interrupciones se coloca en uno cada vez que el valor del contador es igual al dato guardado en registro de valores.

Para cada interrupción del TPM, una bandera de un bit se coloca en uno para reconocer las condiciones de interrupción como Overflow, interrupción por captura de entradas o interrupción por comparación de salidas. Para poner este bit en cero hay que leer el registro que posee la bandera y escribir en ella un cero lógico. Si una nueva interrupción es detectada mientras se realizan estas operaciones, la secuencia se resetea y la bandera de interrupción permanece en uno después del paso de escritura para evitar que la interrupción nueva no se ejecute gracias a la anterior.

Interrupciones del tipo TOF (interrupción por bandera de overflow)

La operación que va a ocurrir por una interrupción del tipo TOF varía dependiendo del modo de operación en que se encuentre el canal TPM, sin embargo las variaciones son mínimas. Para las interrupciones del tipo TOF normales ocurren apenas el contador cambia de 0xFFFF a 0x0000. Cuando el TPM no esta configurado para alineación central de PWM, la bandera se coloca en uno cuando el contador cambia del valor que esta en el registro de modulo a 0x0000.

Interrupciones de alineación central de PWM

Cuando CPWMS se coloca en uno, la bandera TOF se activa cada vez que el contador cambia de dirección, es decir que va de contar hacia arriba a contar hacia abajo. Para este caso en particular la bandera de este bit corresponde al final de cada período.

Interrupción del tipo de captura de entrada

Cuando un canal esta configurado en este modo y los bits de control ELSnB y ELSnA están en alguna de las 4 opciones (flanco de subida, flanco de bajada, cualquier flanco, o canal deshabilitado), cada vez que el flanco seleccionado sea reconocido, la bandera de interrupciones se fuerza en uno.

Interrupción del tipo de comparación de salida

Cuando un canal esta configurado en este Modo de Operación, la bandera de interrupciones se activa cada vez que el valor del contador es igual al valor que se encuentra guardado en el registro del canal.

Interrupcion por finalización de Duty Cycle

Para los canales que estén configurados para cualquier operación del tipo PWM existen dos posibilidades. Cuando el canal esta configurado para alineación de flancos, la bandera de interrupciones se coloca en uno cuando el valor del contador es igual al valor guardado en el registro del canal, esto marca la finalización del duty cycle. Cuando el canal esta configurado para alineación central, el contador va a ser igual al valor del registro del canal dos veces por cada periodo (uno cuando el Clock esta contando hacia arriba y otro cuando el Clock esta contando hacia abajo). Para este caso la bandera se coloca en uno al principio y al final del periodo del Duty Cycle.

Referencias

Contributors

AK, Dalak, Francjsalanova, Leofragachan, Minleung, Misato, Nivmizzet, Racuna, Vegabante