Diferencia entre revisiones de «Modos de operación del MC9S08QE128»

(→Dalida del modo Stop2) |

|||

| (No se muestran 5 ediciones intermedias de 4 usuarios) | |||

| Línea 1: | Línea 1: | ||

| − | Los modos en que se pone a trabajar un | + | |

| + | |||

| + | <div style="top:+0.3em; text-align: center;font-size:100%; border:1px solid #C7D0F8; background:#F2F5FD;width:80%"> | ||

| + | '''Este artículo está incompleto. Necesita trabajo adicional. Revisar la discusión.'''</div> | ||

| + | Los modos en que se pone a trabajar un Microcontrolador permiten hacer uso más adecuado del mismo, en la mayoría de los casos mejorando su rendimiento, consumo de energía y la velocidad en que opera. Estos modos de operación dan la posibilidad de hacer que el micro se mantenga realizando sólo las tareas que necesite ejecutar y que se olvide de las demás. De este forma al no estar realizando tareas innecesarias para su operación actual, el micro puede operar a mayor velocidad y se evita consumir un porcentaje de potencia. Un modo de operación siempre estará siendo ejecutado, sin que se lo ordenemos directamente al micro. Lo que los diferencia entre sí es el estado en que se colocan algunos parámetros como los antes mencionados (consumo y velocidad) y el uso de algunos periféricos si se trata de algún módulo de desarrollo, como el [[PE Micro: DEMOQE128]]. | ||

Los modos de operación difieren entre los microcontroladores incluso dentro de sus propias familias, por ello es recomendable consultar el datasheet del micro a utilizar. En el caso de la asignatura ''Arquitectura del Computador II'' se utilizará el MC9S08QE128, caracterizado por su bajo consumo de potencia y bajo costo. | Los modos de operación difieren entre los microcontroladores incluso dentro de sus propias familias, por ello es recomendable consultar el datasheet del micro a utilizar. En el caso de la asignatura ''Arquitectura del Computador II'' se utilizará el MC9S08QE128, caracterizado por su bajo consumo de potencia y bajo costo. | ||

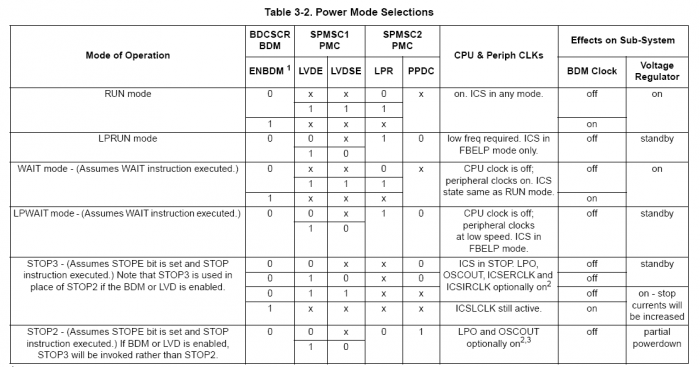

| − | [[Archivo:tabla 2.png|700px|thumb|right]] | + | [[Archivo:tabla 2.png|700px|thumb|right||Power Mode Selections.]] |

== Modo RUN == | == Modo RUN == | ||

| − | Es el modo más común de todos ya que en este se pueden correr los códigos que los usuarios deseen. Por defecto, al hacer un | + | Es el modo más común de todos ya que en este se pueden correr los códigos que los usuarios deseen. Por defecto, al hacer un Reset el CPU ejecuta el código presente en la posición 0xFFFE–0xFFFF de la memoria interna. En este modo de operación los periféricos y el procesador trabajan a velocidad normal ( 50 MHz CPU/25 MHz bus). Ver [[ ICS (Configuración Reloj Interno) - MC9S08QE128]]. |

| + | |||

La activación de este modo se hace habilitando el bit LPR (a 0) del registro SPMSC2 | La activación de este modo se hace habilitando el bit LPR (a 0) del registro SPMSC2 | ||

| Línea 13: | Línea 18: | ||

=== Low Power Run Mode (LPRun) === | === Low Power Run Mode (LPRun) === | ||

| − | Este modo se caracteriza por la puesta en | + | |

| + | Este modo se caracteriza por la puesta en Standby del voltaje del regulador, se lleva este valor al mínimo que aun permita que el CPU continúe funcionando de manera adecuada. El consumo de corriente es llevado al mínimo por lo que los relojes de los periféricos no utilizados quedan inhabilitados haciendo uso de los registros SCGC1 y SCGC2. La habilitación del modo es dada por el bit LPR (a 1) del SPMSC2 | ||

Antes de activar este modo se debe considerar lo siguiente: | Antes de activar este modo se debe considerar lo siguiente: | ||

| Línea 28: | Línea 34: | ||

==== Interrupciones en LPRun ==== | ==== Interrupciones en LPRun ==== | ||

| + | |||

El LPRun ofrece la opción de volver a la regulación completa si ocurre cualquier interrupción. Esto se hace configurando el bit de LPWUI en el registro SPMSC2. El ICS se puede ajustar entonces para permitir velocidad completen la rutina de servicio de interrupción. | El LPRun ofrece la opción de volver a la regulación completa si ocurre cualquier interrupción. Esto se hace configurando el bit de LPWUI en el registro SPMSC2. El ICS se puede ajustar entonces para permitir velocidad completen la rutina de servicio de interrupción. | ||

| + | |||

Si el bit LPWUI es cero, las interrupciones serán atendidos en LPRun. | Si el bit LPWUI es cero, las interrupciones serán atendidos en LPRun. | ||

Si el bit LPWUI esa 1, los bits LPR y LPRS se borrarán y las interrupciones serán atendidos con la regulación completa. | Si el bit LPWUI esa 1, los bits LPR y LPRS se borrarán y las interrupciones serán atendidos con la regulación completa. | ||

| Línea 39: | Línea 47: | ||

==== BDM in Low Power Run Mode ==== | ==== BDM in Low Power Run Mode ==== | ||

| − | No se puede introducir cuando el microcontrolador está en modo Background. Si se esta en modo LPRun el pin BKGD/MS provoca el cambio a | + | No se puede introducir cuando el microcontrolador está en modo Background. Si se esta en modo LPRun el pin BKGD/MS provoca el cambio a Modo RUN normal mediante un flanco de bajada en el reloj. |

==== BDM in Low Power Wait Mode ==== | ==== BDM in Low Power Wait Mode ==== | ||

| Línea 54: | Línea 62: | ||

#Cuando el pin BKGD / MS es 0 durante POR | #Cuando el pin BKGD / MS es 0 durante POR | ||

| − | #Cuando el BKGD/MS es 0 inmediatamente después de emitir una | + | #Cuando el BKGD/MS es 0 inmediatamente después de emitir una Depuración. |

#Cuando un comando de BACKGROUND es recibido a través de la BKGD/MS. | #Cuando un comando de BACKGROUND es recibido a través de la BKGD/MS. | ||

#Cuando una instrucción BGND es ejecutada. | #Cuando una instrucción BGND es ejecutada. | ||

| − | #Cuando se enfrentan a un punto de rupturan en BDC | + | #Cuando se enfrentan a un punto de rupturan en BDC. |

| − | #Cuando se enfrentan a un punto de ruptura en DBG | + | #Cuando se enfrentan a un punto de ruptura en DBG (Ver:[[Debug Module (DBG)(128k)- MC9S08QE128]]) |

La activación del BGD se utilizan para programar bootloader (programa de arranque) o programa de aplicación de usuario en la memoria flash. | La activación del BGD se utilizan para programar bootloader (programa de arranque) o programa de aplicación de usuario en la memoria flash. | ||

| − | Al hacer esta | + | Al hacer esta activación del modo BGD, el CPU queda en modo espera de los comandos BACKGROUND en lugar de ejecutar las instrucciones del programa de aplicación del usuario. |

Hay dos tipos de comandos BACKGROUNDS: | Hay dos tipos de comandos BACKGROUNDS: | ||

| − | # | + | #No intrusivos, que se refieren a que se pueden ejecutar comandos al mismo tiempo que se ejecuta un programa del usuario. |

#Los comandos que pueden ser ejecutados solo cuando se está en modo BGD. Por ejemplo, la lectura y escritura de registros. | #Los comandos que pueden ser ejecutados solo cuando se está en modo BGD. Por ejemplo, la lectura y escritura de registros. | ||

== Modo Wait == | == Modo Wait == | ||

| + | |||

| + | |||

Este modo se introduce mediante la ejecución de una instrucción WAIT. Tras la ejecución de la instrucción, la CPU pasa a un estado de baja potencia en los que no está sincronizado con el reloj. En este modo se permiten las interrupciones. De hecho cuando se produce una petición de interrupción, las salidas de la CPU activa el modo Wait y reanuda el procesamiento, a partir de las operaciones de apilamiento que conduce a la rutina de servicio de interrupción. | Este modo se introduce mediante la ejecución de una instrucción WAIT. Tras la ejecución de la instrucción, la CPU pasa a un estado de baja potencia en los que no está sincronizado con el reloj. En este modo se permiten las interrupciones. De hecho cuando se produce una petición de interrupción, las salidas de la CPU activa el modo Wait y reanuda el procesamiento, a partir de las operaciones de apilamiento que conduce a la rutina de servicio de interrupción. | ||

AL estar activo el modo Wait sólo el commando BACKGROUND y el "memory-access-with-status" están disponibles. No se permite el acceso de memoria, pero se informará de un error que indica que el MCU está en Stop o modo Wait. El comando BACKGROUND se puede utilizar para activar el modo Wait de MCU. | AL estar activo el modo Wait sólo el commando BACKGROUND y el "memory-access-with-status" están disponibles. No se permite el acceso de memoria, pero se informará de un error que indica que el MCU está en Stop o modo Wait. El comando BACKGROUND se puede utilizar para activar el modo Wait de MCU. | ||

| + | |||

=== Low Power Wait Mode (LPWait) === | === Low Power Wait Mode (LPWait) === | ||

| + | |||

| + | |||

La diferencia respecto al modo normal de WAIT es que el regulador de la CPU sale de regulación y queda en estado de standby. Lo anterior reduce enormemente el consumo de la máquina, consumo que puede ser reducido aún más deshabilitando los módulos que no se utilicen. Esta última operación se puede lograr poniendo a cero los bits de los módulos a inactivar en el registro SCGC. | La diferencia respecto al modo normal de WAIT es que el regulador de la CPU sale de regulación y queda en estado de standby. Lo anterior reduce enormemente el consumo de la máquina, consumo que puede ser reducido aún más deshabilitando los módulos que no se utilicen. Esta última operación se puede lograr poniendo a cero los bits de los módulos a inactivar en el registro SCGC. | ||

| Línea 79: | Línea 92: | ||

==== Interrupts in Low Power Wait Mode ==== | ==== Interrupts in Low Power Wait Mode ==== | ||

| + | |||

| + | |||

Si el bit LPWUI se pone en 1 cuando la instrucción Wait se ejecuta, el regulador volverá a estar a plenitud cuando se sale del modo Wait. El ICS se puede ajustar inmediatamente en la rutina de servicio de interrupción. | Si el bit LPWUI se pone en 1 cuando la instrucción Wait se ejecuta, el regulador volverá a estar a plenitud cuando se sale del modo Wait. El ICS se puede ajustar inmediatamente en la rutina de servicio de interrupción. | ||

| Línea 86: | Línea 101: | ||

==== Resets en Low Power Wait Mode ==== | ==== Resets en Low Power Wait Mode ==== | ||

| + | |||

| + | |||

Cualquier reset hará salirse del modo LPW. | Cualquier reset hará salirse del modo LPW. | ||

== Modos Stop == | == Modos Stop == | ||

| − | |||

| + | |||

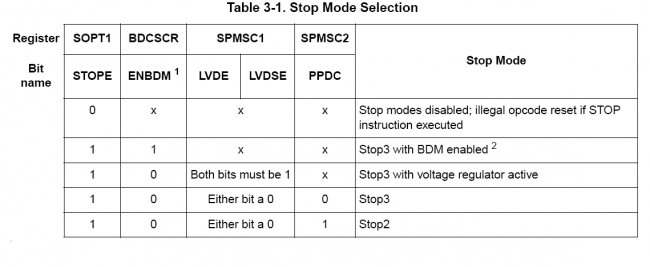

| + | Cuando se tiene el modo Stop los relojes del CPU y del Bus se suspenden, lo que varía es el valor del regulador. Los modos Stop se seleccionan ajustando los bits apropiados del registro SCGC1. | ||

| Línea 101: | Línea 119: | ||

=== Modo Stop2 === | === Modo Stop2 === | ||

| − | [[Archivo:tabla 3.png|650px|thumb|center]] | + | |

| + | |||

| + | |||

| + | [[Archivo:tabla 3.png|650px|thumb|center||Stop Mode Selection.]] | ||

| + | |||

==== Salida del modo Stop2 ==== | ==== Salida del modo Stop2 ==== | ||

| Línea 122: | Línea 144: | ||

Para salir del modo STOP4 es necesario que se produzca un evento de RESET o alguna de las siguientes excepciones de interrupción: la [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#RTC: RTC]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#LVD: LVD]], LVW, [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#ADC: ADC]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#ACMPx: ACMP]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#IRQ: IRQ]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#SCI_-_TX: SCI]], o la[[http://wikitronica.labc.usb.ve/index.php/Interrupciones#KBIx: KBI]]. | Para salir del modo STOP4 es necesario que se produzca un evento de RESET o alguna de las siguientes excepciones de interrupción: la [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#RTC: RTC]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#LVD: LVD]], LVW, [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#ADC: ADC]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#ACMPx: ACMP]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#IRQ: IRQ]], [[http://wikitronica.labc.usb.ve/index.php/Interrupciones#SCI_-_TX: SCI]], o la[[http://wikitronica.labc.usb.ve/index.php/Interrupciones#KBIx: KBI]]. | ||

| − | [ | + | |

| + | ==Referencias== | ||

| + | |||

| + | [http://www.freescale.com/files/microcontrollers/doc/ref_manual/MC9S08QE128RM.pdf MC9S08QE128RM] | ||

| + | |||

| + | [[Categoría: MC9S08QE128]] | ||

Revisión actual del 20:41 17 mar 2013

Los modos en que se pone a trabajar un Microcontrolador permiten hacer uso más adecuado del mismo, en la mayoría de los casos mejorando su rendimiento, consumo de energía y la velocidad en que opera. Estos modos de operación dan la posibilidad de hacer que el micro se mantenga realizando sólo las tareas que necesite ejecutar y que se olvide de las demás. De este forma al no estar realizando tareas innecesarias para su operación actual, el micro puede operar a mayor velocidad y se evita consumir un porcentaje de potencia. Un modo de operación siempre estará siendo ejecutado, sin que se lo ordenemos directamente al micro. Lo que los diferencia entre sí es el estado en que se colocan algunos parámetros como los antes mencionados (consumo y velocidad) y el uso de algunos periféricos si se trata de algún módulo de desarrollo, como el PE Micro: DEMOQE128.

Los modos de operación difieren entre los microcontroladores incluso dentro de sus propias familias, por ello es recomendable consultar el datasheet del micro a utilizar. En el caso de la asignatura Arquitectura del Computador II se utilizará el MC9S08QE128, caracterizado por su bajo consumo de potencia y bajo costo.

Modo RUN

Es el modo más común de todos ya que en este se pueden correr los códigos que los usuarios deseen. Por defecto, al hacer un Reset el CPU ejecuta el código presente en la posición 0xFFFE–0xFFFF de la memoria interna. En este modo de operación los periféricos y el procesador trabajan a velocidad normal ( 50 MHz CPU/25 MHz bus). Ver ICS (Configuración Reloj Interno) - MC9S08QE128.

La activación de este modo se hace habilitando el bit LPR (a 0) del registro SPMSC2

Low Power Run Mode (LPRun)

Este modo se caracteriza por la puesta en Standby del voltaje del regulador, se lleva este valor al mínimo que aun permita que el CPU continúe funcionando de manera adecuada. El consumo de corriente es llevado al mínimo por lo que los relojes de los periféricos no utilizados quedan inhabilitados haciendo uso de los registros SCGC1 y SCGC2. La habilitación del modo es dada por el bit LPR (a 1) del SPMSC2

Antes de activar este modo se debe considerar lo siguiente:

- El ICS debe estar en modo FBELP. Ver ICS (Configuración Reloj Interno) - MC9S08QE128.

- El bit HGO en el registro ICSC2 debe ser 0 para configurar un oscilador externo de bajo consumo.

- La frecuencia máxima del bus debe ser 125Khz.

- Si el ADC está activado debe estar configurado para utilizar la fuente de reloj asíncrono, ADACK.

- El bit LVDE o LVDSE en el registro SPMSC1 debe ser 0.

- no borrar o programar la memoria flash.

- el micro no puede estar en modo "background".

- El módulo de detección de bajo voltaje deberá ser deshabilitado, debido a la condición de standby del regulador interno.

Interrupciones en LPRun

El LPRun ofrece la opción de volver a la regulación completa si ocurre cualquier interrupción. Esto se hace configurando el bit de LPWUI en el registro SPMSC2. El ICS se puede ajustar entonces para permitir velocidad completen la rutina de servicio de interrupción.

Si el bit LPWUI es cero, las interrupciones serán atendidos en LPRun. Si el bit LPWUI esa 1, los bits LPR y LPRS se borrarán y las interrupciones serán atendidos con la regulación completa.

Resets in Low Power Run Mode

Cualquier reset hará salirse del modo LPRun. Se deben poner en 0 los bits LPR y LPRS y devolver el dispositivo a modo RUN normal.

BDM in Low Power Run Mode

No se puede introducir cuando el microcontrolador está en modo Background. Si se esta en modo LPRun el pin BKGD/MS provoca el cambio a Modo RUN normal mediante un flanco de bajada en el reloj.

BDM in Low Power Wait Mode

Ocurre lo mismo que para el caso anterior. El dispositivo no puede operar bajo LPWM y lleva al micro al modo RUN normal de la misma forma arriba descrita

Active Background Mode

La activación de las funciones del modo BGD se gestionan a través del controlador de depuración de fondo (BDC).

Existen varias formas de activar este modo:

- Cuando el pin BKGD / MS es 0 durante POR

- Cuando el BKGD/MS es 0 inmediatamente después de emitir una Depuración.

- Cuando un comando de BACKGROUND es recibido a través de la BKGD/MS.

- Cuando una instrucción BGND es ejecutada.

- Cuando se enfrentan a un punto de rupturan en BDC.

- Cuando se enfrentan a un punto de ruptura en DBG (Ver:Debug Module (DBG)(128k)- MC9S08QE128)

La activación del BGD se utilizan para programar bootloader (programa de arranque) o programa de aplicación de usuario en la memoria flash.

Al hacer esta activación del modo BGD, el CPU queda en modo espera de los comandos BACKGROUND en lugar de ejecutar las instrucciones del programa de aplicación del usuario.

Hay dos tipos de comandos BACKGROUNDS:

- No intrusivos, que se refieren a que se pueden ejecutar comandos al mismo tiempo que se ejecuta un programa del usuario.

- Los comandos que pueden ser ejecutados solo cuando se está en modo BGD. Por ejemplo, la lectura y escritura de registros.

Modo Wait

Este modo se introduce mediante la ejecución de una instrucción WAIT. Tras la ejecución de la instrucción, la CPU pasa a un estado de baja potencia en los que no está sincronizado con el reloj. En este modo se permiten las interrupciones. De hecho cuando se produce una petición de interrupción, las salidas de la CPU activa el modo Wait y reanuda el procesamiento, a partir de las operaciones de apilamiento que conduce a la rutina de servicio de interrupción.

AL estar activo el modo Wait sólo el commando BACKGROUND y el "memory-access-with-status" están disponibles. No se permite el acceso de memoria, pero se informará de un error que indica que el MCU está en Stop o modo Wait. El comando BACKGROUND se puede utilizar para activar el modo Wait de MCU.

Low Power Wait Mode (LPWait)

La diferencia respecto al modo normal de WAIT es que el regulador de la CPU sale de regulación y queda en estado de standby. Lo anterior reduce enormemente el consumo de la máquina, consumo que puede ser reducido aún más deshabilitando los módulos que no se utilicen. Esta última operación se puede lograr poniendo a cero los bits de los módulos a inactivar en el registro SCGC.

Las restricciones vistas en el modo LPRUN se aplican al modo LPWAIT.

Interrupts in Low Power Wait Mode

Si el bit LPWUI se pone en 1 cuando la instrucción Wait se ejecuta, el regulador volverá a estar a plenitud cuando se sale del modo Wait. El ICS se puede ajustar inmediatamente en la rutina de servicio de interrupción.

Si el bit LPWUI está en cero durante la instrucción Wait, se ejecuta una interrupción para devolver el dispositivo a modo LPRun.

Si el bit LPWUI esta en 1 durante la instrucción Wait, se ejecuta una interrupción que devuelve el dispositivo al modo RUN normal con una regulación completa y los bits LPR y LPRs se pondrán a cero.

Resets en Low Power Wait Mode

Cualquier reset hará salirse del modo LPW.

Modos Stop

Cuando se tiene el modo Stop los relojes del CPU y del Bus se suspenden, lo que varía es el valor del regulador. Los modos Stop se seleccionan ajustando los bits apropiados del registro SCGC1.

Existen tres modos de operación en STOP, siempre y cuando el bit STOPE del registro SOPT1 se encuentre en “1”. El bit WAITE del registro SOPT1 deberá ser aclarado, excepto cuando se desee trabajar en modo WAIT. En el modo STOP3 las fuentes de reloj de la CPU son interrumpidas. Los diferentes modos de STOP son seleccionados mediante el bit PPDC del registro SPMSC2. La mayoría de los comandos del modo background (BDM) no son reconocidos en los modos de STOP, pero el comando BACKGROUND puede sacar la CPU del modo STOP4 y entrar en modo HALT. Quedando la CPU en el modo HALT y estando el bit ENBDM en “1”, todos los comandos del BDM se podrán utilizar.

Punto importante: Si el CPU no está habilitada para el modo WAIT ni para el modo STOP y se presenta una ejecución de instrucción STOP, la CPU inicia un evento de RESET por ILLEGAL OPCODE si el bit IRD del registro CPUCR se encuentra en estado “0” o un proceso de excepción por ILLEGAL OPCODE si el bit IRD del registro CPUCR se encuentra en estado “1”.

Modo Stop2

Salida del modo Stop2

Para salir de este modo, es necesario introducir un flanco de bajada en el pin de RESET del sistema o generar un evento de excepción por interrupción en el módulo [RTC], siempre y cuando esté habilitado.

La salida del modo Stop2 se realiza mediante la de activación de (PTA5/IRQ/TCLK/RESET) en la MCU.

Stop3 Mode

Se caracteriza porque los estados de todos los registros internos y la lógica, contenido de la RAM y E / S de los estados pin se mantienen.

Stop3 se puede salir al afirmar RESET, o por una interrupción de una de las siguientes fuentes: la [RTC], [LVD], LVW, [ADC], [ACMP], [IRQ], [SCI], o la [KBI].

Si Stop3 se sale por medio del pasador de RESET, entonces la MCU se restablece y la operación se reanudará después de tomar el vector de reset.

Modo Stop4

A diferencia de los modos STOP2 y STOP3, en este modo el regulador trabaja a plena regulación. Este modo es también llamado modo HALT y está relacionado directamente con la entrada a modo BDM desde STOP o por un evento de LVD desde STOP.

Para salir del modo STOP4 es necesario que se produzca un evento de RESET o alguna de las siguientes excepciones de interrupción: la [RTC], [LVD], LVW, [ADC], [ACMP], [IRQ], [SCI], o la[KBI].