Diferencia entre revisiones de «Debug Module (DBG)(128k)- MC9S08QE128»

| Línea 90: | Línea 90: | ||

==Mapa de Memoria== | ==Mapa de Memoria== | ||

| − | + | ||

| − | La siguiente tabla muestra detalladamente los registros de los cuales dispone el módulo y de los cuales puede disponer el usuario final. Además se indica el área de memoria al cual corresponden y el tipo de acceso a los mismos. | + | La siguiente tabla muestra detalladamente los registros de los cuales dispone el módulo y de los cuales puede disponer el usuario final. Además se indica el área de memoria al cual corresponden y el tipo de acceso a los mismos.<br> |

{| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F0" cellpadding="6" | {| border="2" style="padding: 0.5em; border: 1px #aaa solid; border-collapse: collapse;background:#F9F9F0" cellpadding="6" | ||

| Línea 102: | Línea 102: | ||

|align="center"|Base + $0000 | |align="center"|Base + $0000 | ||

|align="center"|Comparador A (Parte Alta DBGCAH) | |align="center"|Comparador A (Parte Alta DBGCAH) | ||

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $0001 | |align="center"|Base + $0001 | ||

|align="center"|Comparador A (Parte Baja DBGCAL) | |align="center"|Comparador A (Parte Baja DBGCAL) | ||

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $0002 | |align="center"|Base + $0002 | ||

|align="center"|Comparador B (Parte Alta DBGCBH) | |align="center"|Comparador B (Parte Alta DBGCBH) | ||

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $0003 | |align="center"|Base + $0003 | ||

| Línea 118: | Línea 118: | ||

|align="center"|Base + $0004 | |align="center"|Base + $0004 | ||

|align="center"|Comparador C (Parte Alta DBGCCH) | |align="center"|Comparador C (Parte Alta DBGCCH) | ||

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $0005 | |align="center"|Base + $0005 | ||

|align="center"|Comparador C (Parte Baja DBGCCL) | |align="center"|Comparador C (Parte Baja DBGCCL) | ||

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $0006 | |align="center"|Base + $0006 | ||

|align="center"|Registro FIFO (Parte Alta DBGFH) | |align="center"|Registro FIFO (Parte Alta DBGFH) | ||

| − | |align="center"| | + | |align="center"|Solo Lectura |

|- | |- | ||

|align="center"|Base + $0007 | |align="center"|Base + $0007 | ||

| − | |align="center"| | + | |align="center"|Registro FIFO (Parte Baja DBGFL) |

| − | |align="center"| | + | |align="center"|Solo Lectura |

|- | |- | ||

|align="center"|Base + $0008 | |align="center"|Base + $0008 | ||

| − | |align="center"| | + | |align="center"|Registro de Extensión Comparador A (DBGCAX) |

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $0009 | |align="center"|Base + $0009 | ||

| − | |align="center"| | + | |align="center"|Registro de Extensión Comparador B (DBGCBX) |

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $000A | |align="center"|Base + $000A | ||

| − | |align="center"| | + | |align="center"|Registro de Extensión Comparador C (DBGCCX) |

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $000B | |align="center"|Base + $000B | ||

| − | |align="center"| | + | |align="center"|Registro de Información Extendida FIFO (DBGCFX) |

| − | |align="center"| | + | |align="center"|Solo Lectura |

|- | |- | ||

|align="center"|Base + $000C | |align="center"|Base + $000C | ||

| − | |align="center"| | + | |align="center"|Registro de Control (DBGC) |

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $000D | |align="center"|Base + $000D | ||

| − | |align="center"| | + | |align="center"|Registro de Disparador (Trigger -DBGT-) |

| − | |align="center"| | + | |align="center"|Lectura/Escritura |

|- | |- | ||

|align="center"|Base + $000E | |align="center"|Base + $000E | ||

| − | |align="center"| | + | |align="center"|Registro de Estado (DBGS) |

| − | |align="center"| | + | |align="center"|Solo Lectura |

|- | |- | ||

|align="center"|Base + $000F | |align="center"|Base + $000F | ||

| − | |align="center"| | + | |align="center"|Registro de Conteo FIFO (DBGCNT) |

| − | |align="center"| | + | |align="center"|Solo Lectura |

|} | |} | ||

==Registros== | ==Registros== | ||

En construcción... | En construcción... | ||

Revisión del 21:31 15 nov 2012

Contenido

Módulo de Debug (DBG):

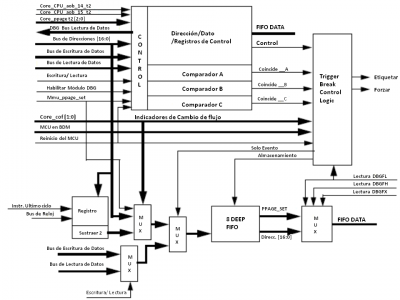

El Módulo de Depuración o ‘Debug Module’ DBG forma parte del desarrollo de sistemas de apoyo del microcontrolador. Si bien el control de depuración de respaldo ‘Background Debug Controller’ (BDC) es la interfaz de depuración primaria del MC9S08QE128, el módulo en circuito DBG opera de manera análoga a éste: es no intrusivo, permite el acceso a los datos de la memoria y mantiene las características tradicionales de depuración como modificar el registro de la CPU, puntos de interrupción, y traza de una sola instrucción.

El módulo DBG, proporciona una interfaz para activar y capturar de forma selectiva, la información del bus. De este modo, implementando un sistema externo se puede reconstruir lo que ocurre en la MCU ciclo a ciclo, sin necesidad de acceder externamente a las direcciones ni datos.

Conceptos

La palabra Debug en el área de programación se refiere a la identificación, eliminación y corrección de fallos o errores en el programa.(2*).

Por tanto al referirse a un Bug dentro del programa, se habla de errores menores o graves que afectan al sistema y la programación y afecta su efectividad y calidad.

Características Generales

El DBG emplea un chip para la emulación en circuito (ICE) con las siguientes características:

| Nº | Característica principal | Descripción |

|---|---|---|

| 1 | Tres comparadores A,B y C con la posibilidad de señalar direcciones en hasta 128 Kbytes de espacio de memoria |

|

| 2 | Nueve modos de disparo o activación (triggers) |

|

| 3 | Organización de la data según FIFO (first in, first out)para almacenamiento de la información del cambio de flujo de data y/o eventos |

|

| 4 | Capacidad de comenzar rastreo desde el reinicio o terminar el rastreo hasta el reinicio |

|

| 5 | Etiqueta y forza puntos de parada (Breakpoints) | --- |

| 6 | No posee, ni depende de los siguientes items: |

|

Ventajas del DBG

¿Para qué se implementa el DBG?

¡Fácil! Permite poder programar el seguimiento e identificación de errores de mi sistema en tiempo real. Representa una medida de prevención de errores cuando se trata de sistemas o programas complejos y extensos. También permite conocer el estado de los resgistros y datos, los cuales soporta hasta 128KBytes en espacio de memoria.El Módulo de Debug opera de modo no intrusivo con un solo pin, no compromete grandes gastos de potencia ni recursos de hardware. Además ofrece múltiples posibilidades de aplicación de 'BREAK POINTS' (puntos de parada o de prueba): por Posición de PC, por Condicionales (A=B, A>B,A<B, entre otros.), lo cual permitirá la identificación de errores en las áreas del sistema de programa deseadas.

En conjunto con el BDM representa una herramienta para asegurar la calidad del programa.

Modos de Operación

EL modulo DBG puede ser habilitado en todos los modos funcionales del MCU. Es deshabilitado si el MCU es asegurado y los comparadores son deshabilitados cuando se ejecuta el comando para modo BDM.

El bus de reloj al DBG puede abrirse o cerrarse usando el bit SCGC2 del DBG. Este bit es puesto en alta (1) luego de cada reinicio, lo cual habilita el bus. Y en caso de que no se requiera el uso del módulo y para conservar la energía, este bit es puesto en nivel bajo (0).

Mapa de Memoria

La siguiente tabla muestra detalladamente los registros de los cuales dispone el módulo y de los cuales puede disponer el usuario final. Además se indica el área de memoria al cual corresponden y el tipo de acceso a los mismos.

| Dirección | Uso | Acceso |

|---|---|---|

| Base + $0000 | Comparador A (Parte Alta DBGCAH) | Lectura/Escritura |

| Base + $0001 | Comparador A (Parte Baja DBGCAL) | Lectura/Escritura |

| Base + $0002 | Comparador B (Parte Alta DBGCBH) | Lectura/Escritura |

| Base + $0003 | Comparador B (Parte Baja DBGCBL) | 256 |

| Base + $0004 | Comparador C (Parte Alta DBGCCH) | Lectura/Escritura |

| Base + $0005 | Comparador C (Parte Baja DBGCCL) | Lectura/Escritura |

| Base + $0006 | Registro FIFO (Parte Alta DBGFH) | Solo Lectura |

| Base + $0007 | Registro FIFO (Parte Baja DBGFL) | Solo Lectura |

| Base + $0008 | Registro de Extensión Comparador A (DBGCAX) | Lectura/Escritura |

| Base + $0009 | Registro de Extensión Comparador B (DBGCBX) | Lectura/Escritura |

| Base + $000A | Registro de Extensión Comparador C (DBGCCX) | Lectura/Escritura |

| Base + $000B | Registro de Información Extendida FIFO (DBGCFX) | Solo Lectura |

| Base + $000C | Registro de Control (DBGC) | Lectura/Escritura |

| Base + $000D | Registro de Disparador (Trigger -DBGT-) | Lectura/Escritura |

| Base + $000E | Registro de Estado (DBGS) | Solo Lectura |

| Base + $000F | Registro de Conteo FIFO (DBGCNT) | Solo Lectura |

Registros

En construcción...Contributors

Any Isabel Rodriguez, Jesus Grimón, LitzaPinto, Minleung, Misato